隨著半導(dǎo)體產(chǎn)業(yè)快速發(fā)展,人工智能加速推動(dòng)對(duì)高性能計(jì)算的需求,Cadence 將自己定位為仿真和設(shè)計(jì)自動(dòng)化領(lǐng)域的行業(yè)先鋒。在于圣克拉拉會(huì)議中心舉行的 DesignCon 2025 大會(huì)上,Cadence 產(chǎn)品管理總監(jiān) Brad Griffin 分享了公司在信號(hào)完整性、電源完整性、熱仿真和電磁分析方面的最新進(jìn)展,這些技術(shù)正是行業(yè)向異構(gòu)集成和芯粒架構(gòu)轉(zhuǎn)型的關(guān)鍵驅(qū)動(dòng)力。

“這標(biāo)志著 Cadence 在 DesignCon 大會(huì)上的一個(gè)新起點(diǎn)。”Griffin 表示。“我們已連續(xù)參會(huì) 20 余年,雖然印刷電路板仍然很重要,但行業(yè)格局已發(fā)生變化——過去分布在電路板上的器件,如今被集成至單一封裝中。”

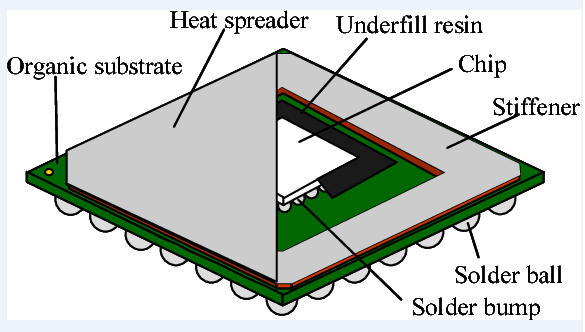

通用芯粒互聯(lián)技術(shù) (UCIe) 標(biāo)準(zhǔn)和高帶寬存儲(chǔ)器 (HBM) 接口極大推動(dòng)了這一轉(zhuǎn)變,大幅增加了設(shè)計(jì)復(fù)雜性、數(shù)據(jù)規(guī)模和仿真要求。隨著 AI 芯片在硅基板或有機(jī)基板上集成多個(gè)芯粒,傳統(tǒng)仿真流程已難以滿足新興架構(gòu)的需求。

應(yīng)對(duì)異構(gòu)集成的復(fù)雜性

隨著系統(tǒng)架構(gòu)從單裸片架構(gòu)轉(zhuǎn)向多裸片架構(gòu),Cadence 專注于開發(fā)新工具,以應(yīng)對(duì)裸片間通信數(shù)據(jù)的指數(shù)級(jí)增長(zhǎng)。“先進(jìn)封裝內(nèi)的幾何尺寸遠(yuǎn)遠(yuǎn)小于印刷電路板上的幾何尺寸,這導(dǎo)致我們的設(shè)計(jì)數(shù)據(jù)庫(kù)規(guī)模呈爆炸式增長(zhǎng)。”Griffin 解釋道。

其中一項(xiàng)關(guān)鍵挑戰(zhàn)是如何確保芯粒之間的無(wú)縫通信。目前,UCIe 標(biāo)準(zhǔn)已廣泛應(yīng)用于裸片間互連,但隨之而來(lái)的信號(hào)完整性和電源完整性問題,需要依賴先進(jìn)的仿真工作流程來(lái)解決。與此同時(shí),HBM 接口通過堆疊內(nèi)存裸片來(lái)實(shí)現(xiàn)高速性能,但會(huì)生成大量數(shù)據(jù),這些數(shù)據(jù)必須在制造前通過仿真進(jìn)行驗(yàn)證。

“Cadence 已將仿真工具直接集成至我們的設(shè)計(jì)平臺(tái),”Griffin 表示,“如果等到設(shè)計(jì)過程結(jié)束才進(jìn)行仿真,可能為時(shí)已晚。通過在設(shè)計(jì)過程中進(jìn)行實(shí)時(shí)、選擇性仿真,我們可以幫助工程師實(shí)現(xiàn)設(shè)計(jì)“左移”,通過設(shè)計(jì)同步分析,提前發(fā)現(xiàn)并解決問題,減少設(shè)計(jì)迭代次數(shù),加快產(chǎn)品上市時(shí)間。”

仿真可擴(kuò)展性:實(shí)現(xiàn) AI 芯片設(shè)計(jì)

Cadence 的一項(xiàng)主要?jiǎng)?chuàng)新是具有高效的多核擴(kuò)展能力,可大大縮短計(jì)算時(shí)間。這對(duì)于具有多個(gè) HBM 接口(有時(shí)單一設(shè)計(jì)中有多達(dá) 12 個(gè)接口)的 AI 芯片尤為重要,因?yàn)?AI 芯片設(shè)計(jì)流程涉及龐大的仿真工作量。

“過去,工程師必須導(dǎo)出可能高達(dá) 500GB 的設(shè)計(jì)數(shù)據(jù)才能進(jìn)行一次仿真,整個(gè)過程往往耗時(shí)數(shù)天。”Griffin 說道。“而如今,Cadence 的工具僅提取必要的數(shù)據(jù),將仿真周期從幾天縮短至幾分鐘。”

在這一過程中,Cadence 的 Clarity 3D Solver 發(fā)揮了關(guān)鍵作用。傳統(tǒng)的全波 3D 電磁求解器僅用于解決特定的問題,但隨著設(shè)計(jì)日益緊湊和復(fù)雜,具備簽核級(jí)精度的電磁分析已成為必然趨勢(shì)。

“現(xiàn)如今,全波 3D 求解器被用作先進(jìn)封裝設(shè)計(jì)的標(biāo)準(zhǔn)解決方案。”Griffin 表示。“Cadence 的 Clarity 求解器兼具準(zhǔn)確性和可擴(kuò)展性,能夠幫助公司滿足新一代 AI 硬件的需求。”

高性能系統(tǒng)中的熱挑戰(zhàn)

隨著 AI 工作負(fù)載推動(dòng)功率密度不斷提升,熱管理已成為芯粒架構(gòu)設(shè)計(jì)工程師關(guān)注的核心問題。如果沒有適當(dāng)?shù)睦鋮s方案,即使是最先進(jìn)的半導(dǎo)體設(shè)計(jì)也可能面臨過熱和故障的風(fēng)險(xiǎn)。

“二十年前,熱分析并不是 Cadence 關(guān)注的重點(diǎn),”Griffin 表示,“但如今已成為客戶首要關(guān)注的問題。”

為了應(yīng)對(duì)這些挑戰(zhàn),Cadence 推出了多物理場(chǎng)仿真平臺(tái) Celsius Studio。該平臺(tái)集成了電熱協(xié)同仿真和計(jì)算流體力學(xué) (CFD),能夠仿真芯片、封裝、電路板和系統(tǒng)級(jí)別的散熱。

“借助 Celsius,電氣工程師可以仿真瞬態(tài)熱行為,動(dòng)態(tài)調(diào)整功耗以防止過熱。”Griffin 說道。“同時(shí),機(jī)械工程師能夠在同一環(huán)境中完成氣流、液體冷卻和外殼設(shè)計(jì)仿真。”

修復(fù)損壞的設(shè)計(jì)流程:

從“弗蘭肯流程”到集成工作流程

大型先進(jìn)封裝設(shè)計(jì)面臨的一個(gè)緊迫問題是 Griffin 所稱的“弗蘭肯流程”——依賴獨(dú)立且缺乏協(xié)調(diào)的工具進(jìn)行仿真、分析和設(shè)計(jì)的碎片化方法。

“工程師不可能花費(fèi)數(shù)周時(shí)間將數(shù)據(jù)從一種工具傳輸?shù)搅硪环N工具。”Griffin 說道。“Cadence 在設(shè)計(jì)環(huán)境中進(jìn)行仿真,消除了這一低效環(huán)節(jié),使工程師能夠在完成整個(gè)設(shè)計(jì)之前簽核關(guān)鍵子系統(tǒng)。”

Cadence前瞻性的“左移”方法將 PCB、IC 封裝和 3D-IC 設(shè)計(jì)工作流程與信號(hào)完整性、電源完整性、熱和電磁仿真相結(jié)合,確保工程師能夠在設(shè)計(jì)的早期階段發(fā)現(xiàn)并解決問題。

“我們正在見證設(shè)計(jì)思維的重大轉(zhuǎn)變。”Griffin 表示。“如今,越來(lái)越多的設(shè)計(jì)工程師直接運(yùn)行仿真,而不再等待專門的信號(hào)完整性或電源完整性專家來(lái)處理。這不僅加快了開發(fā)周期,還降低了設(shè)計(jì)錯(cuò)誤率。”

前景展望:仿真和 AI 驅(qū)動(dòng)設(shè)計(jì)的未來(lái)

隨著行業(yè)深入推進(jìn) AI 驅(qū)動(dòng)的芯片設(shè)計(jì),Cadence 不斷拓展其電子設(shè)計(jì)自動(dòng)化 (EDA) 解決方案。公司利用機(jī)器學(xué)習(xí)和基于云的仿真可擴(kuò)展性,進(jìn)一步簡(jiǎn)化異構(gòu)集成工作流程,使 AI、高性能計(jì)算和新一代半導(dǎo)體設(shè)計(jì)比以往更加高效。

Cadence 還專注于提高設(shè)計(jì)驗(yàn)證的自動(dòng)化水平,通過 AI 輔助仿真和驗(yàn)證,減輕工程師的負(fù)擔(dān)。隨著半導(dǎo)體制造商競(jìng)相開發(fā)突破能效和計(jì)算性能極限的芯片,這些進(jìn)步將變得尤為重要。

“我們不僅緊跟行業(yè)發(fā)展的步伐,”Griffin 總結(jié)道,“更致力于塑造行業(yè)的未來(lái)。”

-

Cadence

+關(guān)注

關(guān)注

67文章

973瀏覽量

144291 -

人工智能

+關(guān)注

關(guān)注

1806文章

48987瀏覽量

249039 -

封裝設(shè)計(jì)

+關(guān)注

關(guān)注

2文章

47瀏覽量

12064

發(fā)布評(píng)論請(qǐng)先 登錄

MUN12AD03-SEC的封裝設(shè)計(jì)對(duì)散熱有何影響?

Chiplet與先進(jìn)封裝設(shè)計(jì)中EDA工具面臨的挑戰(zhàn)

針對(duì)未來(lái)#AI服務(wù)器 發(fā)展,#思瑞浦 有哪些前瞻性產(chǎn)品布局

封裝設(shè)計(jì)圖紙的基本概念和類型

如何通俗理解芯片封裝設(shè)計(jì)

臺(tái)積電擴(kuò)大先進(jìn)封裝設(shè)施,南科等地將增建新廠

testo350加強(qiáng)型—第一臺(tái)具有前瞻性的煙氣分析儀手冊(cè)

博科測(cè)試IPO上市:深耕前瞻性技術(shù)研發(fā),助力推動(dòng)高端裝備國(guó)產(chǎn)化

芯片封裝設(shè)計(jì)引腳寬度和框架引腳的設(shè)計(jì)介紹

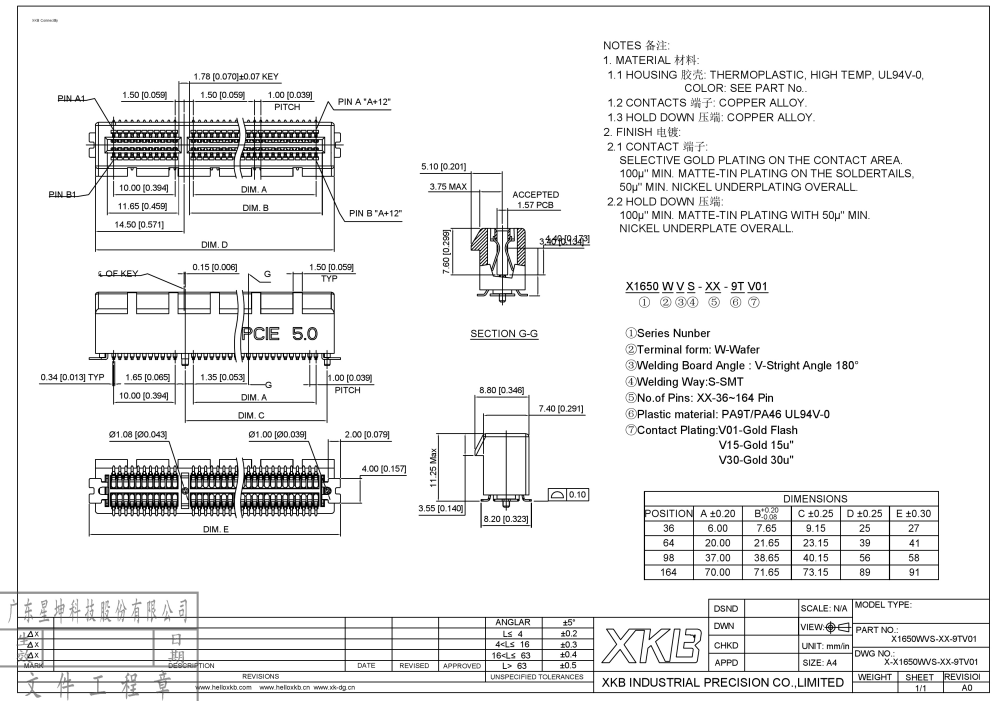

適應(yīng)未來(lái)技術(shù)演進(jìn):中國(guó)星坤PCI-E 5.0 SMT金手指連接器的前瞻性設(shè)計(jì)

開始報(bào)名!PCB/封裝設(shè)計(jì)及系統(tǒng) SI/PI/Thermal 仿真專場(chǎng)研討會(huì)——2024 Cadence 中國(guó)技術(shù)巡回研討會(huì)

晶圓廠與封測(cè)廠攜手,共筑先進(jìn)封裝新未來(lái)

DesignCon 采訪 | Cadence 的前瞻性方法和先進(jìn)封裝設(shè)計(jì)的未來(lái)

DesignCon 采訪 | Cadence 的前瞻性方法和先進(jìn)封裝設(shè)計(jì)的未來(lái)

評(píng)論