工藝微縮下的ESD挑戰(zhàn),CDM防護成關(guān)鍵?。

隨著半導體工藝節(jié)點不斷向5nm、3nm邁進,芯片內(nèi)部結(jié)構(gòu)日趨精密,靜電放電(ESD)問題愈發(fā)嚴峻。傳統(tǒng)人體放電模型(HBM)和機器模型(MM)失效占比逐漸降低,而?充電器件模型(CDM)?因其極快放電速度和高電流峰值,已成為芯片ESD失效的“頭號殺手”。據(jù)統(tǒng)計,CDM導致的失效占比已超過60%,尤其在高速、高密度集成電路中,防護設(shè)計面臨前所未有的挑戰(zhàn)。

?為什么VFTLP技術(shù)至關(guān)重要??

傳統(tǒng)TLP(傳輸線脈沖測試)技術(shù)被廣泛用于HBM防護器件的研發(fā)驗證,但其脈沖寬度(納秒級)難以精準模擬CDM事件中的超快瞬態(tài)特性(皮秒級)。而?VFTLP(超快傳輸線脈沖測試)?通過生成極快上升時間(<1ns)、超高電流(數(shù)十安培)的脈沖信號,可真實復現(xiàn)CDM放電場景,幫助工程師:

● 精準評估防護器件,在CDM應力下的觸發(fā)速度、電流泄放能力;

● 識別防護結(jié)構(gòu)中的“薄弱點”,優(yōu)化設(shè)計避免閂鎖效應和熱失效;

● 縮短芯片ESD防護方案的研發(fā)周期,提升一次流片成功率。

季豐ESD實驗室VFTLP服務亮點?

為助力客戶攻克先進工藝下的CDM難題,季豐電子ESD實驗室正式推出?VFTLP測試與分析服務?,覆蓋從研發(fā)到量產(chǎn)的全生命周期需求:

1全參數(shù)測試能力?

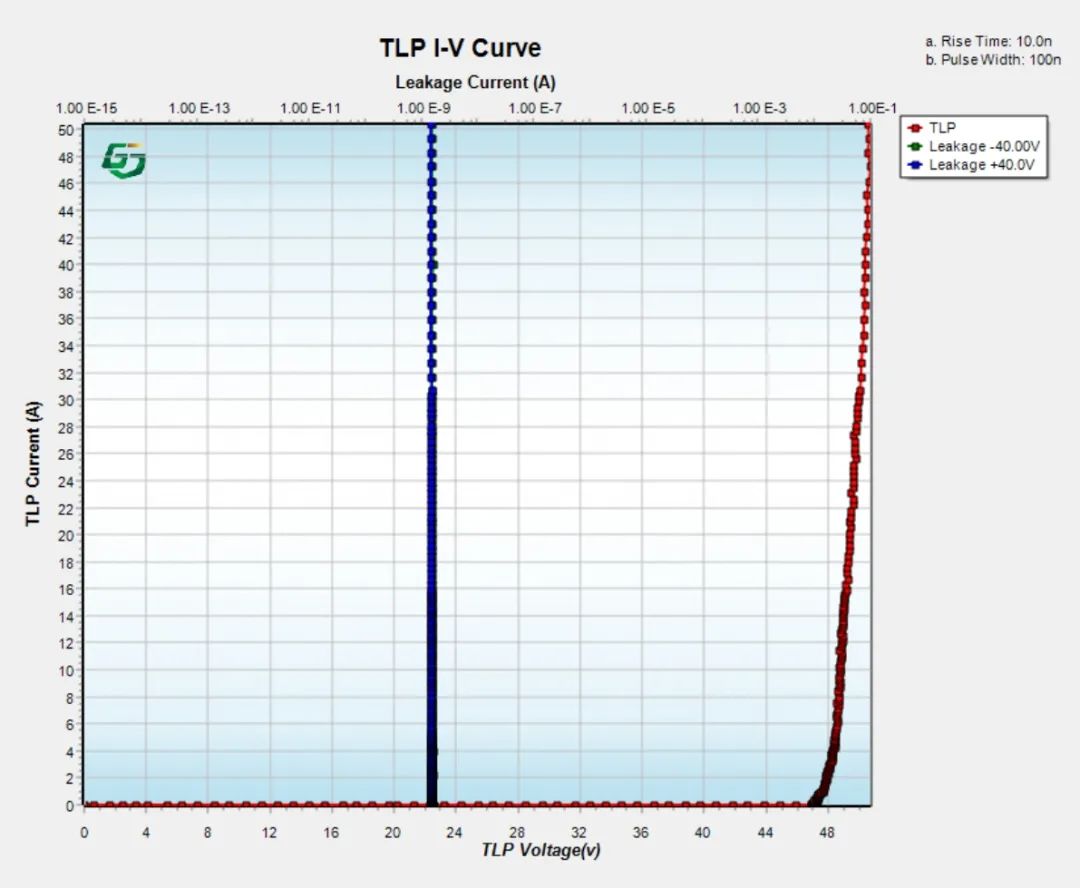

● 脈沖寬度:1.25ns~1000ns,支持CDM、HBM,IEC等多種模型模擬

● 電壓范圍:0.5V~2500V,電流峰值高達50A

● 支持IV特性曲線、失效閾值、時域波形等多維度分析

2應用場景全覆蓋?

● 晶圓級/封裝級器件CDM防護性能驗證

● 高速接口(USB/HDMI/SerDes)、射頻芯片、車規(guī)級芯片等高敏感電路ESD設(shè)計優(yōu)化

● 先進封裝(2.5D/3D IC、Chiplet)的ESD協(xié)同仿真數(shù)據(jù)支撐

3技術(shù)優(yōu)勢:為何選擇季豐??

● ?尖端設(shè)備?:采用業(yè)界領(lǐng)先的VFTLP測試系統(tǒng)Celestron,支持超快脈沖生成與高精度數(shù)據(jù)采集;

● 專家團隊?:15年以上ESD測試經(jīng)驗的工程師團隊,提供從測試到失效分析的深度解讀;

● ?數(shù)據(jù)權(quán)威性?:測試結(jié)果符合JEDEC、AEC-Q100等國際標準,助力產(chǎn)品通過車規(guī)、工業(yè)級認證;

● 快速響應?:7×24小時服務支持,3個工作日內(nèi)交付完整測試報告。

?● 客戶價值:從設(shè)計到量產(chǎn)的ESD保障?

● ?縮短研發(fā)周期?:通過VFTLP提前識別CDM風險,減少流片迭代次數(shù);

● ?提升可靠性?:優(yōu)化防護結(jié)構(gòu),確保芯片在極端靜電環(huán)境下穩(wěn)定工作;

● ?降低成本?:避免因ESD失效導致的批量召回風險;

● ?技術(shù)賦能?:提供設(shè)計建議,幫助客戶構(gòu)建自主ESD防護IP庫。

季豐電子

季豐電子成立于2008年,是一家聚焦半導體領(lǐng)域,深耕集成電路檢測相關(guān)的軟硬件研發(fā)及技術(shù)服務的賦能型平臺科技公司。公司業(yè)務分為四大板塊,分別為基礎(chǔ)實驗室、軟硬件開發(fā)、測試封裝和儀器設(shè)備,可為芯片設(shè)計、晶圓制造、封裝測試、材料裝備等半導體產(chǎn)業(yè)鏈和新能源領(lǐng)域公司提供一站式的檢測分析解決方案。

季豐電子通過國家級專精特新“小巨人”、國家高新技術(shù)企業(yè)、上海市“科技小巨人”、上海市企業(yè)技術(shù)中心、研發(fā)機構(gòu)、公共服務平臺等企業(yè)資質(zhì)認定,通過了ISO9001、 ISO/IEC17025、CMA、CNAS、IATF16949、ISO/IEC27001、ISO14001、ISO45001、ANSI/ESD S20.20等認證。公司員工超1000人,總部位于上海,在浙江、北京、深圳、成都等地設(shè)有子公司。

-

芯片

+關(guān)注

關(guān)注

459文章

52446瀏覽量

439843 -

ESD

+關(guān)注

關(guān)注

50文章

2284瀏覽量

175627 -

半導體

+關(guān)注

關(guān)注

335文章

28854瀏覽量

236711

原文標題:重磅升級 | 新增VFTLP測試能力,賦能先進工藝芯片CDM防護設(shè)計

文章出處:【微信號:zzz9970814,微信公眾號:上海季豐電子】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

愛普生與南山電子晶體電路評估聯(lián)合測試實驗室成立

遼寧材料實驗室一行到訪季豐電子

季豐電子如何提高太陽能電池的光電轉(zhuǎn)換效率

奕斯偉計算通過季豐電子AEC-Q100認證測試

BU-67121W實驗室航空電子接口計算機North Hills

衢州季豐新增參數(shù)特色檢測能力氨氣測試

成都季豐獲批CNAS實驗室認可證書

LIMS實驗室管理平臺的實施步驟

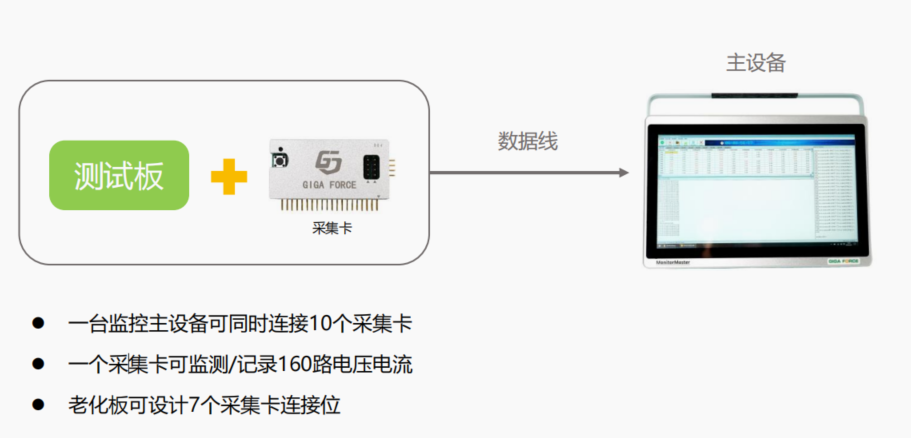

季豐電子MonitorMaster系統(tǒng)在BHAST實驗中的應用

季豐電子ESD實驗室新增VFTLP測試能力

季豐電子ESD實驗室新增VFTLP測試能力

評論