功率放大器 (PA) 線性化是無線接入網 (RAN) 面臨的一項關鍵挑戰,其對計算資源要求嚴苛。而隨著網絡向更高頻段、更大帶寬和更加動態的流量負載發展,對精準數字預失真 (DPD) 的需求也變得愈發迫切。

過去,DPD 通常依賴針對特定 PA 和部署場景調優的固定 DSP 算法。然而,隨著系統需求的演進,使用固定流水線已無法獲得理想的結果。這正是 AI 增強型 DPD 的價值所在,而 Altera Agilex SoC FPGA 為實現這一技術提供了理想的平臺。

AI + DSP:利用統一工具鏈,實現更智能的預失真

利用 DSP Builder、Quartus Prime 及第三方 AI 軟件,工程師能夠在協調一致的環境中將 AI 模型集成至傳統 DPD 處理鏈中。這種協同設計方法讓工程師能夠:

無縫集成機器學習模型進行 DSP 預處理或后處理;

在多種 DPD 拓撲結構和 AI 模型精度之間進行迭代;

快速評估資源占用、時延和線性化準確率之間的權衡方案;

針對實際部署,探索兼顧功耗、性能和占用面積的理想配置。

無論是采用行為模型、記憶多項式還是基于深度學習的估計器,這種工具鏈都能夠支持快速實驗,并助力生產級 DPD 解決方案的快速收斂。

對無線基礎設施的重要性

功率放大器效率會直接影響基站功耗,這是密集部署和邊緣節點中的重大問題。基于 AI 的 DPD 不僅能提升頻譜效率,還可降低功率回退需求和散熱壓力,尤其是當部署在 Agilex FPGA 這類專為低時延并行處理設計的硬件上時,效果更為顯著。

通過將傳統 DSP 信號鏈與可編程邏輯中的 AI 推理模塊相結合,設計人員能夠更加靈活自由地優化射頻性能。基于 FPGA 的 AI 不僅使混合架構成為可能,更使其具備了實際應用的可行性。

利用 FPGAi 實現

從實驗室到部署的跨越

Altera 提供的統一工具鏈可以助力無線系統設計人員實現快速迭代、進行深度探索,并最終交付更高性能的 RAN 解決方案。

通過在 FPGA 邏輯結構內完成 AI + DSP 流水線的仿真、測試和部署,您能夠更加輕松地實現從概念到落地的轉化過程。

-

FPGA

+關注

關注

1645文章

22026瀏覽量

617660 -

功率放大器

+關注

關注

102文章

3973瀏覽量

134612 -

Altera

+關注

關注

37文章

805瀏覽量

155897 -

AI

+關注

關注

88文章

34964瀏覽量

278502

原文標題:AI 與數字預失真 (DPD) 線性化在 Altera SoC FPGA 上的融合實踐

文章出處:【微信號:英特爾FPGA,微信公眾號:英特爾FPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

西門子推出用于EDA設計流程的AI增強型工具集

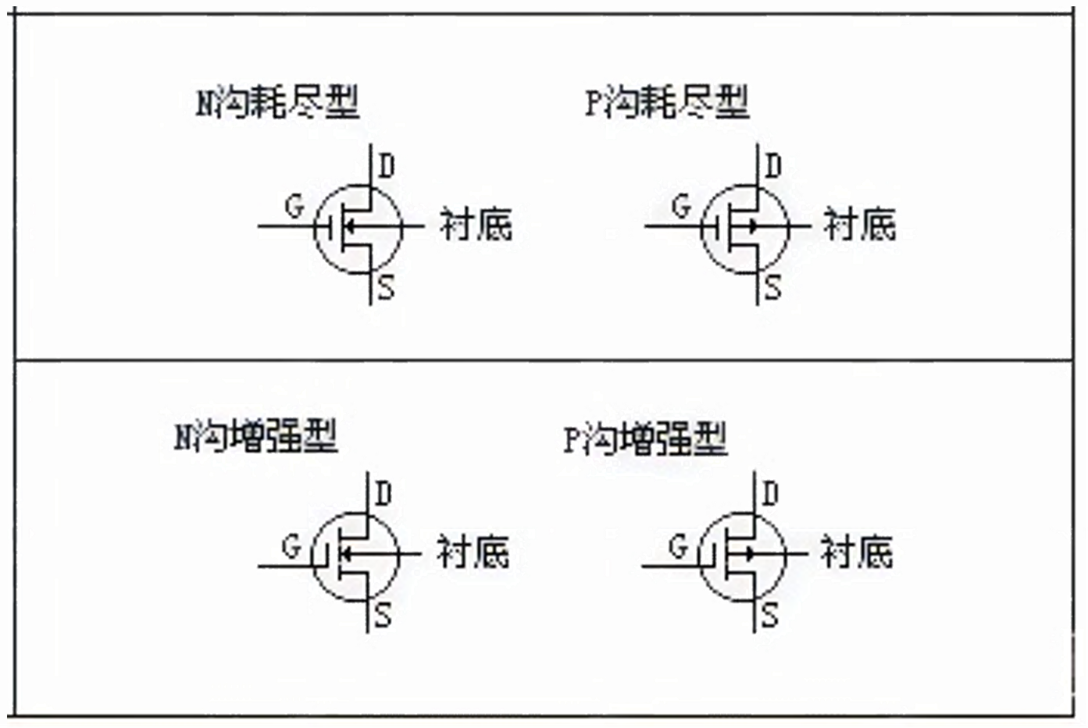

增強型和耗盡型MOS管的應用特性和選型方案

Altera Agilex 3 FPGA和SoC產品介紹

AI增強型DPD在Altera SoC FPGA上的應用

AI增強型DPD在Altera SoC FPGA上的應用

評論