一、SiP 封裝的誕生:技術瓶頸與市場需求的雙重驅動?

SiP(系統級封裝)的誕生并非偶然,而是半導體行業在技術極限與市場需求碰撞下的必然選擇,其背后是“性能突圍”與“場景適配”的雙重邏輯。?

從技術背景看,以 SoC(片上系統)為代表的“單片集成”路徑遭遇瓶頸:一方面,摩爾定律放緩,7nm以下制程成本呈指數級增長(3nm制程研發費用超50億美元),單純通過縮小晶體管提升性能的邊際效益遞減;另一方面,異構集成需求凸顯 ——消費電子、汽車電子等場景需要將 CPU、射頻、傳感器等不同工藝(如 CMOS、GaN)、不同代際的芯片集成,而SoC受限于單一晶圓工藝,無法兼容異構元件。?

從市場背景看,終端產品對“小型化、低功耗、快響應”的需求倒逼封裝技術革新:2010年后,智能手機進入“全面屏”競賽,要求芯片體積縮減30%以上;新能源汽車的智能駕駛系統需要集成77GHz射頻與信號處理,傳統分立封裝的信號延遲與空間占用難以滿足;工業物聯網設備則要求在方寸之間實現“感知-計算-通信”一體化,這些場景都指向“多芯片協同工作”的系統級解決方案。?

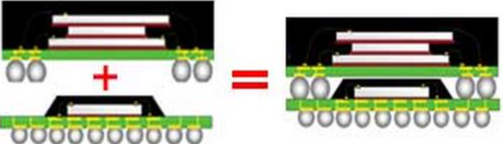

在這樣的背景下,SiP通過“封裝層面的系統集成 突破限制:無需將所有功能集成在單一芯片上,而是通過先進封裝工藝將多個芯片、無源元件(電阻、電容)甚至光學、射頻器件集成在同一封裝體內,實現“系統級功能”。這種“空間換性能” 的思路,讓SiP成為SoC的重要補充。?

二、SiP 封裝的發展階段:從“簡單堆疊”到“異構融合”?

SiP 的發展可分為四個階段,每個階段的技術特征與焊料需求高度綁定:?

1. 雛形期(2000-2010 年):多芯片模塊(MCM)的升級?

核心特征:以“2D 平面集成”為主,將同類型芯片(如CPU + 內存)通過引線鍵合或基板互連,封裝體積仍較大(通常>100mm2)。典型應用是早期智能手機的基帶芯片(如高通 MSM 系列)。?

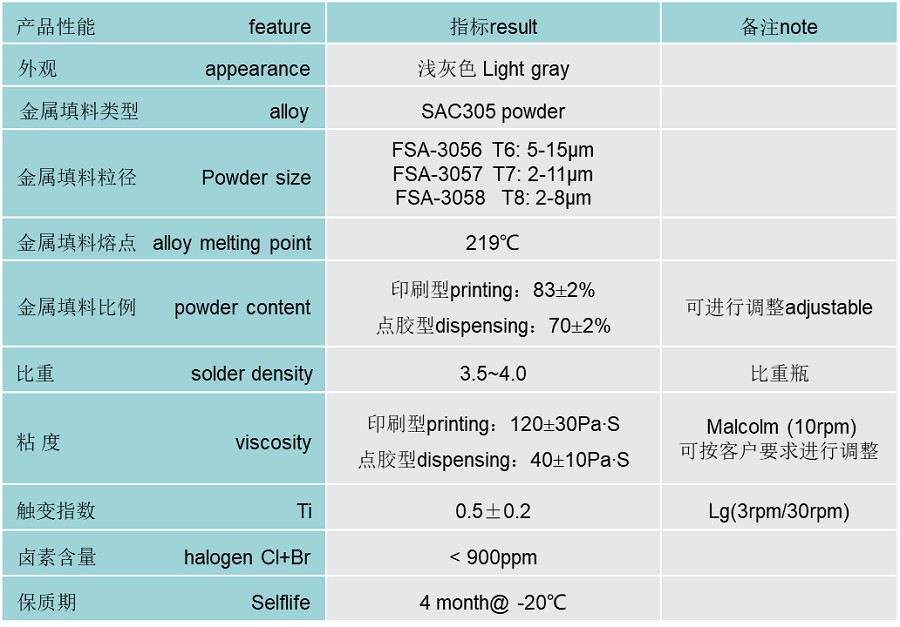

技術局限:互連密度低(I/O 數量<1000),信號延遲高,依賴傳統 PCB 基板。? 焊料需求:2006年前以有鉛錫膏(Sn63Pb37)為主,熔點183℃,印刷精度≥100μm;2006年歐盟RoHS指令實施后,無鉛焊料(如SAC系列)快速普及,逐步替代有鉛產品,側重“能焊牢 的基礎需求。?

2. 成長期(2010-2015 年):扇入/扇出型WLP與倒裝芯片結合?

核心特征:引入晶圓級封裝(WLP)技術,通過扇入/扇出型工藝擴展I/O 數量(1000-5000),實現芯片與基板的“面陣互連”,蘋果A8芯片是典型代表(集成 A8 應用處理器和M8運動協處理器)。?

技術突破:銅柱凸點、重布線層(RDL)開始應用,封裝厚度降至1mm以下。?

焊料需求:無鉛化成為主流,SAC305(Sn3Ag0.5Cu)錫膏普及,要求“細間距適配”(50-100μm)、低空洞率(≤10%);助焊劑需提升活性,應對銅基焊盤的氧化問題。?

3. 爆發期(2015-2020 年):3D堆疊與異構集成落地?

核心特征:3D堆疊技術成熟,通過TSV(硅通孔)實現芯片垂直互連,I/O數量突破10000,可集成異構元件(如CPU+5G 基帶 + 射頻前端),華為麒麟990 5G是標桿產品(主流集成 5G 基帶的手機芯片之一)。?

技術突破:混合鍵合(Hybrid Bonding)、嵌入式封裝(Embedded Die)出現,支持光子、MEMS等跨領域元件集成。?

焊料需求:超細粉末錫膏(T6/T7 級,粒徑5-20μm)成為剛需,適配20-50μm 間距;低熔點錫膏(如 Sn58Bi,熔點 138℃)用于多層堆疊的“階梯焊接”,避免高溫損傷下層芯片;助焊劑需具備“耐多次回流”能力,在200℃以上保持活性。?

4. 成熟期(2020 年至今):Chiplet與超異構集成?

核心特征:以Chiplet為核心的“模塊化集成”成為主流,通過標準化接口(如 UCIe)將不同功能的Chiplet(計算、存儲、互連)像“樂高積木”一樣集成,AMD MI300X、英偉達H100均采用該架構。?

技術突破:間距縮至10μm以下,信號傳輸速率突破100Gbps,熱管理引入液冷、微通道技術。?

焊料需求:微米級錫膏(T8級,粒徑 2-8μm)實現10μm以下間距印刷;高頻場景下關注焊料的導電性能和焊點信號完整性,減少信號損耗;銀膠等導熱焊材(熱導率≥80W/m?K)解決高密度集成的散熱問題。?

三、SiP封裝的未來態勢:向“全域集成”與“智能感知”進化?

未來 5-10 年,SiP將沿著三個方向突破:?

超異構集成:從“電子元件”擴展到“跨物理域集成”,如將光子芯片(光通信)、量子比特(量子計算)、生物傳感器(醫療設備)納入SiP,要求焊料適配不同材料(硅、玻璃、陶瓷)的表面特性,例如針對光子芯片的玻璃基板,需開發能提升焊料與基板界面反應(如形成金屬間化合物)的助焊劑,增強附著力,同時保證焊料對基板的潤濕性(接觸角≤30°)。?

動態可重構:通過“可重構互連”技術,讓SiP內的芯片可按需切換連接方式(如算力分配、功耗調節),這需要焊料具備“低接觸電阻”(≤5mΩ)和“高抗疲勞性”(10000 次溫度循環無失效),支持動態信號路徑切換。?

極致小型化與能效:終端設備(如可穿戴、植入式醫療)要求SiP體積縮至1cm3 以下,功耗降至1mW,推動焊料向“無鉛低溫合金”(如 Sn-Zn-Bi,熔點 180-190℃)、“納米復合焊材”(添加石墨烯片等提升導熱)發展。

?

四、焊料的“進化史”:從“連接工具”到“性能賦能者”?

SiP 的發展直接推動焊料從“簡單連接材料”升級為“系統級性能支撐者”,其進化路徑與SiP需求高度耦合:?

粒徑微縮:從早期的T3 級(25-45μm)到現在的 T8 級(2-8μm),下一步將突破亞微米級(1-3μm),適配5μm以下間距的Chiplet互連,需解決“粉末氧化”(通過惰性氣體保護制造)和“印刷堵網”(優化球形度至≥98%)問題。?

合金體系迭代:從鉛基到無鉛(SAC系列),再到低熔點(SnBi)、高溫穩定(Sn-Ag-Cu-Ni),未來將探索通過優化合金成分比例及添加合適微量元素,讓焊點在溫度變化時更好地緩解應力,減少開裂風險。?

功能復合化:從單一“焊接功能”到“多功能集成”,例如:?

高頻焊料:通過優化合金成分,提升導電性能,減少趨膚效應影響,適配 100Gbps以上信號傳輸。?

自修復焊料:嵌入微膠囊型助焊劑,當焊點出現微裂紋時,膠囊破裂釋放助焊劑,修復氧化層。?

焊點狀態監測:通過在封裝結構中布置外部傳感器(如熱電偶、應變片),實時監測焊點溫度、應力,為SiP的健康管理提供數據。?

工藝適配性優化:針對SiP的多樣化工藝(激光焊、混合鍵合、熱壓焊),開發 “工藝定制化焊料”—— 例如激光焊專用錫膏(高耐熱助焊劑,在250℃以上不碳化)、混合鍵合配套助焊劑(支持Cu-Cu直接鍵合的表面活化)。?

SiP的本質是“用封裝創新突破芯片物理極限”,而焊料則是這場創新的“隱形基石”。從智能手機到量子計算機,從可穿戴設備到深空探測器,SiP的每一次突破都伴隨著焊料的技術躍升。未來,隨著SiP進入“全域集成”時代,焊料將不僅是“連接者”,更會成為“性能定義者”——通過材料創新,為系統級封裝的可靠性、能效與功能拓展提供無限可能。

-

SoC芯片

+關注

關注

1文章

644瀏覽量

35783 -

錫膏

+關注

關注

1文章

941瀏覽量

17434 -

助焊劑

+關注

關注

3文章

138瀏覽量

11588 -

晶圓級封裝

+關注

關注

5文章

41瀏覽量

11658 -

sip封裝

+關注

關注

4文章

68瀏覽量

15726

發布評論請先 登錄

SiP 封裝與錫膏等焊料協同進化之路?

SiP 封裝與錫膏等焊料協同進化之路?

評論