先進的串行通信標準外圍組件互連(PCI)最初用于個人電腦,以克服限制并行總線標準帶寬的挑戰如時鐘和數據信號偏移。PCI作為串行互連,還有助于避免實現并行數據鏈路所需要的高引腳數。

后來PCI升級到PCI Extended (PCI-X),然后到PCI Express (PCIe),這是一種點對點的全雙工串行計算機擴展總線標準,取代了較早的標準并支持更快和更靈活的方案。

PCIe通過三代發展演變,現已能滿足更高速度和數據吞吐量。第一代PCIe 1.1采用2.5GT/s(千兆傳輸每秒)的原始數據傳輸速率和8b/10b的數據編碼,支持每通路500MB/s的高效的數據吞吐量。PCIe 2.1通過提高傳輸速率到5.0GT/s增加數據吞吐量到每通道1GB/s。PCIe 3.0通過將傳輸速率進一步提高到8GT/s和采用更高效的128b /130b編碼方案相結合,達到每通路2GB/s的數據吞吐量。

一條PCIe通路包含發送和接收兩條不同的通道。總PCIe鏈路數據帶寬可通過增加額外的通路擴展。這靈活性已使PCIe普遍用于服務器、網絡附加存儲、網絡交換機、路由器和機頂盒等應用中。這些應用固有的嚴格的時序預算和系統挑戰對PCIe時鐘性能施以嚴苛的要求。

PCIe指定一個100 MHz的外部參考時鐘(Refclk),精確度在± 300ppm以內,用于協調在兩個PCIe設備間的數據傳輸。PCIe標準支持三種范圍的時鐘分配方案:公共時鐘、數據時鐘和分離時鐘架構。所有時鐘方案都要求±300ppm的相同的時鐘精確度。

在公共時鐘架構中(圖1),單個Refclk源被分配到發送器和接收器。這種時鐘方簡單而普遍用于成本敏感的商業應用。支持擴頻時鐘(SSC)可最大限度地減小電磁干擾(EMI)敏感的應用中的電磁輻射。

圖1:公共時鐘架構。

在數據時鐘架構中(圖2),時鐘信號被嵌入并從數據信號中恢復。時鐘恢復需要額外的硬件,以在接收端從信號流提取時鐘。數據時鐘架構也支持SSC。

圖2:數據時鐘架構。

分離時鐘架構(圖3)通過在每一PCIe端點使用分離時鐘源,而省去向所有通道發送時鐘。該標準允許在時鐘間± 600ppm的頻率間隔,以便每一Refclk仍然保持± 300ppm的頻率精確度范圍。因為時鐘是獨立的,接收器的有效抖動是發送器抖動和接收器鎖相環(PLL)的和的平方根(RSS)。這種架構沒有指定抖動限制。但可直觀地理解為它的抖動預算比共同時鐘架構更嚴格。

圖3: 分離時鐘架構。

以往,若采用± 300ppm的整個允許的頻率幅度,在分離時鐘架構中Refclks間允許的有限的頻率間隔已阻礙了SSC的采用。但以不同的發射器和接收器速率的時鐘是被允許的,在Refclks間的頻率間隔高達5600ppm。PCI-SIG正著手起草獨立的分離參考時鐘獨立擴頻(SRIS)標準。安森美半導體PCIe時鐘發生器符合這草擬標準中說明的SRIS Refclk要求。

系統抖動源和影響

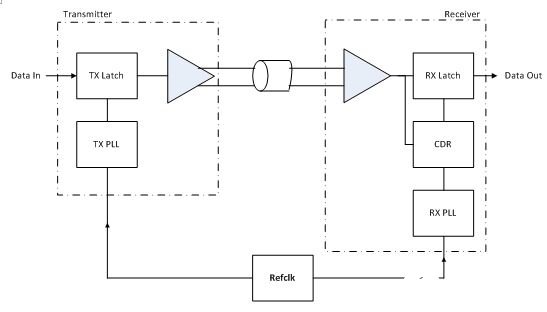

圖4顯示一個采用公共時鐘架構的PCIe x1鏈路。內部鎖相環(PLL)負責復用Refclk達25次,以產生所需的更高頻率信號,以通路比特率傳輸數據。

圖4:PCIe x1數據鏈基本功能塊。

PCIe鏈的整體目標是以高的統計成功確定性從發射器到接收器傳輸大量數據。為實現此,接收器必須采樣由位中心或附近的發射器發出的數據位。在接收器中,時鐘/數據恢復塊(CDR)產生一個時鐘,定期采樣數據到鎖存器。各種相位抖動源引起樣本時序波動。由于樣本位置偏離理想位置,誤碼率增加。

系統中的相位抖動源包括參考時鐘抖動、發射器PLL和接收器CDR獨立的相轉移功能、電源噪聲影響,和電纜及PCB空間分散、符號間干擾、串擾和反射的影響。

總相位抖動以皮秒計算,由各種源產生,引起采樣時鐘和數據位中心間的位移。按照數據眼圖術語,誤碼被定義為相位抖動的累積引起數據和采樣時鐘間的總相位差超過數據眼寬度的一半,否則被稱為單元間隔(UI)。

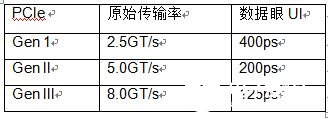

表1顯示在PCIe 2.1和3.0中數據傳輸率更高UI變短,這有效地實行更嚴格的抖動預算。

表1:PCIe Gen 1到III數據速率和數據眼UI的比較。

低抖動設計

采用穩壓電源和校正電路設計可有效地消除電源噪聲影響。同樣,采用阻抗匹配、高品質板材和優化布線可設計出防止信號完整性問題如ISI和串擾。

參考時鐘抖動是最難抑制的。它的影響不僅成倍增加并直接以發送信號傳播,而且對接收器信號恢復產生不利影響。

Refclk包含寬范圍的頻率抖動。接收器只能跟蹤這些頻率的一個波段。有意義的PCIe系統抖動主要是通過時鐘/數據恢復(CDR)模塊的傳輸功能跟蹤抖動分量(不濾波)。對于PCIe Gen I、II和III模型,用于計算抖動的數學函數是不同的。

信號抖動由確定性(Dj)和隨機(Rj)性內容組成。Dj由非高斯概率密度函數有界的振幅控制。它有特定的起因如干擾、數據依賴和占空比失真(DCD),是可預測的。對于時鐘,Dj在相位噪聲圖中呈現出一定幅度的毛刺。

Rj呈現高斯分布且無邊界。它的存在是由于隨機現象如熱噪聲和工藝變異。在時鐘中,Rj在特定頻率偏移范圍呈現出集成的相位噪聲。總抖動(Tj)通過卷積法從Dj和Rj計算。

n 取決于BER鏈(以太網為10-12)

表2描述在特定頻帶(基于CDR傳輸功能) PCIe Gen I、II和III系統可接受的Tj值,并比較這些要求與安森美半導體的NB3N51034四輸出HCSL/LVDS時鐘生成器性能,NB3N51034適用于Gen I、Gen II 和Gen III應用。

表2:PCIe規格抖動限制和PCIe時鐘性能。

時鐘樹設計

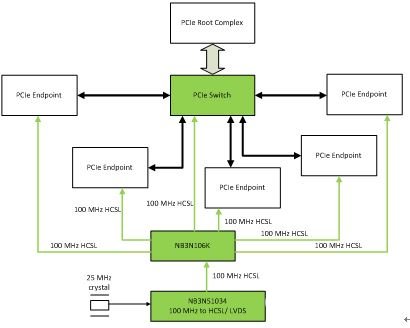

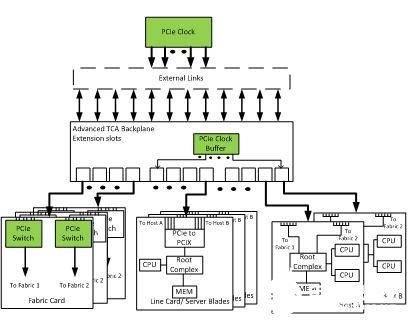

當設計任何PCIe系統時,考慮到將來的擴展,好的時鐘樹技術至關重要。恰當的PCIe時鐘源的最佳選擇、緩沖器和開關取決于系統中內部和外部PCIe I/O(包括以后的擴展)數量,以及速度和帶寬要求。圖5和圖6說明了常用的時鐘樹架構。在計算系統中,CPU和存儲器通過由多個稱作PCIe Root Complex 的PCI Express通路組成的集線器交換數據。

圖5:典型的計算系統PCIe時鐘樹。

圖6:典型的嵌入式/通信PCIe時鐘樹。

時鐘樹通常由多個功能部件組成,包括時鐘生成器、扇出緩沖器、零延遲緩沖器和開關。雖然選擇具有亞皮秒相位抖動性能的同類最佳時鐘源是重要的,以確保符合PCIe規格的最佳性能,但用于分配多個高精度、低相位噪聲時鐘的緩沖器還必須有低附加相位抖動和低輸出到輸出偏移(skew)。

安森美半導體提供一系列緩沖器適用于PCIe Gen I、Gen II 和Gen III應用,典型的附加相位抖動低至0.1ps rms(在12 kHz到20 MHz集成),最大輸出偏移為100 ps。低電流、多通道PCIe開關與這些精密的時鐘和緩沖器一起使用,令單個控制器能管理多個PCIe插槽,如圖6所示。

結語

下一代PCIe提供更高的數據傳輸速度,但對抖動的承受力較低。雖然在PCIe系統內有各種干擾源,如電源噪聲和符號間干擾,但參考時鐘是難以根除的主要抖動源。因為PCIe標準支持多種時鐘分配策略,所以仔細選擇低抖動時鐘源和時鐘樹組建至關重要,以符合高速單路或多路PCIe系統的抖動預算。

責任編輯:gt

-

接收器

+關注

關注

15文章

2563瀏覽量

73458 -

時鐘

+關注

關注

11文章

1886瀏覽量

132884 -

PCIe

+關注

關注

16文章

1328瀏覽量

84738

發布評論請先 登錄

Microchip面向下一代數據中心應用推出四款全新20路微分時鐘緩沖器

化PCIe應用中的時鐘分配方法

ML605——PCIe MGT參考時鐘抖動怎么回事

輸入抖動約束是否對PCIe源時鐘有效?

近場通信NFC:無線數據傳輸的下一個王者?

核芯互聯推出符合DB2000QL及PCIe Gen5和Gen 6標準的低抖動時鐘緩沖器CLB2000

低抖動時鐘源和時鐘樹組建為下一代PCIe提供更快的數據傳輸速度

低抖動時鐘源和時鐘樹組建為下一代PCIe提供更快的數據傳輸速度

評論