引言

在進行網絡應用的硬件設計時,開發者經常會面臨將設計思想轉化為具體的硬件電路時不得不從繪制電路圖、PCB制板,元件焊接等步驟一步步來繁瑣而漫長的過程,或者只能通過工具軟件進行模擬仿真卻無法及時進行實際測試的情況。另外,在計算機網絡通信等課程的教學過程中,也存在著學生缺乏有效的實驗手段,難以更深入了解網絡設備實際的工作機理的問題。為此,我們設計開發了基于FPGA、MPC860架構的網絡層應用硬件開發平臺,較好地解決了上述問題。

通過開發平臺,開發者可以實現數據包的分析、處理及轉發,在開發平臺之上可實現的主要功能包括以下幾部分:

1. 協議識別和分類:根據數據包的協議類型、端口號、目的地址、以及其它特定于協議的信息對數據包進行識別。

2. 拆裝和重組:數據包的拆分,處理,以及為轉發而重組。

3. 排隊和接入控制: 識別出數據包之后,將這些數據包送往相應的隊列中以進行下一步處理,如優先處理,流量整形等。同時,可根據某些安全接入策略進行數據*濾,確定是繼續轉發,還是丟棄。

另外還包括流量整形和流量工程、 QoS(Quality of Service)和CoS(Class of Service)、修正數據包、差錯檢測等。

搭建這個硬件開發平臺后,應用開發者只需關注于核心的硬件邏輯和算法設計,可以及時地驗證算法,*估效果,使得設計能盡快轉化為實際的電路,將在FPGA開發環境下的功能仿真、時序仿真更進一步至實際電路的測試,極大地方便應用開發。

通過這個硬件平臺,學生也可方便地進行計算機網絡實驗,獲取硬件開發經驗,提升科研能力。

2 實現原理

1、網絡設備的基本功能是實現網絡通信業務流的控制和轉發, 處于網絡邊緣的設備需要將來自不同物理鏈路的各種業務流復用到統一的傳輸鏈路上,傳統的方法是在網絡邊緣設備上采用通用的處理器來完成協議棧處理、路由選擇以及包頭的剝離等功能。隨著傳輸線速率的增加,通用處理器無法維持和傳輸速率一樣的處理速度,于是用專用芯片完成包的處理成為一種趨勢。利用專用集成電路(ASIC)來完成特定包的處理工作,性能得到很大的改善,但是ASIC缺乏靈活性給網絡設備的升級和功能擴展改進帶來很大麻煩。隨著傳輸線速的高速增長和高層協議處理日益增加的復雜度,以及各種網絡應用需求的靈活多變,高速和靈活地完成各種協議層上包處理顯得更為迫切,而FPGA技術的進步則為這種要求提供了堅實的物理基礎。FPGA和MPC860組成的系統架構,則同時具有通用處理器的靈活性和ASIC的高速處理的能力。

從概念上來看,以上所有的應用都是基于如下的處理流程:物理層把來自物理介質的光、電信號轉換成一定格式的比特流幀,幀轉交到網絡處理模塊。網絡處理模塊通過兩條通道處理數據幀,快速通道,如數據通道或者轉發通道,實現線速處理轉發數據幀,這部分是由FPGA完成的;慢通道,如控制通道,完成小部分數據幀(如控制、信令、路由幀)的處理,則可由MPC860完成。

2、在這里需要討論一下為什么選擇FPGA而不是網絡處理器(NPU)?

網絡應用中可編程解決方案主要有兩類:NPU和FPGA,兩者都是可編程的。NPU可提供以處理器為中心(即以軟件為中心)的可編程特性,而FPGA則提供以硬件為中心的可編程特性。一般而言,以軟件為中心的方法的性能低于以硬件為中心的方法。FPGA優于NPU還體現在以下幾個方面:

* 深度分組處理:與需要多個NPU進行深層分組處理的NPU解決方案不同,FPGA解決方案只需一塊FPGA,這是因為FPGA中的硬件并行處理完全可以同NPU中基于RISC的處理方法相媲美。多個NPU不僅為硬件和軟件分區帶來新挑戰并增加了軟件的復雜度,而且還增大了系統延遲和功耗。

* 軟件可升級性:NPU不具備代碼復用,因為NPU的軟件大多是不可移植的,即這些軟件是專有的匯編代碼或因定制程度過高而喪失移植性的C代碼。相反, FPGA則具有較強的軟件升級功能。

* 硬件可升級性:硬件的可升級特性確保了較長的產品壽命,因而成為可編程解決方案的一個關鍵特性。NPU只在處理器中提供可編程特性,其類似ASIC的定制硬件并不能直接進行編程,因此它在硬件升級上的劣勢與ASIC非常相似。FPGA顧名思義就是現場可編程,是對數據進行高速并行處理的理想器件,具有極強的靈活性和擴展性,可輕松升級,以很好地滿足需求變化。

3、MPC860是基于PowerPC結構的通信控制器。它不僅是集成的微處理器,而且將很多外設的功能也集成在一起。MPC860具有功能很強的存儲控制器,可以支持各種存儲器,包括各種新型的DRAM和Flash,并可以實現與存儲器的無縫接口。使用嵌入式操作系統VxWorks和開發環境Tornado進行開發也非常方便。

之所以使用MPC860,是為了系統的靈活性考慮。利用它可以完成一些較復雜的算法功能,和FPGA相配合,充分發揮各自的長處,以適應不同的網絡應用。

4、在開發平臺的設計中,考慮到了系統的可擴展性和靈活性,盡管FPGA內部已有豐富的存儲器資源,我們仍特別為FPGA配置了片外的SRAM,并在SRAM的容量上作了較大的冗余,可完成一般情況下的數據包存貯。同時考慮到FPGA處理速度的因素,SRAM的數據總線的寬度設計為64位,這樣,由FPGA進行SRAM讀取操作時不會產生阻塞現象。

3 具體實現

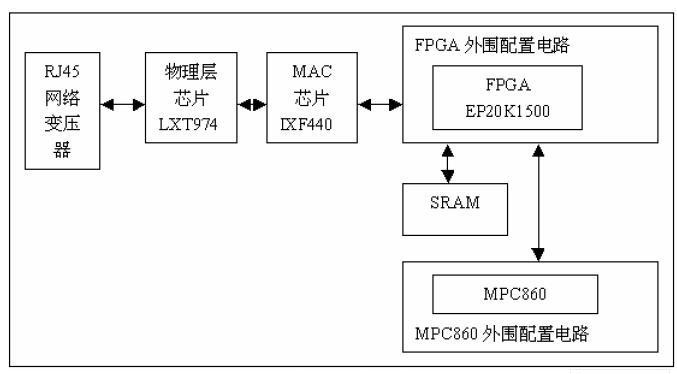

開發平臺由以太網控制器(MAC),FPGA,SRAM,MPC860,物理層芯片,網絡變壓器等元器件組成,系統組成如圖1所示。

圖1 系統組成框圖

本開發平臺的硬件功能完全在一片FPGA中完成。從功能需求和可持續開發的角度出發,選擇了ALTERA公司的APEX20KE1500。之所以選擇APEX20KE1500,主要是因為此型號的規模大,邏輯門達到150萬門,51840個邏輯單元(LEs)特別是其內部可定義的存儲單元大,達到了442368位,可靈活地實現為RAM、ROM、CAM,可以滿足緩存數據包的需求,又有利于設計復雜的存儲、查找、比對等功能。

MAC選取了Intel的IXF440,它是一個8口10/100Mbits以太網控制器,用以接收和發送以太包。LXT974是4端口快速以太網物理層芯片,它支持IEEE802.3協議,支持10Mbps 和100Mbps應用,提供四個獨立的MII接口。每個端口可支持雙絞線接口和連接10/100BASE-TX 或 100BASE-FX 的PECL。在本開發平臺上,使用了兩片百兆PHY芯片LXT974,這樣共可提供8個網絡接入端口。

4 應用實例

利用此開發平臺可以實現如8口以太網交換機,8口以太網路由器,網絡防火墻等,在本文中將以總裝備部課題DDoS的防御為例予以介紹。

隨著網絡技術的發展和Internet的普及,網絡安全問題也日益突出。高速廣泛連接的網絡給大家帶來了方便,也為分布式拒絕服務(DDoS)攻擊創造了極為有利的條件。DDoS攻擊已經成為網絡上廣泛傳播的問題。我們在本開發平臺的基礎上,通過尋求一種高效、對各種DDoS攻擊都行之有效的算法,采用軟硬件相結合的方法,實現了實時檢測、防御DDoS攻擊的功能。

利用該開發平臺,我們用MPC860實現非參數的CUSUM算法,在嵌入式實時操作系統VxWorks及其開發環境Tornado下對MPC860進行開發;用FPGA實現硬件功能,采用AHDL語言對FPGA進行開發,在MAX+PLUS II和Quartus II環境下對FPGA進行調試和仿真;

根據CUSUM算法計算出判決門限,檢測出DDoS攻擊,由硬件對攻擊包進行實時處理,采取有效措施維護網絡的正常運行,消除攻擊的危害。

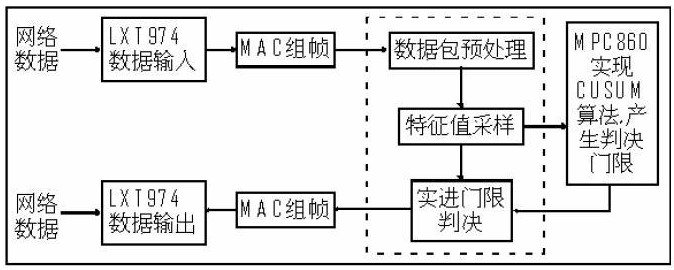

完整的DDoS防御系統置于網段入口,它包括了從數據接收、數據預處理、數據采集、數據運算和處理、實時判決到最終的數據輸出這一整套步驟。數據流程見圖2。

由FPGA完成了數據包的預處理功能,包括數據包類型的讀取;源IP地址,目的IP地址的讀取、比較;數據包協議類型的提取;IP數據包頭的奇偶校驗;TCP/UDP數據包端口提取,檢測等。特征值的數據采樣也由FPGA完成。MPC860根據FPGA提取的特征值進行計算產生判決門限和過濾規則,由FPGA根據MPC860得出的過濾規則實現實時的門限判決。

由于有了本開發平臺,研究小組集中精力于HDL語言和檢測算法,在較短的時間內完成了建模和仿真,并進行了實際的電路運行測試,根據測試中存在的問題及時調整了硬件邏輯和算法,最終比原計劃提前半年完成了該課題的研究。

另外,該開發平臺在網絡課程教學中也得到了有效的應用。在講授交換機原理,路由協議、排隊算法等課程時,讓學生對一些簡單的算法進行硬件仿真設計,并下載至開發平臺上進行實驗,加深了學生對所學知識的理解,掌握了初步的硬件設計能力和設計思想,為學生的科研能力的提高打下了較好的基礎。

-

處理器

+關注

關注

68文章

19485瀏覽量

231501 -

FPGA

+關注

關注

1632文章

21816瀏覽量

607006 -

pcb

+關注

關注

4331文章

23197瀏覽量

400880

發布評論請先 登錄

相關推薦

MPC860 的中斷處理技術研究

VxWorks下MPC860的中斷處理機制及其應用

MPC860 Power QUICC及其在嵌入式系統中的應用

VxWorks下MPC860的中斷處理機制及其應用

VxWorks下MPC860的中斷處理機制及其應用

基于MPC860的HDLC通道驅動程序的設計與實現

基于MPC860和VxWorks的硬件防火墻設計及實現

基于MPC860的SIMADYN D通信板的設計

基于MPC860與ST16C654的串行通信設計

基于MPC860的HDLC通道驅動程序的設計與實現

MPC860寄存器配置

TMS320C6000擴展總線與MPC860的HPI接口設計

采用FPGA器件和MPC860架構實現網絡應用硬件開發平臺的設計

采用FPGA器件和MPC860架構實現網絡應用硬件開發平臺的設計

評論