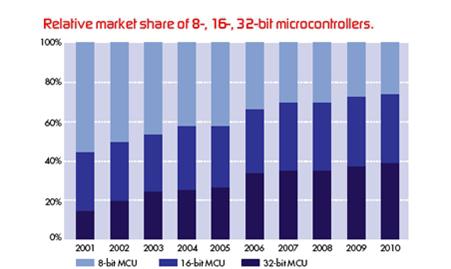

嵌入式系統與桌面PC結構非常不同,但其底層技術發展卻是一樣的,而且遵循著類似發展趨勢。當桌面PC轉向64位架構來滿足不斷增長的存儲器要求時,嵌入式系統也由于同樣的原因快速轉向32位處理器。桌面/服務器計算市場主要是圍繞x86架構,大多數創新和差異都在系統級,如雙核、四核或多核中央處理架構、集成圖像處理器單元和存儲器控制器等等。同樣,嵌入式系統則主要圍繞簡單的32位RISC處理器,多核架構、集成外設以及可配置處理等系統級發展,使得設計人員能夠快速適應不斷變化的應用要求。根據iSuppli的研究報告,2007年32位微控制器(MCU)市場將超過8位MCU市場。如圖1所示,32位MCU市場的增長速度超過了半導體市場其它部分的增長速度,而8位MCU市場的份額過去幾年時間里則有所下降。

這一趨勢的主要推動力是嵌入式系統中軟件內容和復雜性的不斷增加,因此直接產生的后果是需要更寬的存儲器總線(32位)來滿足軟件程序所使用的代碼和數據要求。與傳統微處理器不同,32位處理器不需要分段等存儲器管理技巧就可以處理更大的存儲器空間,因此使編程更容易。8位MCU必須采用難學難用的匯編語言來滿足小存儲器空間限制(少于32K字節),而許多32位嵌入式應用則可以利用C/C++來編程,從而提高了嵌入式軟件開發人員生產力。更為重要的是,越來越多的操作系統(實時和非實時)都提供現成的驅動程序和軟件庫,從而使軟件開發人員能夠集中于應用本身的開發。

集成降低成本

在摩爾定律的指引下,越來越細的硅工藝線寬使得32位嵌入式解決方案的成本不斷降低,從而可以滿足更多的應用對價格的要求。此外,集成外設和片上存儲器進一步降低了元器件和總體材料清單成本。通過集成針對手機和游戲機等垂直應用而優化的外設,許多器件的價格大大降低,直接推動了市場增長。

價格壓力還導致只能在這些系統中集成一組固定的外設,因此通常的外設組合是面向大批量應用的。然而,不可能有適用于所有應用的萬能器件,因此許多小批量、中等規模甚至大批量應用都無法直接利用成品集成解決方案。其結果是設計人員必須采用額外的芯片來擴展外設、分流處理器的負擔,或增加膠合邏輯。這也是可配置處理解決方案產生的原因。

可配置32位處理

根據Gartner Dataquest的報告,如圖2所示,基于FPGA嵌入式處理方案的應用正在增長,到2010年,約40%的FPGA設計將包括嵌入式處理器。因為能夠定制滿足特定應用或產品的要求,嵌入系統設計人員正在越來越多地采用基于FPGA的可配置處理解決方案。這一方法的主要優點是可通過集成降低成本,同時還可實現產品在市場上的差異化。

通過選擇同一FPGA系列中的不同器件,或者將設計重新適配到新的FPGA器件中,能夠針對更高性能、更低成本、或者不同的I/O標準進行個性設計。這樣可以降低設計過時的風險,從而保證設計是未來可用的。對于必須有長使用壽命的產品(如汽車或工業應用),這是特別關鍵的一個因素。

圖1:32位MCU市場的增長速度超過了其它類型的MCU的增長速度。

可配置處理系統的配置(或定制)的層面包括:

處理器配置

1. 乘法器、除法器、浮點單元以及其它。

2. 指令或數據緩沖配置。

3. 協處理器或硬件加速器。

系統配置

1. I/O外設選擇、定制、DMA選擇。

2. 存儲器外設選擇、定制。

應用配置

1. RTOS選擇、定制。

2. 應用庫/中間件定制。

許多產品都包括需要某種形式網絡或通信接口的嵌入式系統。由于以太網成本低、幾乎無處不在,并且可以利用TCP/IP等互聯網協議連接互聯網,因此以太網是目前在嵌入式產品中應用最廣泛的網絡接口之一。根據目標應用的不同,網絡子系統的要求變化也相當大。簡單的遠程控制和監控應用只需要每秒數千比特的傳輸能力,而高端存儲或視頻應用則需要持續的千兆比特級的吞吐能力。

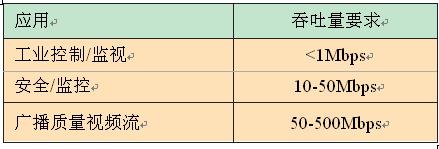

為簡單起見,我們將使用TCP載荷吞吐能力做為性能比較的主要指標。表1列出了一些典型應用以及相應的TCP/IP載荷吞吐能力要求。

表一:不同應用的網絡吞吐量要求

可配置的嵌入式網絡

基于FPGA的處理解決方案提供的強大靈活性允許您根據需要開啟或禁止處理器、IP內核以及軟件平臺的高級功能,并且可以對許多獨立參數進行精細調整,直到在軟件一級滿足應用的要求。此外,利用建模工具可以識別任何性能關鍵的軟件功能并將其分流至適當的硬件加速器或協處理器來完成。

讓我們來分別看一下可利用IP內核滿足典型應用性能要求的三種以太網子系統的例子。每種設計具有不同的系統架構:包括處理器配置、以太網 MAC IP配置以及存儲器接口。此外,這些例子還突出了可與這些硬件子系統配合使用的不同TCP/IP軟件協議棧。由于硬件構建模塊和軟件層都是可定制的,因此您可以根據應用的需要對這些系統進行增減。

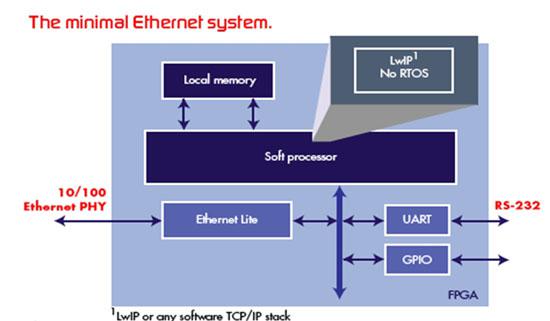

簡化以太網子系統

對于遠程監視或控制應用中所需要的簡單網絡接口來說,如圖3所示的最小化網絡子系統就足夠了。在此類應用中,TCP/IP性能要求較低(<1Mbps),因此LwIP(簡化版互聯網協議棧)這樣的小TCP/IP協議棧(不需要RTOS實時操作系統)就足夠了。

圖3:規模最小的以太網系統。

這可以使用不間斷的以太網Lite IP在簡單的查詢模式下實現。全部軟件,包括簡單的應用層,可全部存儲在FPGA中的本地存儲器中。如圖3中所示,其它需要的I/O接口,RS-232 UART和GPIO,可以增加到基本子系統中。

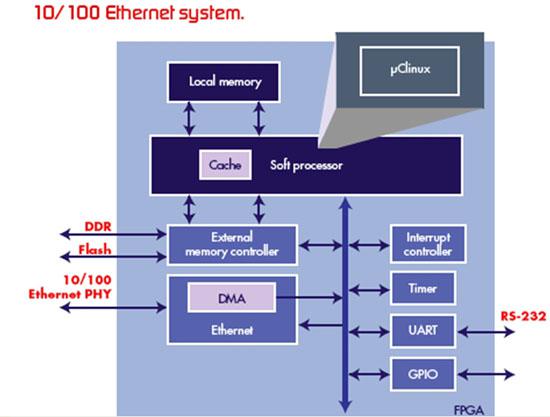

圖4:典型的10/100以太網系統架構。

通過對圖3中的最小系統做一定的修改,可以實現更高TCP/IP吞吐能力(10-50Mbps),并轉向如圖4所示的更為典型的10/100以太網解決方案。主要的變化有:

1. 為以太網MAC增加直接存儲器訪問(DMA)引擎,實現中斷驅動;

2. 為系統增加外部存儲器,為處理器增加緩存;

3. 更復雜的TCP/IP棧,如Linux(Clinux)系統TCP/IP協議棧。

對于需要100Mbps以上TCP/IP吞吐能力的應用,可以考慮硬IP或軟IP內核方式提供的三模式以太網MAC(圖5)。為獲得高端應用所需要的500Mbps以上的吞吐能力,需要像分散/匯聚DMA(SGDMA)等高級DMA技術,以及包括數據重排引擎(DRE)和校驗和卸載 (CSO)等FPGA硬件加速器技術。

為滿足千兆以太網對更高數據吞吐率的需求,可能需要更高性能的嵌入式(硬)處理器或FPGA上實現的可定制軟處理器,以及更大的緩沖容量、如16Kbit指令和數據緩存。就軟件平臺來說,Linux、VxWorks、Integrity和QNX等軟件平臺中的高級TCP/IP棧支持諸如零拷貝和校驗和旁路等功能。

包括硬件和軟件在內的許多因素都會影響到TCP性能,并進而影響系統TCP吞吐能力。這些因素包括:

1. 處理器,包括頻率、功能和緩存

a. 頻率:TCP/IP協議通常需要將載荷從用戶緩存拷貝到協議棧控制的緩存,然后再將其拷貝到以太網MAC的FIFO中去。這些存儲器拷貝操作有些是以軟件方式完成的,因此需要處理器的處理周期。同時處理器還參與TCP校驗和的計算,計算過程中需要將整個數據包從存儲器讀出。更快的處理器配合更快的存儲器能在更短的時間內完成這些操作,從而可以保持較高的數據速率;

b. 功能:TCP/IP協議棧需要對數據包的包頭和載荷進行訪問處理。做為包頭處理的一部分,典型的訪問包括讀取包頭信息的特定位。因此每個數據包的處理過程都需要相當多的移位操作。此外在處理每個數據包時都需要進行乘法操作。在可配置的處理器中,必須開啟完成移位或乘法的指令才能獲得更高的性能;

c. 緩存:數據包從以太網MAC被拷貝到存儲器中之后,將會通過TCP/IP協議棧的不同層。然后TCP/IP棧中的數據包處理代碼會被執行。將所有代碼和數據包讀到緩存中會大大提高處理器效率并提高以太網帶寬。

2. 存儲器

存儲器訪問時間和延遲對于系統性能有巨大的影響。典型應用中,TCP/IP應用并不存儲在本地存儲器中,程序和數據存儲在外部存儲器中。存取數據和指令所花費的時間對于性能有很大影響。存儲器因素通常與緩存大小有關。提高指令和數據緩存大小有助于減輕外部存儲器延遲和存取時間所帶來的影響。

3. 以太網MAC

在FPGA中實現的以太網MAC外設提供了很大的靈活性,特別是在工作模式(無DMA與SGDMA)、數據包FIFO深度、DRE支持、CSO支持以及超大幀支持方面。每一項都會影響到MAC所需要的資源,以及其能夠從處理器分流的功能多少,從而對整體性能造成影響。

4. TCP/IP協議棧

靈活的優化TCP/IP協議棧是影響系統性能的重要因素。對硬件CSO和零拷貝API(數據不需要從應用拷貝到協議棧緩存)以及可配置棧選項等TCP/IP棧功能的支持可幫助提高系統性能。

5. 信息多少

信息(應用數據)的大小是影響性能的另一個因素。隨著信息減少,TCP/IP協議頭(如TCP、IP和以太網頭)的開銷增加,從而會減小總體的數據載荷吞吐能力。

大多數應用對于成本、性能和功能都有一組基本的需求。當為特定應用設計產品時,設計人員必須在這些需求之間進行正確的折衷,然而,為了適應市場條件,這些要求在產品生命周期內可能會發生變化。采用靈活可配置的平臺能夠在不改變設計平臺或供應商的情況下根據需要對這些要求進行重新平衡。

-

處理器

+關注

關注

68文章

19485瀏覽量

231510 -

FPGA

+關注

關注

1632文章

21816瀏覽量

607041 -

嵌入式

+關注

關注

5096文章

19227瀏覽量

308679

發布評論請先 登錄

相關推薦

基于FPGA的32位嵌入式處理器的解決方案

基于FPGA的32位嵌入式處理器的解決方案

評論