1.引言

近年來全球范圍內出現了新一輪的太空探索熱潮,世界各主要航天大國相繼出臺了一系列雄心勃勃的航天發展規劃。空間技術的迅猛發展,使各種電子設備已經廣泛應用于人造衛星、宇宙飛船等設備中,在天然空間輻射環境中往往因經受空間輻射而導致性能降低或失靈,甚至最終導致衛星或空間飛行器災難性后果。因此,必須在輻照惡劣環境中的電子設備使用抗輻射的電子元器件。

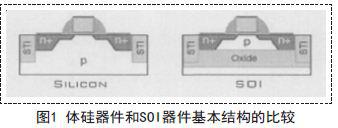

絕緣體上硅與體硅器件相比較,其獨特的絕緣層把器件和襯底隔開,減輕了襯底對器件的影響,降低了源漏極電容、消除了閂鎖效應、改善了短溝道效應以及熱載流子效應、提高了抗輻照性能等等,因此,SOI技術能夠成功地應用于抗輻射領域,其被國際上公認為“二十一世紀的硅集成電路技術”.SOI與體硅MOS器件結構的比較如圖1所示。

通常根據在絕緣體上的硅膜厚度將SOI分成薄膜全耗盡FD(Fully Depleted)結構和厚膜部分耗盡PD(Partially Depleted)結構。本論文中設計的SOI MOS器件是薄膜全耗盡結構的,這是因為薄膜SOI結構的器件由于硅膜的全部耗盡完全消除“翹曲效應”,且這類器件具有低電場、高跨導、良好的短溝道特性和接近理想的亞閾值斜率等優點。因此薄膜全耗盡FDSOI應該是非常有前景的SOI結構。

因此,對SOI MOS器件進行研究具有十分重要的意義。本論文將設計一個0.18μmH柵P-Well SOI MOS器件并對該器件進行電學特性仿真,通過仿真獲取閾值電壓和飽和電流這兩個重要參數。

2.設計0.18μmH柵P-Well SOI MOSFET

整個設計流程為:首先,使用SentaurusStructure Editor工具編輯器件的基本結構和設定注入粒子的類型和劑量;然后,在使用Sentaurus Structure Editor工具中的網格生成工具Mesh設置器件的網格參數;最后使用Sentaurus Device工具仿真器件的電學特性并測試。在這一部分,我將通過上述流程來設計一個0.18μmH柵P-Well SOI MOSFET器件。

對于器件結構的設計,器件結構的X和Y軸范圍分別為[-0.3,0.3]和[-0.3,0.3],Z軸的范圍為下面過程中設置的厚度的總和。

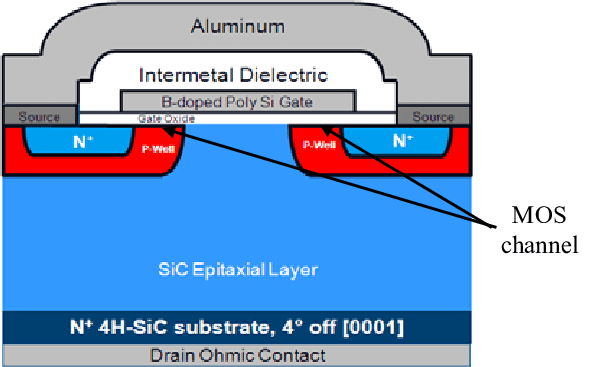

首先,畫一層0.2μm厚度的硅襯底,硅襯底上畫一層0.15μm厚度的絕緣氧化層,再在絕緣氧化層上畫一層0.1μm厚的硅層(即頂硅層);然后,在頂硅上放置一層0.005μm厚度的氧化層,氧化層上放置一層寬度為0.18μm,厚度為0.04μm的多晶硅柵層;最后,在柵的周圍放置側墻并定義接觸點。

經過上述過程,器件的基本結構已經完成。下面,往頂硅中注入劑量為1E+11cm-3的硼粒子來形成P-Well.在對源漏極進行注入粒子之前,需要先定義粒子注入的窗口,然后,設置注入粒子類型、峰值劑量、峰值位置和擴散長度。源漏極注入粒子參數如表1所示。

器件的結構和摻雜粒子的一些參數已經設置好,現在需要做的工作就是設置網格,這里設置了三個部分的網格,全局網格、頂硅層部分的網格和溝道處的網格。設置溝道處網格是因為仿真器件的電學特性時,粒子的傳輸主要是在溝道處,在溝道處設置合理的網格不僅會提高仿真精度,也能優化仿真速度。

設置完網格后,就可以通過生成網格把器件結構,摻雜信息,網格信息集成到一個網格文件中,進行器件電學特性仿真時需要用到這個文件。

器件的電學特性仿真,可以理解為半導體器件(比如,晶體管或則二極管)電學特性的虛擬測試。器件被看作為有限網格點構成的結構,結構中的每個點都包含著金屬類型、摻雜粒子類型和濃度等屬性。對于每個點,載流子濃度、電流密度、電場強度、電子空穴對的生成和復合速率等都要進行計算。

3.結果和分析

0.18μmH柵P-Well SOI MOSFET器件的結構和器件特性仿真如圖2到圖7所示。使用INSPECT工具顯示器件電學特性曲線,TECPLOT_SV工具顯示器件結構。這兩個工具都在Sentaurus TCAD軟件中。

圖2和圖3所示分別顯示了生成網格之前的器件結構和生成網格之后的最終器件結構。圖中顯示的有花紋的界面代表的是源極、漏極、柵極、襯底的接觸點,這些接觸點是為了器件特性仿真設置電壓參數的。圖中凹的地方是源極和漏極,凸的地方是H形柵極;按從上到下的順序看,下面3層結構分別為頂硅、絕緣氧化層、襯底。

需要對設計的器件做傳輸特性和輸出特性分析,結果如圖4和圖5所示。從圖中我們可以得到所設計器件的閾值電壓(Vth)為1.104V,飽和電流為3.121E-4A.

閾值電壓(Vth)是MOSFET最重要的參數之一,通常將傳輸特性曲線中輸出電壓隨輸入電壓改變而急劇變化轉折區的終點對應的輸入電壓稱為閾值電壓。當柵極上所加的電壓大于閾值電壓時,器件處于開通狀態;小于閾值電壓時,器件處于關閉狀態。

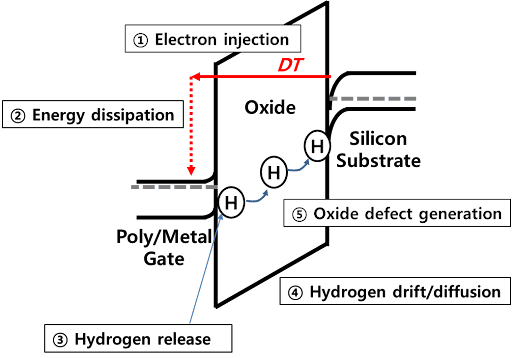

本文所設計的器件的閾值電壓為1.104V圖6中顯示了在不同輻照劑量條件下,器件閾值電壓的漂移。這是因為在輻照會產生總劑量效應,在MOS器件中總劑量效應主要是在氧化物中產生電荷以及在Si/SiO2界面產生界面態。即使在室溫條件下,SiO2中的電子也是可以移動的,它們能夠迅速離開氧化層;另一方面,陷在氧化物中的空穴會產生正氧化物電荷,該電荷會導致器件閾值電壓產生負漂移。同時,總劑量輻照也會也會在Si/SiO2界面產生界面態,與氧化物電荷作用相反,界面態會使閾值電壓增大。

4.總結

使用Sentaurus TCAD軟件成功設計了0.18μmH柵P-Well SOI MOSFET器件并進行了特性仿真。整個設計過程中用到了SentaurusTCAD軟件中的SDE和Sentaurus Device兩個主要工具,分析仿真結果得到了閾值電壓(Vth)和飽和電流(Idsat)兩個主要參數,參數值和理論相符合。

-

MOSFET

+關注

關注

150文章

8430瀏覽量

219368 -

仿真

+關注

關注

52文章

4252瀏覽量

135517 -

衛星

+關注

關注

18文章

1758瀏覽量

68294

發布評論請先 登錄

掃描電機的PID恒速控制仿真及實驗

虛擬仿真實訓室建設解決方案最新解析

為何必須通過TDDB(時間相關介質擊穿)方法檢驗國產SiC MOSFET的柵氧可靠性水平

光學實驗教具應用:邁克爾遜干涉儀實驗

SiC碳化硅MOSFET驅動電壓的限制源于柵氧可靠性與器件性能之間的權衡

做賊心虛:部分國產碳化硅MOSFET廠商“避談柵氧可靠性”的本質

做ros0小車仿真實驗室stp 文件免費獲取方法

什么是MOSFET柵極氧化層?如何測試SiC碳化硅MOSFET的柵氧可靠性?

既然MOSFET柵-源阻抗非常大,為什么設計驅動MOS電路的柵極電流還要大?1200字說清楚

教學驗證丨BUCK電路仿真驗證

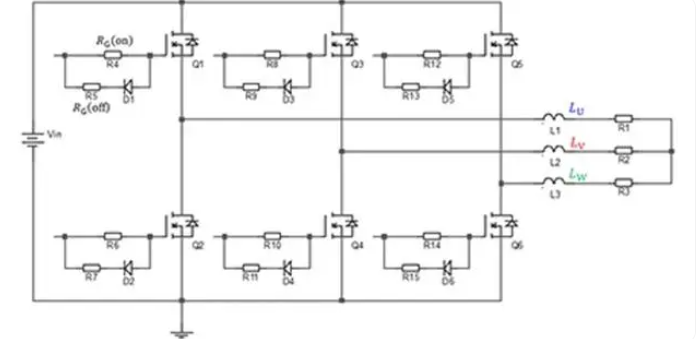

通過三相逆變電路比較PrestoMOS?與普通SJ MOSFET的效率(仿真)

通過軟件設計0.18μmH柵P-Well SOI MOSFET器件并進行仿真實驗

通過軟件設計0.18μmH柵P-Well SOI MOSFET器件并進行仿真實驗

評論