在以太網中,物理層芯片(Physical Layer Interface Devices,PHY)是將各網元連接到物理介質上的關鍵部件。負責完成互連參考模型(OSI)第I層中的功能,即為鏈路層實體之間進行位傳輸提供物理連接所需的機械、電氣、光電轉換和規程手段。其功能包括建立、維護和拆除物理電路,實現物理層比特(bit)流的透明傳輸等。物理層包括4個功能層和兩個上層接口。兩個上層接口為物理介質無關層接口(MII)和物理介質相關層接口(MDI),在MII的上層是邏輯數據鏈路層(DLL),而MDI的下層則直接與傳輸介質相連。而這些子層的正常工作都離不開一個穩定精確的時鐘同步信號。PLL在物理層芯片的時鐘同步應用中,要求其輸出時鐘帶寬覆蓋范圍廣,電壓控制頻率線性度好,頻譜純度高。在PLL設計過程中,VCO是最為關鍵的設計環節,其性能將直接決定PLL的設計工作質量。近年來,VCO相位噪聲得到越來越深入的研究,各種低噪聲VCO結構不斷涌現,文獻中提到的交叉耦合電流饑餓型VCO便是其中一種。電流饑餓是指電路單元的電流受到電流源的鉗制而不能達到其應有的最大值。本文在其基礎上采用了一種有效控制電壓變換電路,保證原有電路優點的同時擴展了線性度,提高抗噪聲能力,有效降低了相位噪聲。

1、VCO延遲單元工作原理

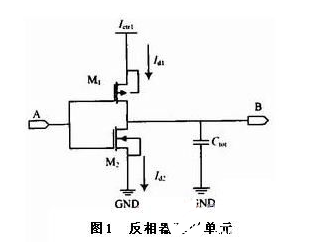

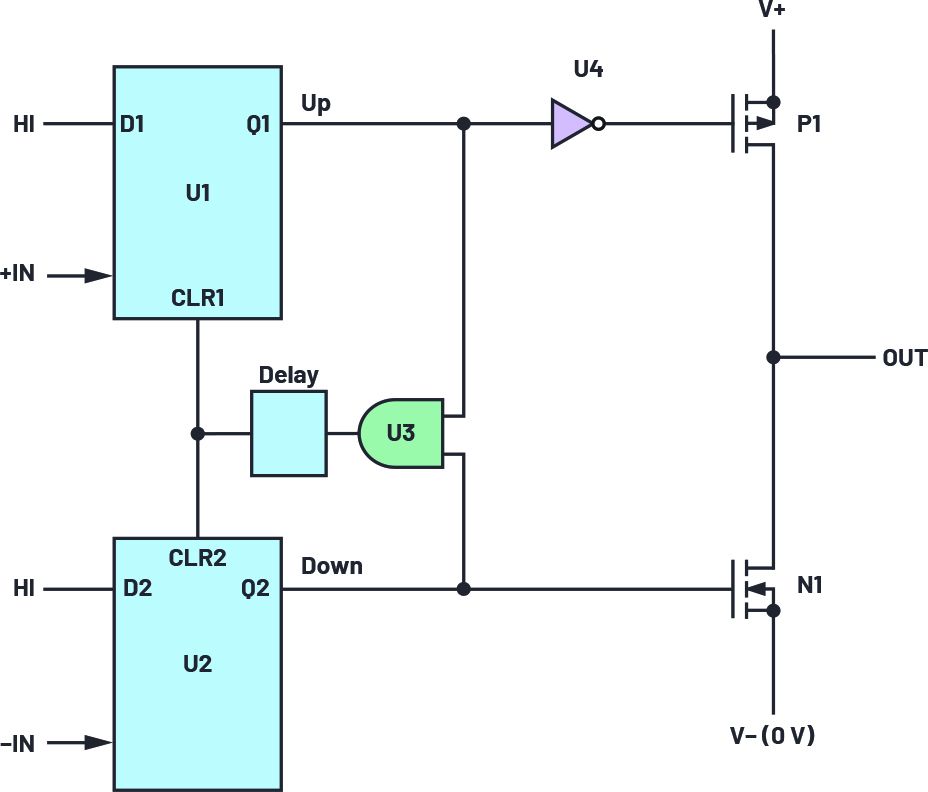

圖1所示為電流饑餓型VCO中的單級結構。PNP管M1和NPN管M2是延遲單元的組成部分,Ictrl是用于控制電容的放電電流Id1和充電電流Id2,他們是構成環形振蕩器的每一級。Ictrl控制著流過M1管和M2管的電流,所以由M1管和M2管構成的延遲單元處于電流饑餓狀態。每一級遲單元處于電流饑餓狀態。每一級的電流都由同一個電流源所鏡像,所以Id1=Id2同時電流大小由輸入控制電流Ictrl控制。

反相延遲主要是2個原因:一個是RC的充電時間;另一個是反相器的預置電壓。而這2個延遲時間的產生都是可以通過調整寬長比來實現。環形反相的次數必須是奇數,這樣電路才不會鎖定導致振蕩失敗。而差動結構的振蕩器級電路數可以是偶數,只要將其中的一級接成不反相的。這種靈活性是差動電路優于單端電路的一個優點。

2、電流饑餓型VCO

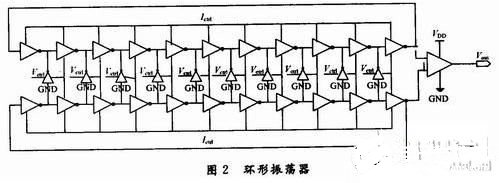

如圖2所示VCO由11級單端反相延時單元組成的差分電流饑餓型環型振蕩器結構,11級差分反相延遲單元,交叉耦合輸出結構轉為單端輸出,其振蕩電壓可達到全擺幅。交叉耦合、柵極接地的P管,在兩個環之間加入一個反相器,使它們的輸出信號相位差為180°。為了在上電的時候能立即使兩個振蕩器同步并保持180°的輸出相差,這兩個門的尺寸必須設得比較大以便有足夠大的驅動能力。這種結構能夠有效地抑制環境噪聲包括電源和襯底噪聲的影響,因此具有良好的抗噪能力。在設計環型振蕩器時,應充分考慮每級輸入輸出點的電容負載,保證每一級的延時都相同,這樣每個輸入輸出點的振蕩頻率才能相同。

此外,由于溝道長度L決定了最大工作頻率,因此在滿足最大工作頻率指標的條件下應盡可能增加溝道長度以減少電路對工藝參數的敏感程度,即使在最壞情況下仍能保證電路正常工作。第一級反相器的控制電流來自于PLL中RC濾波器的輸出電壓轉換過來的。在設計反相器的寬長比時要保證有足夠大的控制電流調節范圍,同時也要使溝道長度足夠長以消除短溝道效應。反相器MOS管的襯底與濾波器電容接同一個參考地電位,這樣可以保證PMOS管和NMOS管不受接地噪聲的影響。在與控制支路平行的電流通路中,NMOS管是長溝道管,它為VCO提供小的偏置電流,保證了當控制管工作在亞閾值狀態時振蕩器仍能振蕩。反相器電容管連接在虛地線與VDD之間,其作用等效一個電容,它能有效地限制虛地線的電壓波動,從而增強VCO的抗噪聲能力。如果需要較大的電容值,可以通過多管并聯的方法得到。但是該電路需要設計一個良好的電壓/電流轉換電路,即控制電壓變換電路。

3、控制電壓交換電路

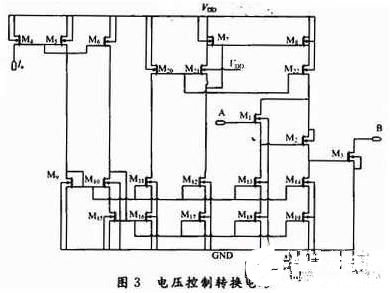

控制電壓變換電路如圖3所示,該電路的工作原理是在保持振蕩器控制電流范圍不變的情況下對RC濾波器的輸出電壓,即變換電路的輸入電壓進行成比例縮放。這樣使得振蕩控制支路在臨界飽和工作狀態下能夠提供更大的控制電流,從而改善高頻區域的線性度,增大VCO的線性覆蓋頻率范圍。在圖3中,控制管M1是做阻抗變換,M2,M3用于電壓的放大,第一級反相放大管采用PMOS管的形式放大很小的電壓,M3管是第二級反相放大NMOS管。這樣可以保證輸出電壓跟輸入電壓是具有同相功能。該控制電壓變換電路的偏置電路采用共源共柵結構,完全適用于低壓電路。該結構不僅增強變換電壓對電源,工藝,溫度依賴性,輸出電流噪聲的干擾能力,同時抑制了電源噪聲對VCO輸入電壓的影響。 M1,M13,M18管組成了低壓共源共柵結構,這時M1管的柵電壓為(Vth+2Vds),該電壓由M18和M22管組成的偏置支路提供。通過隔離控制管和振蕩器控制電流,可以進一步抑制振蕩器產生的電壓振蕩對控制管的影響,降低了控制電流的波動,從而減小了VCO輸出的頻率抖動,大大降低了VCO輸出的相位噪聲,有效地提高了VCO輸出的頻譜純度。

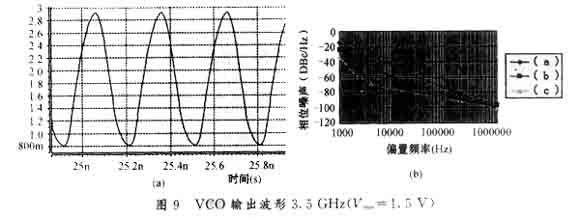

4、仿真結果

該電路的電源電壓為2.5 V,使用Spectre仿真工具,VCO電路得到的輸出頻率與控制電壓特性曲線和相噪特性曲線結果如圖4和圖5所示。圖4為VCO的輸出相位噪聲曲線,可見低頻的1/f噪聲得到了很好地抑制。在偏離中心頻率600 kHz處的相位噪聲為-108 dBc/Hz。圖5為VCO的輸出頻率與控制電壓特性曲線表明,VCO的控制電壓調節范圍是0.6~2.0 V,線性區頻率覆蓋范圍是60~480 MHz,壓控增益為300 MHz/V,滿足了以太網物理層芯片的時鐘頻率要求。表1給出了整個VCO的性能參數指標。

5、結語

本文設計了一個適用于以太網物理層芯片時鐘同步PLL的高寬帶低噪聲VCO,采用了具有良好抗噪能力的交叉耦合電流饑餓型差分環形振蕩器。仿真結果表明,在同樣輸入噪聲和環境噪聲的情況下,本文的VCO中心頻率為250MHz時,壓控增益線性區頻率覆蓋范圍是60~480MHz,在偏離中心頻率600 kHz處的相位噪聲為-108 dBc/Hz,較文獻中傳統的反相器延遲單元的環形VCO性能有明顯的改善。說明了改進后的電路具有較寬的頻率調節范圍,較好的線性度和較低的相位噪聲,完全滿足以太網物理層芯片時鐘同步PLL的性能要求。

責任編輯:gt

-

芯片

+關注

關注

459文章

52308瀏覽量

437929 -

電流

+關注

關注

40文章

7121瀏覽量

134450 -

以太網

+關注

關注

40文章

5605瀏覽量

175148

發布評論請先 登錄

ADI推出全新四頻段VCO 提供更低相位噪聲及低水平電流消耗

關于ADF4351開環VCO相位噪聲測試問題

如何用交叉耦合電流饑餓型VCO設計實現降低時鐘頻率的相位噪聲?

交叉耦合模型及其在腔體濾波器中的實現

高速低相位噪聲VCO設計

基于交叉耦合的同軸腔雙工器設計

分析交叉耦合軸承力給渦輪增壓器設計帶來的影響

ADI四頻段VCO是如何做到兼具低相位噪聲和寬帶頻率?

交叉耦合電流饑餓型VCO設計實現降低時鐘頻率的相位噪聲

交叉耦合電流饑餓型VCO設計實現降低時鐘頻率的相位噪聲

評論