前言

最近有網友對小編說:xilinx時序收斂完全不會用,不知道工具在干啥,一直都在瞎點,報告一直是瞎看。

好消息是,Xilinx發布了一篇新文檔ug1292。這個文檔把ug949中時序收斂的相關內容單獨提取出來,用最簡練的語言介紹了時序收斂的方法。ug1292是時序收斂的一個快速參考手冊,也就是看完之后你可以快速知道怎么用工具實現時序收斂。

UG1292百度云鏈接:

鏈接:https://pan.baidu.com/s/1FOZCRzDogrGeuIMDXkaeaA

提取碼:gku9

ug1292 總體了解

這個手冊只有十頁內容,一天就可以看完,每一頁都有流程圖或表格都可以指導使用者更好的操作。該手冊每一頁都是一個章節,哪個地方不懂直接翻到該頁仔細看,建議看英文原版,目錄翻譯如下:

手冊目錄

第1頁——初始設計檢查流程

第2頁——時序基線流程

第3頁——分析建立時間違規流程

第4頁——保持時間違規解決

第5頁——減少邏輯延時流程

第6,7頁——減少網絡延時流程

第8頁——改善時鐘偏斜流程

第9頁——改善時鐘不確定性流程

第10頁——FAILFAST報告概覽

從目錄和內容其實可以看出來,xilinx的理念是——一切問題盡量在設計初期干預。越是在設計初期考慮的全面,后期的工作會越順利,也就是時序是設計出來的,不是測試出來的!所以前期多花時間設計好時序,可能最開始進度慢一些,但是后期會避免很多不必要的問題。如果前期設計的不周全導致后期項目不停打補丁而導致維護成本增加得不償失。所以各位老司機設計前期請慎重,后期各種問題堆起來可能根本就解決不了,就算能解決,后面接手維護的人內心也只能吶喊:臣妾做不到啊!!

設計期初可以從以下角度去考慮時序方面的問題:

初始設計檢查

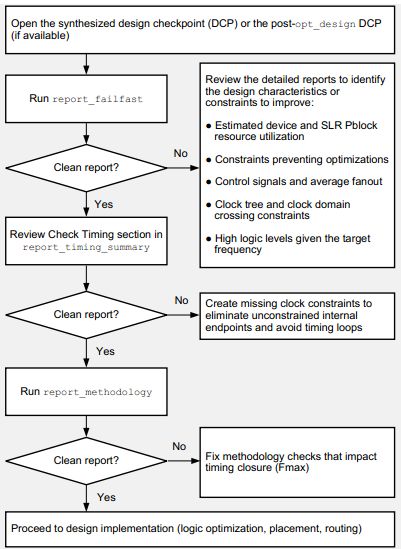

UG1292第一頁是針對綜合后或者opt_design階段的使用說明。vivado的基本流程有5步(其實不同策略可以更多,具體使用方法和好處以后講),分別是synth_design, opt_design, place_design, route_design, write_bitstream,除了最后生成bit外每一步都可以生成一個時序報告,幫助分析定位問題或者優化設計做出指導。而UG1292第一頁是講opt_design階段如何去利用vivado提供的工具和報告分析和定位問題的。

UG1292初始設計檢查流程圖

簡單地說只需要下面幾步。

初始設計檢查步驟

1.opt_design階段生成的dcp(design check point)

2. 用report_failfast生成failfast報告

3. 用report_timing_summary生成時序報告

4. 用report_methodology可以生成UFDM報告

failfast報告作用

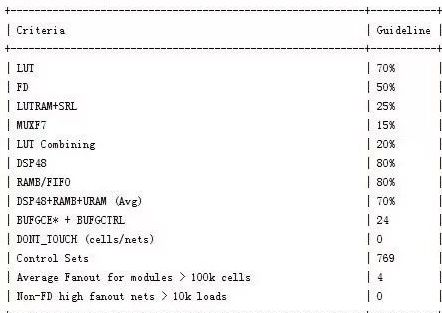

failfast作用是給出各類資源利用率的推薦上限和實際上限比值,根據這兩個比值的對比可以知道哪里是時序的瓶頸,需要自己去檢查的。下面是K7某個芯片各個資源的推薦利用率:

如果某項實際使用指標超過了指導指標,在status一欄(Guideline旁邊一欄沒有截圖出來)里面會有REVIEW的字樣,表示這里你要檢查下,這里會對時序有一定影響需要你人為去評估,但是不以為著一定要改。比如DONT_TOUCH約束推薦是一條都不要用,然而有的特殊情況處理,人是有把握比機器更好的,所以為了不讓編譯器去修改,就加這條約束,但是編譯器不確定你是否有能力把握,或者是否注意到這一點,所以會提示你,如果你的設計需要必須這樣,并且有把握那么可以不做任何修改的。

時序報告作用

這里生成的時序報告看路徑延遲之類的是沒有任何意義的,因為還沒有布局布線。這里主要檢查以下幾點。

check_timing下面有沒有未約束路徑,loop有沒有,已經約束的是否合理,比如本來是125M時鐘實際約束是120M。

異步時鐘域路徑約束是否合理。

UFDM報告

UFDM(UltraFast Design Methodology)報告主要作用是報告RTL級代碼檢查,IP使用分析等方面的報告,主要關注報告里面Bad Practice的項目即可。

-

芯片

+關注

關注

459文章

52331瀏覽量

438301 -

ug1292

+關注

關注

0文章

3瀏覽量

2377

原文標題:時序收斂官方文檔UG1292解讀之一

文章出處:【微信號:HaveFunFPGA,微信公眾號:玩兒轉FPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

ImageCraft ICCAVR 的中文使用說明

如何安裝ug5.0以及ug5.0怎么安裝

PCA9685使用說明

ug1292時序收斂快速參考手冊

ug1292深度解析

深度解析ug1292:降低布線延遲

DC1292A DC1292A評估板

UltraFast設計方法時序收斂快捷參考指南(UG1292)

UG1292使用之初始設計檢查使用說明

UG1292使用之初始設計檢查使用說明

評論