當(dāng)設(shè)計出現(xiàn)布線擁塞時,通常會導(dǎo)致布線延遲增大,從而影響時序收斂。布線擁塞程度可通過如下兩種方式獲取:

-布線階段的log文件中會顯示擁塞程度

-對于place_design或route_design生成的dcp文件,可通過如下命令獲取

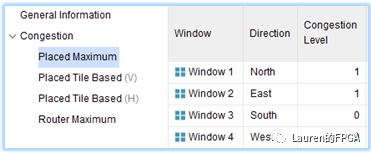

生成的擁塞報告如下圖所示。要格外關(guān)注擁塞程度(Congestion Level)大于4的區(qū)域。

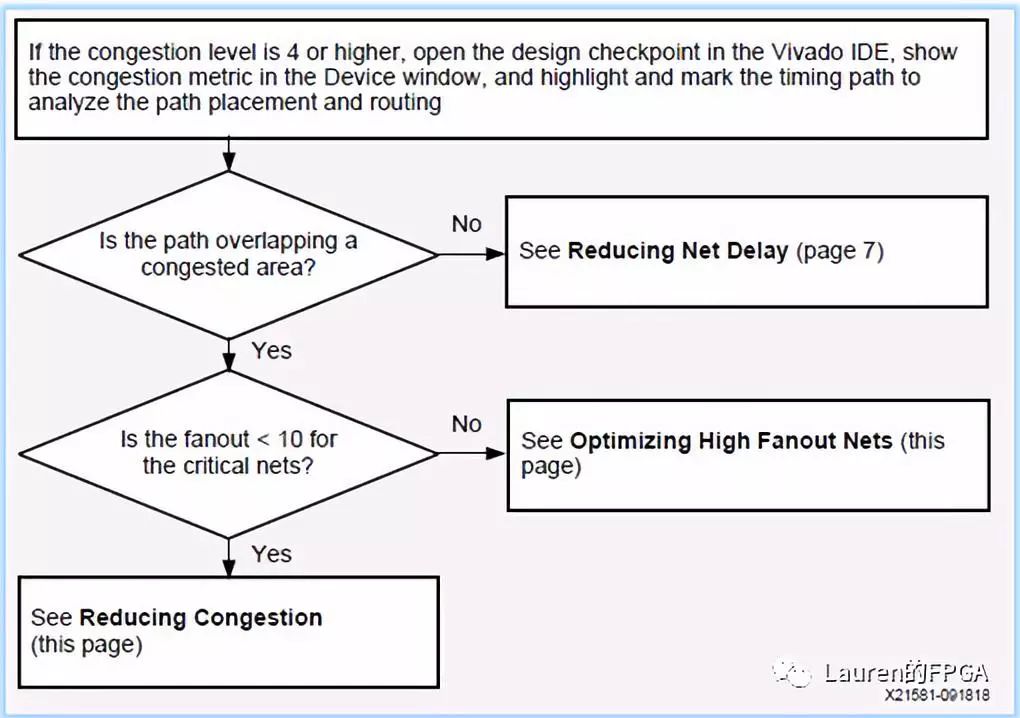

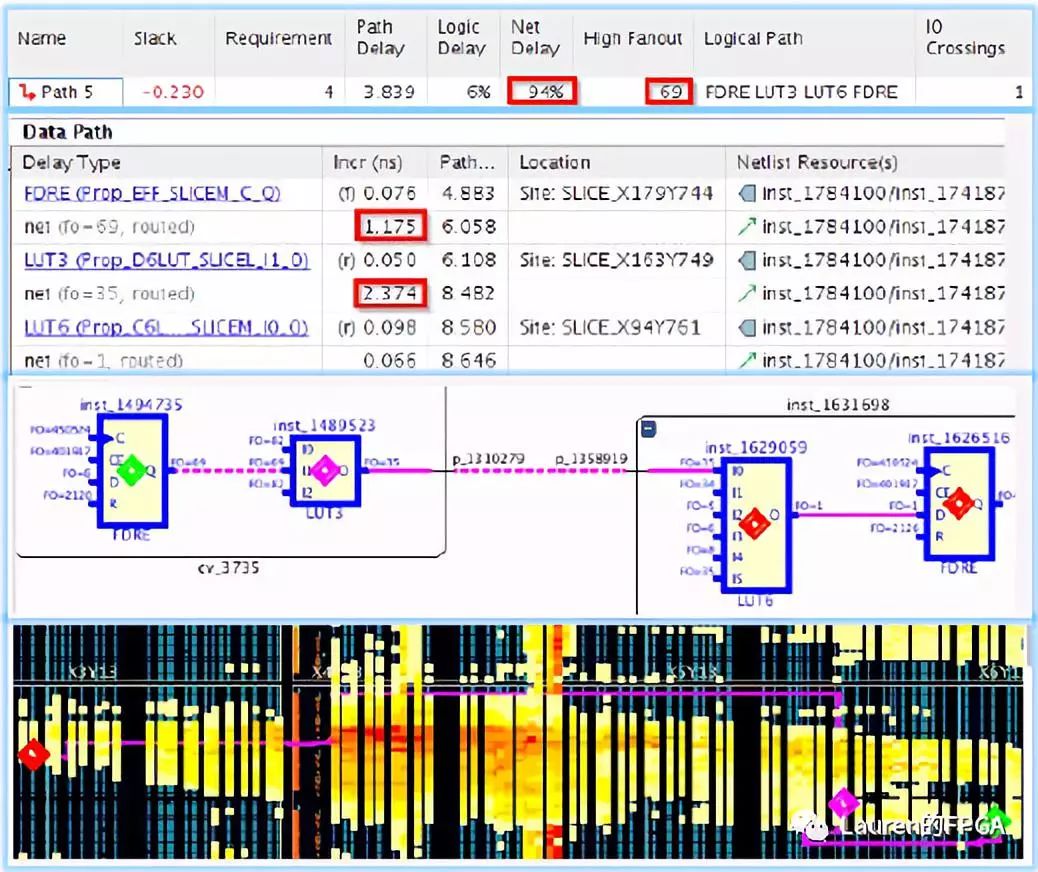

對于擁塞程度大于4的情形,可采用如下流程加以改善并降低布線延遲。在如下的案例中,可以看到布線延遲占到了總延遲的94%,據(jù)此,可斷定布線延遲是導(dǎo)致時序違例的根本原因。從布線結(jié)果看,在擁塞區(qū)域出現(xiàn)了繞線。

圖片來源:page 6, ug1292

圖片來源:page 6, ug1292

降低擁塞程度可改善布線質(zhì)量。Xilinx建議采用如下方法以改善布線擁塞。

(1)當(dāng)整體資源利用率達(dá)到70%~80%時(對于多die芯片,這個數(shù)值是指每個SLR的資源利用率),需要砍掉一些模塊以降低資源利用率。尤其要避免LUT/BRAM/DSP/URAM利用率同時出現(xiàn)大于80%的情形。如果BRAM/DSP/URAM這些Block利用率無法降低,那么要確保LUT利用率低于60%。

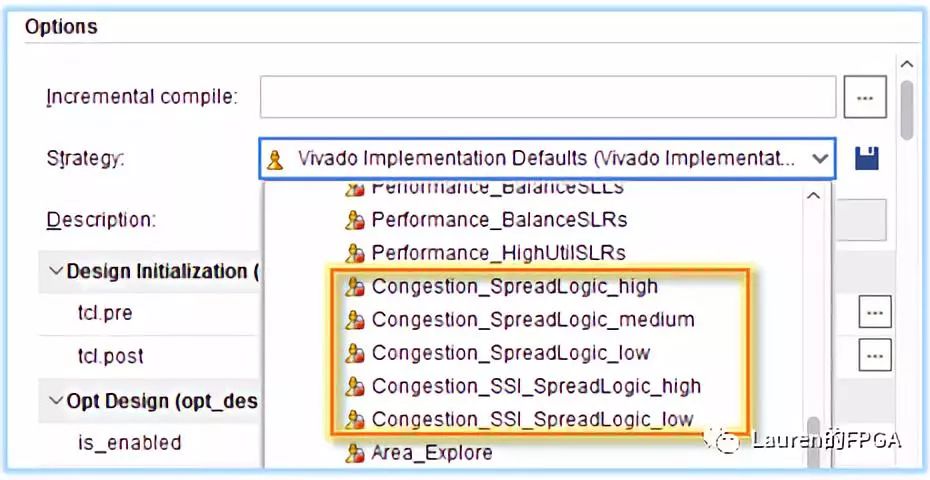

(2)執(zhí)行place_design時,嘗試將-directive設(shè)置為AltSpreadLogic*或SSI_Spread*或?qū)mplementation的策略設(shè)置為Congestion_*,如下圖所示。

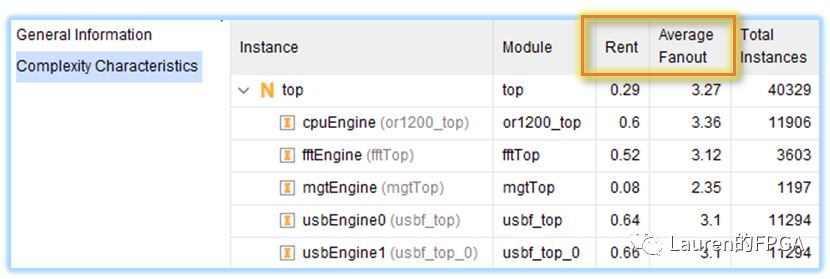

(3)通過如下命令分析設(shè)計復(fù)雜度,找到設(shè)計中出現(xiàn)擁塞的模塊(Rent值大于0.65或AverageFanout大于4)。之后,對這些模塊實施模塊化綜合,其中的綜合策略設(shè)置為ALTERNATE_ROUTABILITY。

生成設(shè)計復(fù)雜度報告:

對擁塞模塊采用模塊化綜合技術(shù):

(4)降低擁塞區(qū)域MUXF*和LUT-Combining的使用率,具體方法有時可通過report_qor_suggestions獲得。但采用模塊化綜合技術(shù)是一個值得一試的方法。

(5)在布線區(qū)域內(nèi)非關(guān)鍵的高扇出網(wǎng)線上引入BUFG,可通過如下命令實現(xiàn)。

(6)從之前低擁塞的布線或布局結(jié)果中繼承DSP/BRAM/URAM的布局。這可通過如下腳本實現(xiàn)。

優(yōu)化高扇出網(wǎng)線:

(1)在RTL層面,基于設(shè)計層次復(fù)制寄存器降低扇出,或者在opt_design階段通過-hier_fanout_limit選項降低扇出。

(2)在phys_opt_design(布局之后)階段通過-force_replication_on_nets對關(guān)鍵的高扇出網(wǎng)線通過復(fù)制寄存器降低扇出。

-

布線

+關(guān)注

關(guān)注

9文章

797瀏覽量

84986 -

ug1292

+關(guān)注

關(guān)注

0文章

3瀏覽量

2377

原文標(biāo)題:深度解析ug1292(6)

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術(shù)驛站】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

深度解析降低EMI的辦法

怎么降低延遲?

AUTOSAR架構(gòu)深度解析 精選資料推薦

AUTOSAR架構(gòu)深度解析 精選資料分享

C語言深度解析

LM1292 pdf,LM1292 datasheet

ug1292時序收斂快速參考手冊

ug1292深度解析

深度解析ug1292建立時間違例分析流程

淺談ug1292中的降低邏輯延遲的解決方案

UG1292使用之初始設(shè)計檢查使用說明

DC1292A DC1292A評估板

AD1292R芯片手冊

UltraFast設(shè)計方法時序收斂快捷參考指南(UG1292)

深度解析ug1292:降低布線延遲

深度解析ug1292:降低布線延遲

評論