研究機(jī)構(gòu)IMEC已經(jīng)發(fā)表了一篇論文,該研究表明,在5nm節(jié)點(diǎn)上,STT-MRAM與SRAM相比可以為緩存提供節(jié)能效果。這種優(yōu)勢(shì)比非易失性和較小的空間占用更重要。

半導(dǎo)體行業(yè)著名機(jī)構(gòu)IMEC在加利福尼亞州舊金山舉行的國(guó)際電子器件會(huì)議(IEDM)上發(fā)表了大量論文。

在關(guān)于5nm嵌入式MRAM的論文中,IMEC使用經(jīng)過(guò)硅驗(yàn)證的pMTJ(SSDFans作者蛋蛋命名MTJ為茅臺(tái)酒)緊湊模型進(jìn)行了設(shè)計(jì)分析,該模型與5nm節(jié)點(diǎn)兼容。對(duì)于讀寫操作,pMTJ稱訪問(wèn)延遲分別小于2.5ns和7.1ns。分析表明,STT-MRAM滿足了高性能計(jì)算中一級(jí)到三級(jí)緩存的眾多要求,并且讀寫性能顯著高于SRAM。它滿足了超過(guò)100MHz的時(shí)鐘頻率的要求,同時(shí)占用面積為SRAM的43.3%。

IMEC進(jìn)行了設(shè)計(jì)技術(shù)協(xié)同優(yōu)化(DTCO),以確定5nm節(jié)點(diǎn)上STT-MRAM單元的要求和規(guī)格,并得出了一個(gè)結(jié)論,高性能STT-MRAM位單元的MRAM間距是45nm接觸柵極間距的兩倍,是5nm最后一級(jí)高速緩存的首選解決方案。在第二步中,在300mm 硅晶片上制造高性能STT-MRAM單元,并通過(guò)實(shí)驗(yàn)測(cè)量磁隧道結(jié)的特性。

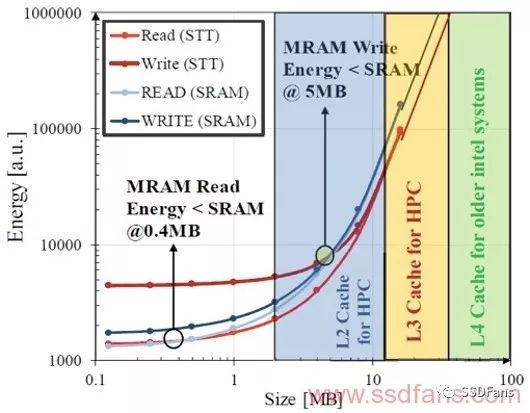

通過(guò)改變高速緩存大小,對(duì)SRAM和STT-MRAM進(jìn)行能耗比較。在0.4MB時(shí)的讀操作和5MB時(shí)的寫操作的情況下,與SRAM相比,STT-MRAM的能耗更低。資料來(lái)源:IMEC。

通過(guò)對(duì)SRAM和STT-MRAM的能耗曲線的觀察,研究人員認(rèn)為有兩個(gè)交叉點(diǎn)會(huì)影響系統(tǒng)能耗:STT-MRAM的讀和寫能耗分別在在0.4MB和5MB時(shí)低于SRAM。這是由于隨著SRAM容量的增加,SRAM待機(jī)功率呈指數(shù)增長(zhǎng)。

研究人員得出結(jié)論,即使SST-MRAM存在讀寫不對(duì)稱,但在5nm節(jié)點(diǎn)和高速緩存容量低于12MB時(shí),無(wú)論在何種應(yīng)用場(chǎng)景下,STT-MRAM都是有好處的。

IMEC項(xiàng)目主管Gouri Sankar Kar在一份聲明中說(shuō),“DTCO和硅驗(yàn)證模型讓我們首次得出了這樣的結(jié)論,在容量分別大于0.4MB和5MB時(shí),STT-MRAM的讀寫能耗均比SRAM小;STT-MRAM的延遲足以滿足高性能計(jì)算領(lǐng)域中最后一級(jí)緩存的要求,這些緩存的工作頻率約為100MHz。“

我們應(yīng)該考慮到MRAM會(huì)進(jìn)一步改進(jìn),這些MRAM現(xiàn)在已經(jīng)從研究領(lǐng)域中出現(xiàn)并且顯示出優(yōu)越的特性。

-

嵌入式

+關(guān)注

關(guān)注

5124文章

19434瀏覽量

312927 -

MRAM

+關(guān)注

關(guān)注

1文章

236瀏覽量

32074

原文標(biāo)題:IMEC:MRAM比SRAM更適合做緩存

文章出處:【微信號(hào):SSDFans,微信公眾號(hào):SSDFans】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

STT-MRAM新型非易失性磁隨機(jī)存儲(chǔ)器

5nm節(jié)點(diǎn)上為什么STTMRAM比SRAM更好?

具有28nm CMOS的1Gb 1.2V DDR4 STT-MRAM的產(chǎn)品化和優(yōu)異的性能

STT-MRAM的相關(guān)資料下載

你知道在5nm節(jié)點(diǎn)上, STT-MRAM與SRAM相比可以為緩存提供節(jié)能效果?

MRAM緩存可行性比SRAM更高

什么是STT-MRAM,關(guān)于STT-MRAM的作用以及應(yīng)用

高通研發(fā)出內(nèi)嵌STT-MRAM的邏輯芯片

STT-MRAM高密度低能耗技術(shù)

在5nm節(jié)點(diǎn)上, STT-MRAM與SRAM相比可以為緩存提供節(jié)能效果

在5nm節(jié)點(diǎn)上, STT-MRAM與SRAM相比可以為緩存提供節(jié)能效果

評(píng)論