工作中第一次感受到上電順序的重要性還是在羅禮電腦,我那個時候還是一名PE,也就是產(chǎn)品工程師,負責(zé)產(chǎn)線的制程分析改善和不良品維修。有一天早上,剛剛到辦公室,生產(chǎn)線就發(fā)生了緊急事件,有一個測試工位連續(xù)燒了三塊主板,這可不得了,那個年代一塊Intel-440BX的主板要買1300塊,我那時一個月工資也才1300塊啊。

Figure1被燒毀的南橋芯片

我把三塊燒毀的板子拿過來分析,發(fā)現(xiàn)三塊板子的南橋芯片也就是上圖中的82371芯片都有明顯的被燒焦的痕跡,芯片表面燒的面目全非,看著有點毛骨悚然,當(dāng)時的照片我沒有拍下來(那時候沒有智能手機^_^),但是情形和圖2基本一樣。

Figure2芯片的燒毀痕跡

排查這類問題的過程其實和警察查案子類似,我們也查“人證”和“物證”:

01先“查人”

三塊板子燒毀都是在同一個測試工位,也就是說由同一個測試人員產(chǎn)生,其他相同的測試工位沒有發(fā)生這樣的事件,我們發(fā)現(xiàn)此站工位的作業(yè)員比較瘦小,每次插拔ATX PowerCable時,由于胳膊力氣小,需要左右兩邊連續(xù)做上下晃動,才能拔出或插入,有點像是利用省力杠桿的原理,而其它工位的作業(yè)員則是直接一次性垂直上下插入和拔出。

Figure3ATX電源連接器

02再“查物”

也就是芯片,三塊板子燒毀的芯片位置都是南橋芯片。我們從南橋芯片82371的Datasheet里面獲得了上電順序的要求:

“

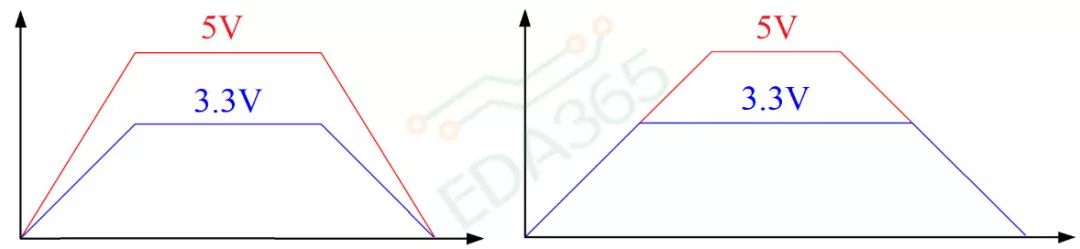

1)上電– 5V要比3.3V先上電,或者二者同時

2)下電– 5V要比3.3V后掉電,或者二者同時

Figure482371上電和下電順序要求

原因分析:

此工位的作業(yè)員在插拔ATX電源的時候,由于胳膊的左右晃動造成南橋芯片的上電/下電順序被破壞,導(dǎo)致燒毀。我們更換了作業(yè)員,并且進行作業(yè)指導(dǎo)培訓(xùn)后就再也沒有出現(xiàn)過芯片燒毀的情況。

雖然我們沒有做過實際的測試,但是很多大牛的文章里面都在描述,芯片的上電順序不滿足的話比較危險,要么發(fā)生即時故障,要么影響芯片的長期穩(wěn)定性,我們來列舉幾個可能發(fā)生的情況:

01

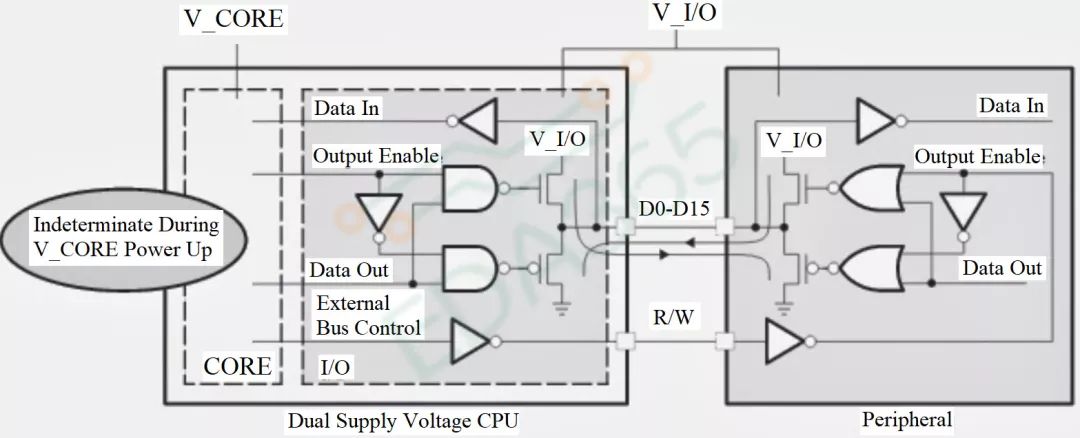

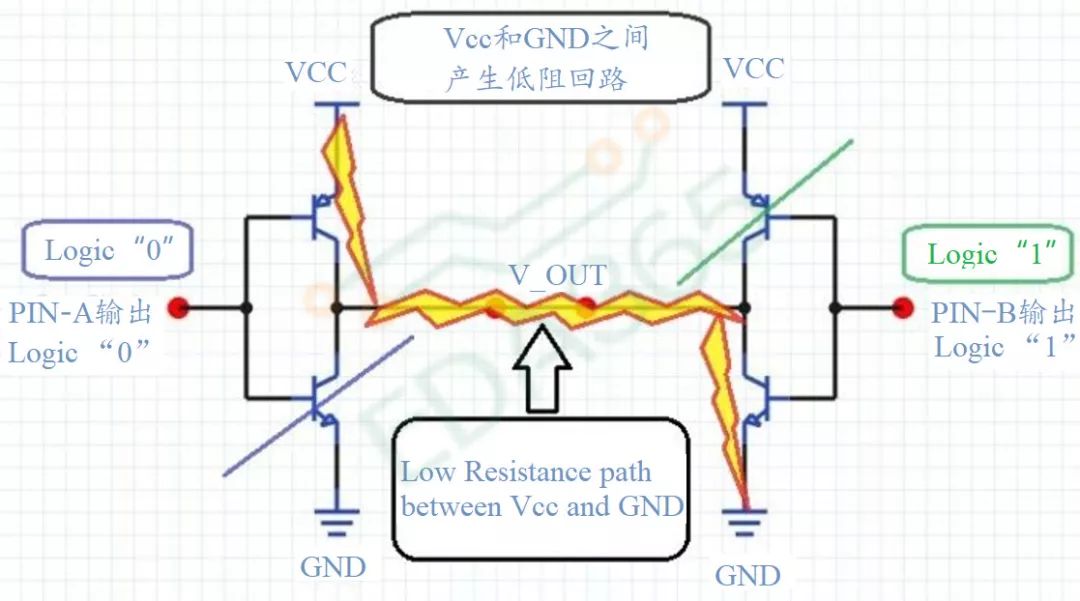

如圖5所示,左邊的CPU有兩路電源,即V_CORE和V_IO,右邊的芯片和CPU共用V_IO,兩顆芯片之間通過雙向數(shù)據(jù)總線接口相連,也就是所謂的“BidirectionalDatabus”,在這個系統(tǒng)里面,我們需要V_CORE先上電,然后V_I/O再上電,否則的話很容易出現(xiàn)CPU和I/O同時往數(shù)據(jù)線上發(fā)送數(shù)據(jù),產(chǎn)生圖6的情況,此時我們看到在VCC和GND之間產(chǎn)生了一個低阻回路,很容易損壞甚至燒毀芯片。

Figure5系統(tǒng)有一顆雙電源的芯片

Figure6BusContention產(chǎn)生的低阻回路

需要提一下,圖5的上電順序(先V_CORE-后V_IO)不是絕對的,有的CPU要求先V_IO后V_CORE,根據(jù)接口類型,工藝,設(shè)計廠家的不同,上電/下電順序要求也不一樣。

02

Latch-up

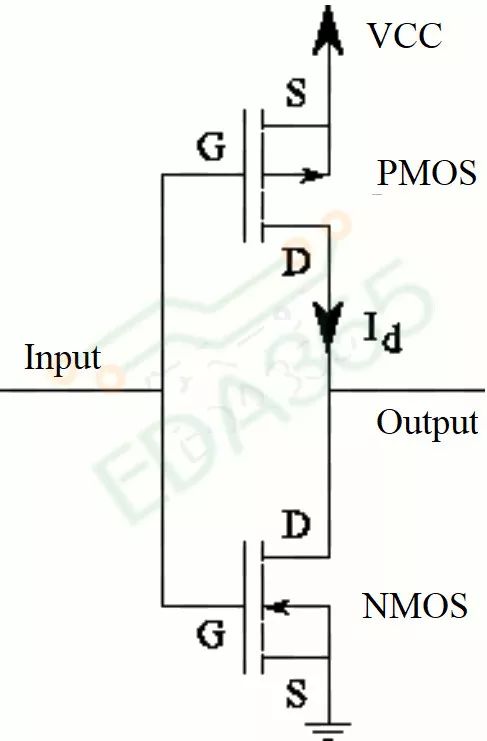

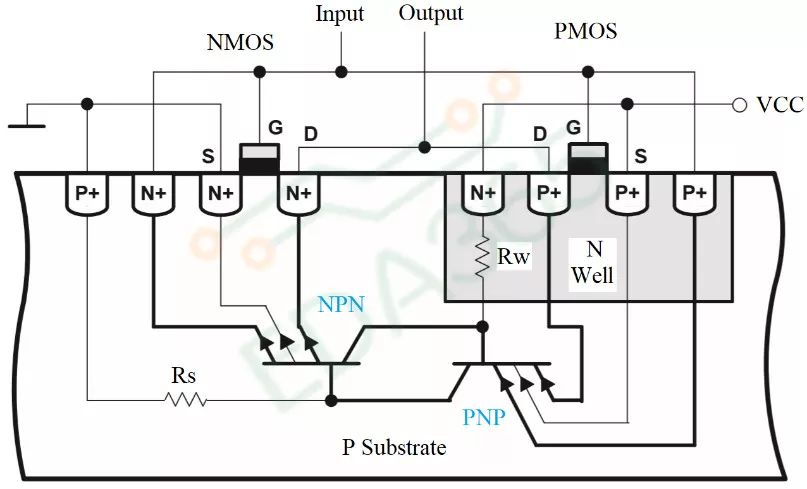

Latch-up的中文名叫閂鎖,有很多文章也都提及這個概念,我們先來簡單描述一下CMOS電路的常用一個基本電路單元如下圖(a),(b)圖是相對應(yīng)的芯片物理連接。

(a)

(b)

Figure7Latchup示意圖

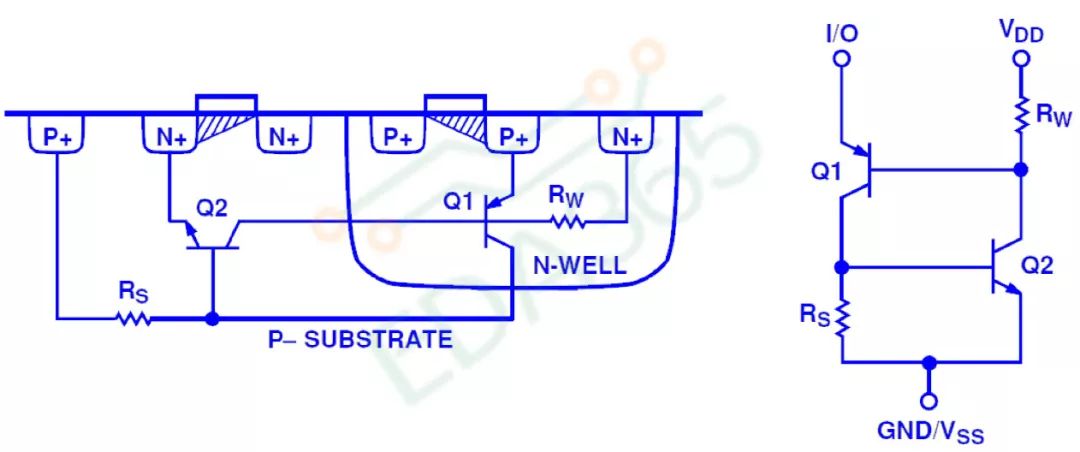

我們發(fā)現(xiàn)多了兩個器件,也就是我們看到的NPN和PNP,它們是怎么形成的呢?我們從圖中看到是來自不同的MOSFET的P和N之形成了雜散的PNP和NPN,我們把這些管子叫做SCR ( Silicon-Controlled Rectifier ),為了更加清楚的描述SCR,我們用另外一張簡圖來表示:

Figure8SCR

根據(jù)圖8,我們看到SCR是一個帶有正反饋的不穩(wěn)定結(jié)構(gòu),正常情況下SCR是不導(dǎo)通激活的,但是凡事都有例外,我們來看看如果下面這種情況:

“

1)Q2的Base上面有正向外部電流擾動注入,Q2導(dǎo)通;

2)Q2導(dǎo)通,使得Q1的Base電壓降低,促進Q1導(dǎo)通;

3)Q1導(dǎo)通,使得Q2的Base電壓抬高,Q2進一步導(dǎo)通;

4)Q1和Q2都進入飽和導(dǎo)通狀態(tài),電源和地低阻建立。

案例總結(jié):

隨著芯片的集成度越來越高,所需要的電壓種類也越多,對上電順序的需求也越來越復(fù)雜,我們在設(shè)計時需要仔細閱讀Datasheet里面的關(guān)于Powersequence的需求,這樣設(shè)計出來的產(chǎn)品才能更加穩(wěn)定,有時候我們有僥幸心理,覺得上電順序無關(guān)緊要,事實上運氣好在研發(fā)階段可能確實不會有什么問題,但是到了后期量產(chǎn)和交付客戶使用,會發(fā)生什么事情就不可控了,尤其是消費電子產(chǎn)品,林子大了什么鳥都有啊。

-

芯片

+關(guān)注

關(guān)注

459文章

52252瀏覽量

436830 -

電路

+關(guān)注

關(guān)注

173文章

6022瀏覽量

174543 -

上電

+關(guān)注

關(guān)注

0文章

16瀏覽量

11029

原文標(biāo)題:上電順序知多少?

文章出處:【微信號:eda365wx,微信公眾號:EDA365電子論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

上電順序知多少?論上電順序的重要性

上電順序知多少?論上電順序的重要性

評論