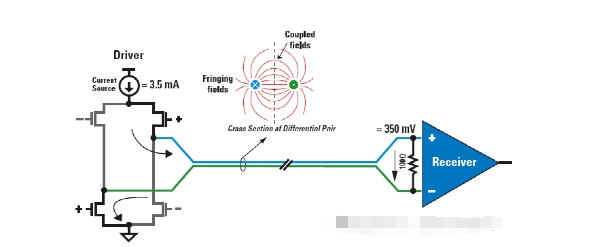

LVDS 基礎(chǔ)系列旨在提供低壓差分信號(hào)技術(shù)的基礎(chǔ)知識(shí)。 本視頻系列分為五個(gè)部分。 分別為 LVDS技術(shù)概述,LVDS 的優(yōu)點(diǎn), M-LVDS 和三種常用的通信架構(gòu),LVDS 數(shù)據(jù)速率, 以及 LVDS 接口的典型用例。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

-

ti

+關(guān)注

關(guān)注

113文章

8021瀏覽量

214422 -

通信

+關(guān)注

關(guān)注

18文章

6182瀏覽量

137415 -

lvds

+關(guān)注

關(guān)注

2文章

1118瀏覽量

67135

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

熱點(diǎn)推薦

LVDS接口的汽車認(rèn)證ESD保護(hù)

電子發(fā)燒友網(wǎng)站提供《LVDS接口的汽車認(rèn)證ESD保護(hù).pdf》資料免費(fèi)下載

發(fā)表于 02-20 16:11

?0次下載

為什么DATACLK用的是LVDS電平標(biāo)準(zhǔn)的接口呢?

你好,請(qǐng)問DAC的DACCLK用LVPECL電平標(biāo)準(zhǔn)的接口,為什么DATACLK用的是LVDS電平標(biāo)準(zhǔn)的接口呢?在設(shè)計(jì)DAC的時(shí)候,從哪方

發(fā)表于 01-21 07:56

能否用LMH0341將HD-SDI轉(zhuǎn)成LVDS接口,再用DS90CR288A將LVDS轉(zhuǎn)成RGB?

能否用LMH0341將HD-SDI轉(zhuǎn)成LVDS接口,再用DS90CR288A將LVDS轉(zhuǎn)成RGB,供給DM8168主芯片作為HD-SDI輸入解碼方案。

發(fā)表于 12-23 07:20

ADC3663輸出SLVDS差分電壓超過FPGA接口LVDS接口的輸入電壓范圍,如何處理?

根據(jù)ADC3663手冊,輸出格式為SLVDS,VCM=1.0V, VOD=500mV(min),700mV(typ), 850mV(max). 而FPGA通常LVDS接口(輸入)VIDIFF最大

發(fā)表于 11-27 06:23

lvds接口與其他接口比較

LVDS接口是一種低壓差分信號(hào)技術(shù),它通過小電壓擺幅和差分信號(hào)傳輸數(shù)據(jù),以減少功耗和電磁干擾。LVDS接口廣泛應(yīng)用于筆記本電腦、監(jiān)視器和高端電視等顯示設(shè)備中,因?yàn)樗軌蛱峁└哔|(zhì)量的視頻

lvds接口在工業(yè)顯示中的應(yīng)用

隨著工業(yè)自動(dòng)化和智能化的不斷發(fā)展,工業(yè)顯示技術(shù)也在不斷進(jìn)步。LVDS(Low Voltage Differential Signaling,低壓差分信號(hào))接口作為一種高速、低功耗的串行通信技術(shù),在

lvds接口適用于哪些設(shè)備 lvds接口兼容性問題解析

LVDS(Low-Voltage Differential Signaling,低電壓差分信號(hào))接口因其低功耗、低電磁干擾和長傳輸距離等特點(diǎn),在多種設(shè)備中得到了廣泛應(yīng)用。以下是對(duì)LVDS接口

lvds接口傳輸距離限制 lvds接口優(yōu)勢及劣勢分析

LVDS(Low Voltage Differential Signaling)是一種高速串行通信技術(shù),廣泛應(yīng)用于連接顯示器和圖形處理器等設(shè)備。LVDS接口通過小電壓擺幅的差分信號(hào)傳輸數(shù)據(jù),以減少

lvds接口和HDMI的區(qū)別 lvds接口電路設(shè)計(jì)技巧

LVDS(Low Voltage Differential Signaling,低電壓差分信號(hào))接口和HDMI(High-Definition Multimedia Interface,高清多媒體

lvds接口用途與應(yīng)用 lvds接口連接方法指南

LVDS(Low Voltage Differential Signaling,低電壓差分信號(hào))接口是一種數(shù)據(jù)傳輸和接口技術(shù),以下是對(duì)其用途、應(yīng)用以及連接方法的介紹: 一、LVDS

edp接口和lvds接口區(qū)別 edp接口和lvds接口能混用嗎

EDP(Embedded DisplayPort)接口和LVDS(Low Voltage Differential Signaling)接口是兩種不同的顯示接口技術(shù),它們在多個(gè)方面存在

lvds接口需要驅(qū)動(dòng)嗎

LVDS(Low-Voltage Differential Signaling,低電壓差分信號(hào))接口確實(shí)需要驅(qū)動(dòng),但其驅(qū)動(dòng)方式與其他常見的接口有所不同。 一、LVDS

edp接口和lvds接口能混用嗎

EDP(Embedded DisplayPort)接口和LVDS(Low Voltage Differential Signaling)接口是兩種不同的顯示接口技術(shù),它們在設(shè)計(jì)、工作原

【技術(shù)分享專欄】MIPI接口與LVDS接口有何區(qū)別?

啟明智顯Model3、Model4芯片支持RGB、LVDS、MIPI等多種屏幕接口,其中LVDS 和MIPI的物理接線是一樣的,都是5組差分對(duì),但是傳輸?shù)膬?nèi)容是不一樣的,即軟件的報(bào)文格式不一樣。

LVDS用法:LVDS RX 時(shí)鐘選擇 LVDS的PLL的復(fù)位信號(hào)的處理

這里以鈦金的LVDS為例。 LVDS RX 時(shí)鐘選擇 LVDS時(shí)鐘的接收要連接名字為GPIOx_P_y_PLLINz名字的差分對(duì),這樣的管腳直接驅(qū)動(dòng)PLL,產(chǎn)生

LVDS接口的典型用例分析

LVDS接口的典型用例分析

評(píng)論