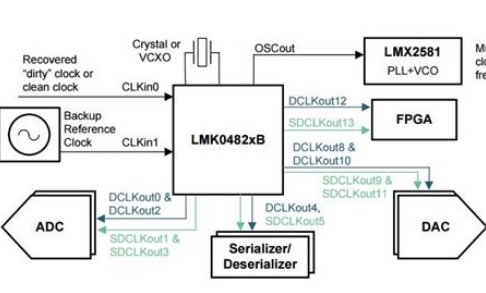

在“JESD204B子類(第一部分):JESD204B子類簡介與確定性延遲”一文中,我們總結了JESD204B子類和確定性延遲,并給出了子類0系統中多芯片同步的應用層解決方案詳情。本系列的第二部分詳細討論子類1和子類2的不同之處。具體而言,我們將討論滿足確定性延遲相關的時序要求時遇到的挑戰、子類2中器件時鐘速度限值,以及對于給定的系統應用,采用何種子類效果最佳的相關指導。

子類1

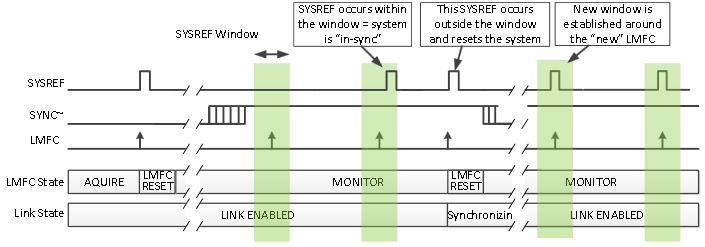

在子類1系統中,確定性延遲的精度取決于器件時鐘和SYSREF之間的時序關系,以及系統中這些信號的分布偏斜。除了SYSREF的設置時間和保持時間要求(TSU和THOLD),應用對于確定性延遲不確定的容忍程度對于定義SYSREF與器件時鐘的應用分布偏斜要求而言至關重要。

精確捕獲SYSREF

采用JESD204B接口的轉換器具有極高的采樣速率。為了降低系統中的相位噪聲,這些轉換器通常會使用一個參考時鐘,該參考時鐘與JESD204器件時鐘相同,其速率等于或大于采樣速率。在很多情況下,該時鐘頻率為GHz級。在如此高的速度下,要滿足設置和保持時間要求就會變得非常具有挑戰性。為了簡化系統設計,對于JESD204B系統組成部分的各器件而言,也許有必要采用可編程的SYSREF和/或器件時鐘相位失調。

子類1相對于子類2所具有的一個優勢,是前者采用源同步時鐘。子類2系統使用系統同步時鐘,相比使用源同步時鐘會更早遇到頻率限值問題。后文我們詳細考察子類1和子類2時序示例時,將加以說明。

確定性延遲不確定性

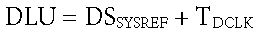

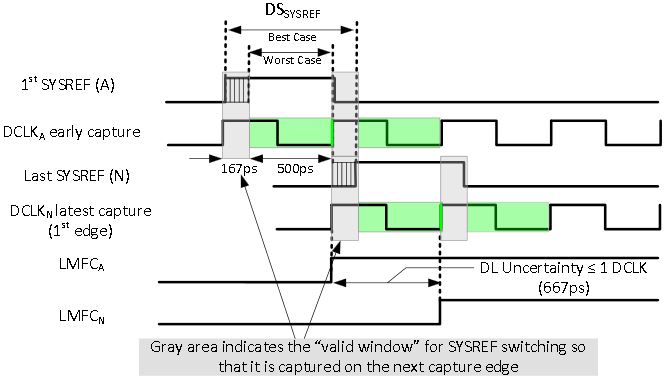

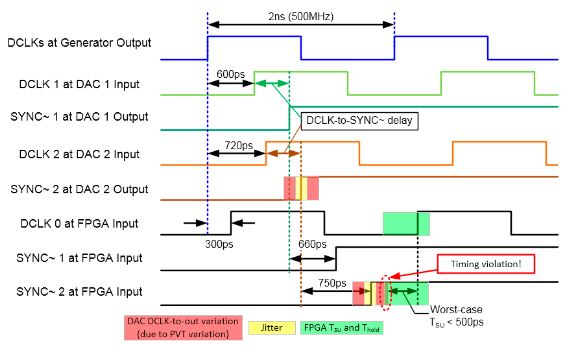

確定性延遲不確定性(DLU)在JESD204B系統中表現為LMFC偏斜,由系統中最早與最遲可能捕獲的SYSREF時間之差確定。圖1顯示的是最差情況下的DLU,此時系統中一切器件均不滿足SYSREF捕獲的設置和保持時間要求1。當系統中器件時鐘的分布偏斜不受控時便會發生;它會使最多一個器件的時鐘(DCLK)產生不確定性。這種不確定性會疊加到SYSREF分布偏斜中(DSSYSREF),形成總DLU。

DSSYSREF是系統中SYSREF的最早到達時間以及SYSREF的最遲到達時間之差(針對系統中的全部器件而言)。在圖中, TSU 是 ? TDCLK 和 THOLD is ? TDCLK。最早到達的SYSREF (A)在可能的最早時間加以捕獲(DCLKA剛好滿足設置時間要求),而最遲到達的SYSREF (N)在可能的最晚時間加以捕獲(DCLKN剛好不滿足設置時間要求)。因此,相應的LMFC對齊誤差等于 DSSYSREF + TDCLK。1 為保持DLU概念圖示的清晰明了,此處未考慮時鐘抖動和工藝、電壓以及溫度(PVT)的變化。

在很多應用中,都以能夠接受這種最差情況下的DLU作為要求。這些應用可能無需過于嚴格地控制器件的時鐘分布偏斜。確保SYSREF的脈沖寬度 (2 × TDCLK),然后控制SYSREF分布偏斜,就應當足以滿足系統時序要求。

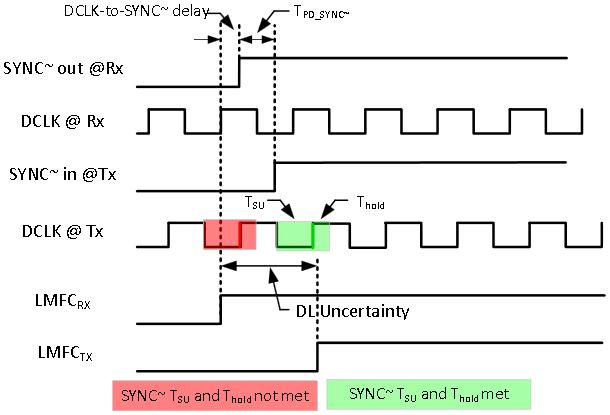

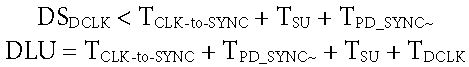

對于無法接受額外器件時鐘不確定性的應用,就必須嚴格控制器件的時鐘分布偏斜,保證系統中每一個器件的SYSREF時序要求得到滿足。這種情況見圖2;不確定性由下式給出:

最小化確定性延遲不確定性

如以上DLU等式所示,通過保證每一對SYSREF/DCLK均滿足設置與保持時間,以及最小化對內分布偏斜,便可最小化DLU。

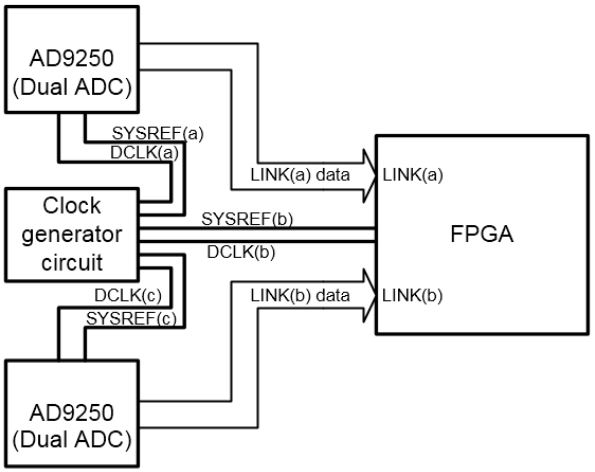

若要滿足設置與保持時間要求,JESD204B系統中的每一個器件都應有自己的SYSREF/DCLK對。可通過在各對內實現走線長度匹配,從而保證時序。走線長度匹配限值由SYSREF開關的有效窗口時間確定。此外,SYSREF應在DCLK的捕獲邊沿上輸出,且SYSREF長度必須大于DCLK的長度,以滿足保持時間要求(如果THOLD等于0,則長度可以相等)。

由于采用了走線長度匹配,最小化對內分布偏斜基本上等同于最小化SYSREF分布偏斜。該分布偏斜限值等于DLU限值減去有效窗口時間,同樣可以通過走線長度匹配來處理。DLU限值由應用要求所決定。

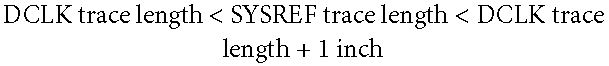

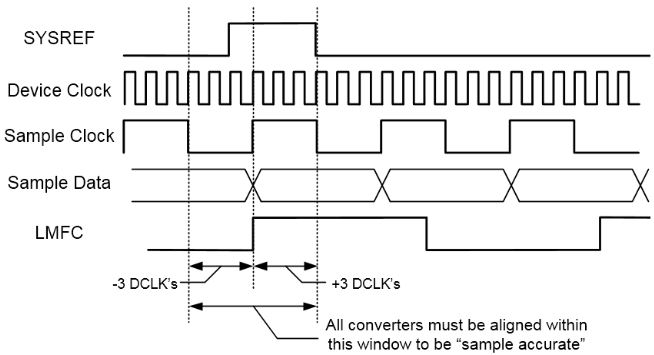

這些最小化DLU的方法如圖3所示。由于JESD204b系統中的每一個器件都有各自的SYSREF/DCLK對,滿足捕獲SYSREF的時序要求與使用源同步時鐘的任何系統類似。每個器件的時序裕量都視為與系統中的其他器件無關。

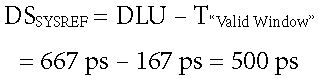

滿足這一要求可以保證SYSREF在有效窗口期間進行轉換,如圖4所示。2 DLU等于器件時鐘是滿足SYSREF時序要求的最差情況。

因此,所有SYSREF/DCLK對的對內分布偏斜必須在下式計算值以內3:

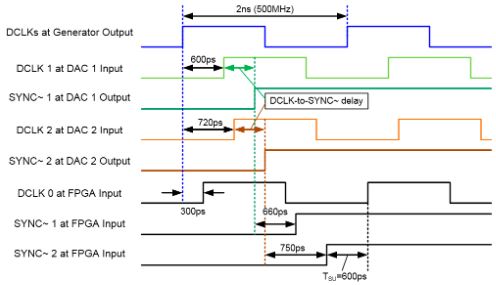

圖5顯示了此示例的時序。“最佳情況”分布偏斜(DSSYSREF)指的是允許較為寬松的走線長度匹配要求。3 500 ps表示SYSREF最差情況下的偏斜,應當用來確定走線長度的匹配限值。

在圖中, TSU是? TDCLK和THOLDis ? TDCLK。如圖所示,DLCK經偏斜后匹配DCLK至SYNC~延遲和SYNC~傳播延遲,并且剛好滿足設置時間要求。

圖13. 單轉換器應用的子類2 SYNC~捕獲時序 (最差情況DLU)

哪個子類最適合您的應用?

為JESD204B系統選擇哪個子類取決于您是否需要確定性延遲、若需要則精度是多少,以及用于系統中的器件時鐘要求。

子類0最容易實現;無需確定性延遲時可以使用子類0。哪怕您的多轉換器系統需要同步所有(或部分)轉換器的樣本,也能通過AD9625和AD9680支持的時間戳功能來實現。

由于子類1支持超高器件時鐘速率以及高采樣速率轉換器,對于要求這些高速率的系統來說,子類1是最保險的解決方案。子類1器件也可用于較低的速率。如果器件時鐘速率低于500 MHz,那么滿足時序要求便很簡單,無需調節時鐘相位。

子類2器件也可用于500 MHz以下的應用中。在較低速率下使用子類2的一個小優勢,是它可以減少邏輯器件的IO數,且無需將SYSREF路由至每一個JESD204B器件。

-

JESD204B

+關注

關注

6文章

82瀏覽量

19522

發布評論請先 登錄

如何實現JESD204B時鐘方案最大性能

JESD204B的系統級優勢

JESD204B轉換器的確定性延遲解密

在Xilinx FPGA上快速實現JESD204B

JESD204B串行接口時鐘的優勢

如何采用系統參考模式設計JESD204B時鐘

JESD204B協議介紹

采用系統參考模式設計JESD204B時鐘

JESD204B標準及演進歷程

JESD204C入門第二部分:新特性及其內容

采用系統參考模式設計JESD 204B時鐘

JED204B是什么?JESD204B的分類及優缺點介紹

JESD204B使用說明

JESD204B子類(第二部分):子類1與子類2系統考慮因素

JESD204B子類(第二部分):子類1與子類2系統考慮因素

評論