簡介

直接數(shù)字合成(DDS)技術(shù)正在迅速發(fā)展,但直接合成UHF和微波輸出頻率尚不實用或經(jīng)濟(jì)上可行。目前最先進(jìn)的商用DDS IC(如300 MHz AD9852單通道和AD9854正交完整DDS芯片)可為低VHF頻譜提供可用輸出,約為120 MHz。 DDS和輸出DAC的采樣速度限制構(gòu)成了主要瓶頸;基本DDS輸出信號不得大于采樣頻率的一半。 ADI公司的下一代高速DDS IC將以900 MHz采樣率和360 MHz可用基波輸出來挑戰(zhàn)這些限制。

為了利用UHF和微波頻率的DDS屬性,DDS通常與鎖相環(huán)(PLL)集成或在混頻器中上變頻。不幸的是,使用PLL的乘法會影響信號完整性,頻率分辨率和靈活性。此外,使用混頻器將DSB(雙邊帶)信號上變頻到更高頻率的單邊帶可能需要困難或不可能的輸出濾波以及高質(zhì)量的固定頻率本地振蕩器(LO)。用于克服這些缺點的方法通常需要多個PLL或混頻器/濾波器/振蕩器級。

以下是單級上升的改進(jìn)且經(jīng)濟(jì)的方法使用上述AD9854正交完整DDS和新器件AD8346正交調(diào)制器將頻率轉(zhuǎn)換為800至2500 MHz的頻率,相位精度在1度以內(nèi),幅度平衡在1900年內(nèi)在0.2 dB以內(nèi)兆赫。上變頻抑制載波單邊帶信號在整個頻率范圍內(nèi)顯示> 36 dB典型的LO抑制和不需要的邊帶頻率。此外,所有 DDS信號質(zhì)量得以保留,而不需要的上變頻產(chǎn)品則被最小化。對于許多應(yīng)用來說,36 dB抑制就足夠了,這種4000倍的無用信號功率抑制將大大降低輸出濾波器的復(fù)雜性,或者提高在要求更高的應(yīng)用中進(jìn)行有效濾波的可行性。

要在上邊帶和下邊帶之間進(jìn)行選擇,只需在AD8346調(diào)制器輸入引腳上反轉(zhuǎn)或交換正交DDS信號,I代表Q,Q代表I。 AD9854 DDS具有多種調(diào)制模式(AM,F(xiàn)M,PSK和FSK)。除靈活的單頻信號外,還通過提供數(shù)字和模擬通信功能,增強(qiáng)了該應(yīng)用的實用性。

正交DDS信號的上變頻只是AD8346正交調(diào)制器可以實現(xiàn)的一個例子。事實上,它可以上轉(zhuǎn)換任何正交模擬基帶信號(直流到70 MHz),具有類似的邊帶抑制。

正交SSB上變頻

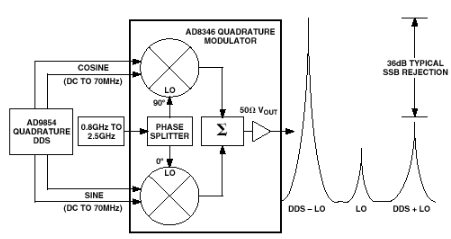

AD8346正交調(diào)制器提供令人印象深刻的SSB上變頻性能,允許基帶信號直接調(diào)制800 MHz至2.5 GHz的本地振蕩器(LO)頻率,通常36 dB抑制冗余邊帶和LO頻率。上變頻信號可以是跳頻,擴(kuò)頻或靜止的;在允許的輸入帶寬內(nèi)未調(diào)制或?qū)拵д{(diào)制。對于上變頻由DDS合成的正交信號,圖1中的框圖顯示了AD9854輸出信號如何應(yīng)用于AD8346差分“基帶調(diào)制”輸入,以便在LO頻率附近進(jìn)行SSB上變頻。

在正交上變頻中,兩個混頻器由正弦和余弦LO驅(qū)動,這些LO內(nèi)部源自用戶提供的單端高質(zhì)量振蕩器。混頻器輸入正弦和余弦基帶信號(濾波后的DDS輸出信號),以便在固定LO周圍對稱地進(jìn)行上變頻。兩個混頻器輸出在內(nèi)部相加,以添加同相分量并抑制混頻器輸出的正交分量。最終結(jié)果(無需額外濾波)是抑制載波,單邊帶,-10dBm和50歐姆阻抗的電壓輸出,其頻率可以是LO和基帶信號的和或差,加上抑制的殘余LO和相反的邊帶。

正交調(diào)制需要精確的相位關(guān)系,這不是一個新概念。五十年前,正交調(diào)制的首要用途之一是產(chǎn)生單邊帶無線電話信號;它被稱為“階段化方法”。然而,“濾波器方法”變得優(yōu)選,因為用模擬方法不能容易地在可觀的帶寬上保持正交相位關(guān)系。這兩種方法主要用于低IF頻率,目的是消除冗余邊帶并消除“載波”。

AD9854 DDS產(chǎn)生數(shù)字精確正交輸出信號(典型值)精度為十分之一(十度),從直流到> 120 MHz,使用300 MHz時鐘源。在圖1所示的示例中,如果適當(dāng)?shù)胤诸l,則可以從高質(zhì)量LO導(dǎo)出時鐘。 AD8346的正交相位誤差在800至2500 MHz輸出范圍內(nèi)通常為1度。這些器件包含一個“芯片組”,可以很好地用于許多寬帶數(shù)字和模擬通信方案,從擴(kuò)頻到電視。

一個更完整的解釋,包括模擬和數(shù)字正交調(diào)制和SSB上轉(zhuǎn)換的基本數(shù)學(xué)分析,可以在Doug Smith撰寫的文章“信號,樣品和材料:DSP教程(第1部分)”中找到。 1998年3月/ 4月,發(fā)行 QEX:通信實驗論壇雜志。欲了解更多信息,請聯(lián)系美國無線電中繼聯(lián)盟,225 Main Street,Newington,CT 06111,http://www.arrl.org/qex.

要更好地了解正交上轉(zhuǎn)換的優(yōu)點,比較兩種常用的產(chǎn)生UHF和微波DDS信號的方法可能是有益的: DDS / PLL倍頻和單級混頻器上變頻。

PLL / DDS乘法

DDS信號到UHF和微波頻率的PLL倍增很容易且經(jīng)濟(jì)地完成,但是要付出代價:DDS提供的優(yōu)勢幾乎會在所有理想的屬性中降低,包括相位噪聲規(guī)范,新頻率采集時間,頻率分辨率和無雜散動態(tài)范圍(SFDR)。確實存在降低信號劣化的PLL / DDS /混頻器/濾波器的組合,但是這種多級實現(xiàn)的復(fù)雜性和成本可能是不可容忍的。圖2顯示了典型的DDS / PLL實現(xiàn)。

PLL輸出相位噪聲是一種明顯且容易觀察到的現(xiàn)象;它的放大倍數(shù)會降低性能,與PLL的倍增系數(shù)成比例(以dB表示,20 log F out / F in )。例如,如果將10 MHz處的DDS信號的頻率乘以100以從PLL產(chǎn)生1 GHz的輸出,則PLL環(huán)路帶寬內(nèi)的輸出相位噪聲將比原始輸入信號大約40 dB。此外,PLL環(huán)路帶寬內(nèi)的雜散信號或“雜散”將增加相同的量。這可能導(dǎo)致不可接受的雜散電平比DDS輸入信號高出40dB

頻譜圖很容易顯示DDS信號的相位噪聲在乘以后會受到多大影響圖2中的PLL電路為×64。圖3顯示了14 MHz時PLL的DDS輸入信號,圖4顯示了896 MHz的PLL倍頻DDS信號。寬噪聲“裙邊”是降級相位噪聲的標(biāo)志。

為了說明PLL倍增對雜散電平的影響,調(diào)制DDS信號以產(chǎn)生豐富的低水平的馬刺接近基礎(chǔ)。圖5顯示了饋入PLL的調(diào)制DDS信號,而圖6顯示了PLL的30 kHz環(huán)路帶寬內(nèi)的這些雜散如何被放大。請注意,距離載波> 60 kHz,雜散幅度不受影響。相位噪聲沒有改變,也沒有任何其他參數(shù)被改變。

除了相位噪聲,定時抖動和雜散電平降級之外,許多其他所需的DDS屬性,包括頻率捷變和分辨率,都會受到PLL倍頻的不利影響。即使頻率分辨率也會比DDS分辨率差N倍,新頻率采集將受到PLL建立時間的限制(可能比DDS高出10,000倍)。

DDS /混頻器上變頻

設(shè)計人員可以選擇的更好的選擇是使用混頻器將DDS信號上變頻到UHF /微波頻率。上變頻不會顯著增加雜散電平或相位噪聲。此外,頻率捷變和分辨率不受影響。要克服的最大障礙是存在雙邊帶(DSB)輸出:LO + DDS和LO - DDS,以及發(fā)生的任何LO饋通。

圖7,顯示200抑制載波(LO)的頻譜區(qū)域,單上變頻混頻器輸出,證明了上轉(zhuǎn)換的這個問題。兩個邊帶相距50 MHz,LO饋通在兩者之間的中間頻率為1.04 GHz。這種50 MHz的擴(kuò)展僅為1 GHz輸出頻率的5%。過濾信號以去除不需要的邊帶和LO饋通將非常困難。如果輸出頻率增加到2 GHz,則可能使事情變得復(fù)雜到過濾不切實際的程度。為了克服這個問題,設(shè)計人員傳統(tǒng)上采用混合和濾波的多個階段來產(chǎn)生DSB信號,在UHF /微波處具有更大的邊帶間距,這將更容易過濾,但成本和復(fù)雜性要高得多。

DDS上變頻實驗室結(jié)果

在實驗室中使用AD9854和AD8346的評估板完成了SSB上變頻器的正交實現(xiàn)。需要對AD8346評估板進(jìn)行修改,以接受AD9854評估板提供的濾波,正交,單端信號。還需要增加輸出電壓電平,以滿足AD8346的輸入要求。圖8中顯示了實驗室連接和修改的示意圖。修改如下:

添加兩個1:16中心抽頭阻抗升壓變壓器(小型電路T16) -6T)將單端正交信號轉(zhuǎn)換為差分信號,并提供1:4的升壓電壓。使用中心抽頭的次級允許將1.2 V的直流偏移電壓添加到差分信號,以符合AD8346的輸入偏置要求。

在每個變壓器輸出端添加1000歐姆的終端電阻。

添加一個1.2伏直流偏置源,由兩個硅二極管組成,這些二極管通過一個2000歐姆的限流電阻從3.3伏電源電壓正向偏置。連接到I和Q通道變壓器次級繞組的中心抽頭。

此設(shè)置的測試驗證了正交輸入時AD8346數(shù)據(jù)手冊中的性能預(yù)期來自AD9854的信號經(jīng)過適當(dāng)調(diào)整,以補(bǔ)償正交相位誤差和I& Q幅度不平衡。見圖9和圖10。

I& D中的錯誤。在信號退出AD9854 IC之后,通過濾波器,不相等的電纜和PCB走線長度,變壓器差異等引入了Q正交相位關(guān)系 - 。系統(tǒng)相位誤差無法通過編程更改來糾正AD9854。其輸出以精確的正交固定。通過調(diào)整AD9854至AD8346評估板的電纜長度,可以糾正相位誤差。使用AD9854的12位獨立正弦和余弦(I& Q)數(shù)字幅度乘法器級可以校正幅度不等式。

圖9顯示了以1.05 GHz為中心的AD8346輸出頻譜的200 MHz段。 DDS“調(diào)制”上邊帶和下邊帶信號在LO的任一側(cè)在1.04 GHz處看到25 MHz。在抑制的上邊帶(USB)和有利的下邊帶(LSB)幅度之間指示-40dB的差異。 40 dB差分相當(dāng)于功率比約為1萬比1。這種邊帶抑制水平表示大約1度的輸入信號相位失配。

1.015 GHz下邊帶(LSB)的近視圖(圖10)表現(xiàn)出色信號完整性。它與圖4中的PLL倍增信號進(jìn)行了驚人的比較。如前所述,可以交換正交調(diào)制器的正弦和余弦DDS信號,使互補(bǔ)邊帶更受青睞。

LO饋通幅度(-36 dB)大于此設(shè)置中的抑制邊帶。 LO饋通電平不受DDS I和D的相位或幅度的影響。 Q輸入信號。為了降低LO饋通的重要性,I&的電壓電平降低。每個差分輸入引腳的Q輸入信號應(yīng)最大化(1V p-p)。

結(jié)論

正交調(diào)制是DDS上轉(zhuǎn)換為UHF和微波頻率的完善且經(jīng)濟(jì)的方法,不會丟失DDS技術(shù)的任何理想屬性或損害信號質(zhì)量。 AD8346正交調(diào)制器簡化了工藝。這是與AD9854 DDS的“自然”匹配,具有差分正交輸出。擁有高品質(zhì)的LO,UHF&微波SSB輸出很容易實現(xiàn)。

AD9854具有多種調(diào)制模式,該應(yīng)用支持微波輸出頻率的(幾乎)完整的AM,F(xiàn)M,PSK,F(xiàn)SK激勵器。利用AM抑制載波I&的少量附加信號處理。 Q DDS輸出,SSB語音或其他幅度調(diào)制方案成為可能。圖11顯示了IC如何與外部調(diào)制源和控制器件互連以執(zhí)行通信功能。

36 dB(典型值)邊帶和LO拒絕直接可用于許多應(yīng)用程序,在要求更高的應(yīng)用程序中,輸出過濾成為一項不那么艱巨的任務(wù)。適當(dāng)調(diào)整DDS I& Q信號相位關(guān)系和幅度平衡可以進(jìn)一步增加邊帶抑制。

雖然它專門設(shè)計用于提供適當(dāng)?shù)妮敵鲂盘柖鵁o需多個DDS來實現(xiàn)此功能,但此處描述的應(yīng)用中的AD9854并不是組合DDS和正交調(diào)制的唯一方法。其他DDS IC,如AD9850,AD9851和AD983x系列,也可用于正交對。如果兩個DDS可以同步,則很可能可以使用內(nèi)部相位偏移電路對它們進(jìn)行編程以實現(xiàn)正交輸出。有關(guān)DDS和數(shù)字調(diào)制器產(chǎn)品的完整列表,以及訪問技術(shù)說明和數(shù)據(jù)表,請參閱DDS產(chǎn)品。值得注意的是,AD9854的獨立可編程I& Q輸出幅度使輸出匹配成為一個簡單的軟件程序。

正交DDS SSB上變頻到2GHz以上的相對簡單和經(jīng)濟(jì)性應(yīng)該鼓勵讀者考慮將這種技術(shù)添加到他們的曲目中。它保留了微波頻率下所有理想的DDS屬性,同時大大減少了傳統(tǒng)雙邊帶混頻器上變頻的不良冗余邊帶。

-

pll

+關(guān)注

關(guān)注

6文章

888瀏覽量

136197 -

DDS

+關(guān)注

關(guān)注

22文章

672瀏覽量

154197 -

調(diào)制器

+關(guān)注

關(guān)注

3文章

897瀏覽量

46219

發(fā)布評論請先 登錄

在DAC3482中,采用片內(nèi)混頻器實現(xiàn)上變頻功能需要保證兩路輸入信號的正交性嗎?

怎么將一路信號轉(zhuǎn)為IQ正交信號

有關(guān)AD9361的上變頻

一路模擬信號轉(zhuǎn)I/Q正交信號有解決方案嗎?

PXI 5610實現(xiàn)上變頻信號發(fā)送

AD9739上變頻功能實現(xiàn)原理是什么?

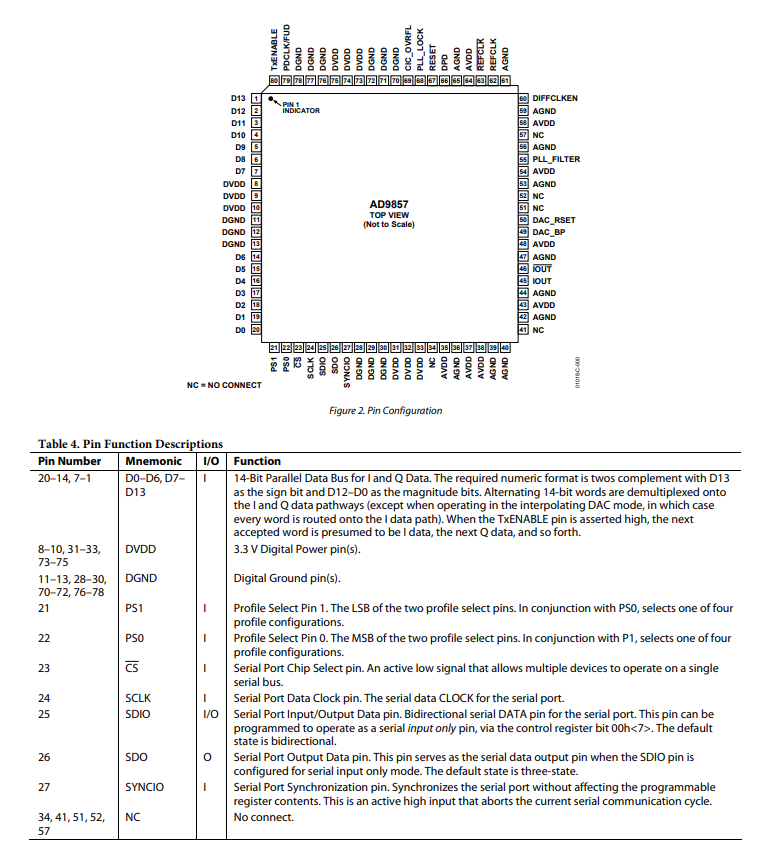

數(shù)字正交上變頻器AD9857

基于QDUC的雷達(dá)上變頻電路的設(shè)計

AN-0996: 在點對點微波發(fā)射系統(tǒng)中使用正交數(shù)字上變頻器(QDUC)的優(yōu)勢

AD9957: 內(nèi)置14位DAC的1 GSPS正交數(shù)字上變頻器

正交DDS信號至800至2500MHz頻段的單邊帶上變頻

上變頻和下變頻的定義 下變頻和上變頻的區(qū)別

AD9857 CMOS 200 MSPS、14位正交數(shù)字上變頻器技術(shù)手冊

正交DDS信號的上變頻基波輸出挑戰(zhàn)

正交DDS信號的上變頻基波輸出挑戰(zhàn)

評論