約束、時(shí)序分析的概念

很多人詢問(wèn)關(guān)于約束、時(shí)序分析的問(wèn)題,比如:如何設(shè)置setup,hold時(shí)間?如何使用全局時(shí)鐘和第二全....

關(guān)于AD9361的抗阻塞能力的實(shí)測(cè)

在窄帶應(yīng)用中,零中頻軟件無(wú)線電芯片已經(jīng)非常流行,其代表是ADI公司的AD9361。

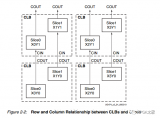

關(guān)于FPGA四輸入、六輸入基本邏輯單元LUT的一點(diǎn)理解

我們知道FPGA由LUT、IO接口、時(shí)鐘管理單元、存儲(chǔ)器、DSP等構(gòu)成,我覺(jué)得最能代表FPGA特點(diǎn)的....

Verilog實(shí)現(xiàn)流水燈及與C語(yǔ)言的對(duì)比

由原理圖可知僅當(dāng)FPGA的對(duì)應(yīng)管腳輸入低電平時(shí)LED才會(huì)亮,流水燈的效果可以輪流讓四個(gè)對(duì)應(yīng)管腳輸....

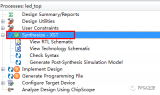

軟件與Verilog基本格式規(guī)范說(shuō)明

以前總是沒(méi)有記錄的習(xí)慣,導(dǎo)致遇到問(wèn)題時(shí)總得重新回憶與摸索,大大降低了學(xué)習(xí)效率,從今天開(kāi)始決定改掉....

詳細(xì)討論SERDES用到的各種關(guān)鍵技術(shù)

隨著大數(shù)據(jù)的興起以及信息技術(shù)的快速發(fā)展,數(shù)據(jù)傳輸對(duì)總線帶寬的要求越來(lái)越高,并行傳輸技術(shù)的發(fā)展受到了時(shí)....

如何通過(guò)Vivado Synthesis中的URAM矩陣自動(dòng)流水線化來(lái)實(shí)現(xiàn)最佳時(shí)序性能

UltraRAM 原語(yǔ)(也稱為 URAM)可在 Xilinx UltraScale + 架構(gòu)中使用,....

Vivado調(diào)用Questa Sim仿真中存在的一些問(wèn)題

首先說(shuō)明一下Modelsim與Questa Sim都可以與Vivado聯(lián)調(diào),也比較相似,但是Ques....

FPGA設(shè)計(jì)中大位寬、高時(shí)鐘頻率時(shí)序問(wèn)題調(diào)試經(jīng)驗(yàn)總結(jié)

時(shí)鐘周期約束:用戶需要將設(shè)計(jì)中的所有時(shí)鐘進(jìn)行約束后,綜合器才能進(jìn)行合理的靜態(tài)時(shí)序分析。一個(gè)設(shè)計(jì)中的時(shí)....

FPGA設(shè)計(jì)原則總結(jié)

這里的面積指一個(gè)設(shè)計(jì)消耗 FPGA/CPLD 的邏輯資源的數(shù)量,對(duì)于 FPGA 可以用消耗的 FF(....

Windows上使用iverilog+gtkwave仿真

使用Verilog編寫(xiě)好了功能模塊以及對(duì)應(yīng)的testbench之后,一般需要對(duì)其功能進(jìn)行仿真測(cè)試。由....

Xilinx FPGA時(shí)序約束設(shè)計(jì)和分析

在進(jìn)行FPGA的設(shè)計(jì)時(shí),經(jīng)常會(huì)需要在綜合、實(shí)現(xiàn)的階段添加約束,以便能夠控制綜合、實(shí)現(xiàn)過(guò)程,使設(shè)計(jì)滿足....

按鍵抖動(dòng)消除verilog設(shè)計(jì)

按鍵作為一種機(jī)械開(kāi)關(guān),在進(jìn)行按鍵操作時(shí),機(jī)械接觸點(diǎn)的彈性及電壓突變等原因,在機(jī)械開(kāi)關(guān)合閉的時(shí)候會(huì)出現(xiàn)....

寄存器怎么賦初值啊?這電路怎么工作呢?

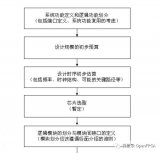

數(shù)字電路中,電路通過(guò)復(fù)位來(lái)啟動(dòng),復(fù)位猶如數(shù)字電路的“起搏器”,主要有下面三種方式

牛頓-拉夫遜迭代法原理及其實(shí)現(xiàn)

直接看數(shù)學(xué)公式描述如何迭代不直觀,先來(lái)看動(dòng)圖就很容易理解牛頓迭代法為什么叫迭代法以及怎樣迭代的

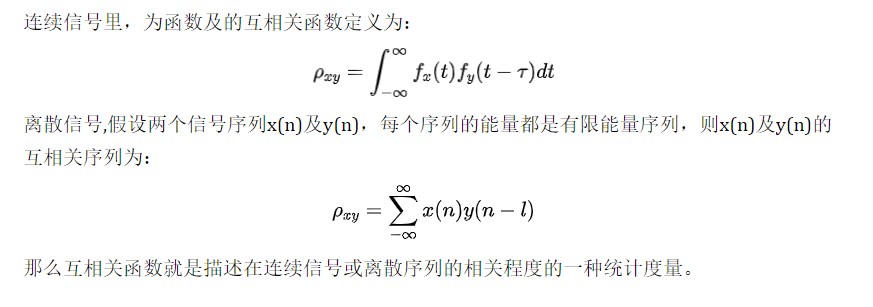

如何判定兩個(gè)信號(hào)序列的相似程度?

在統(tǒng)計(jì)學(xué)中,相關(guān)是描述兩個(gè)隨機(jī)變量序列或二元數(shù)據(jù)之間的統(tǒng)計(jì)關(guān)系,無(wú)論是否具有因果關(guān)系。

世界首款采用58Gbps PAM4收發(fā)器技術(shù)的現(xiàn)場(chǎng)可編程門(mén)陣列

英特爾 Stratix 10 TX FPGA 提供多達(dá) 144 個(gè)收發(fā)器通道和 1 到 58 Gb....

RAM初始化的下板驗(yàn)證

本實(shí)驗(yàn)基于xilinx ARTIX-7芯片驗(yàn)證實(shí)現(xiàn),有時(shí)間有興趣的朋友可在其他FPGA芯片上實(shí)現(xiàn)驗(yàn)證....

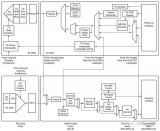

一個(gè)簡(jiǎn)單的8位處理器完整設(shè)計(jì)過(guò)程及verilog代碼

一個(gè)簡(jiǎn)單的8位處理器完整設(shè)計(jì)過(guò)程及verilog代碼,適合入門(mén)學(xué)習(xí)參考,并含有作者個(gè)人寫(xiě)的指令執(zhí)行過(guò)....

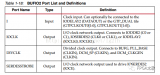

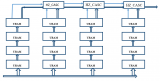

A/X家FPGA架構(gòu)及資源評(píng)估

基本邏輯單元LAB包含10xALM,ALM全程為Adaptive Logic Module,具有8輸....

HLS協(xié)議實(shí)現(xiàn)

HLS,Http Live Streaming 是由Apple公司定義的用于實(shí)時(shí)流傳輸?shù)膮f(xié)議,HLS....