高級(jí)設(shè)計(jì):SDR SDRAM驅(qū)動(dòng)設(shè)計(jì)

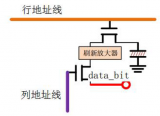

隨機(jī)訪問存儲(chǔ)器(RAM)分為靜態(tài)RAM(SRAM)和動(dòng)態(tài)RAM(DRAM)。由于動(dòng)態(tài)存儲(chǔ)器存儲(chǔ)單元的....

阿特·德吉亞斯變革集成電路設(shè)計(jì)

計(jì)算機(jī)歷史博物館2009年的口述歷史表明,他在那里開發(fā)了用多路復(fù)用器設(shè)計(jì)邏輯的工具。他和一位設(shè)計(jì)師朋....

系統(tǒng)模塊SOM能否成為FPGA的未來形態(tài)?

我認(rèn)為FPGA的主要優(yōu)勢有很多,但我認(rèn)為排名前三的優(yōu)勢分別是:靈活的輸入/輸出,確定性,低時(shí)延。

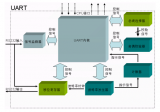

基于FPGA的UART控制器設(shè)計(jì)

串口的出現(xiàn)是在1980年前后,數(shù)據(jù)傳輸率是115kbps~230kbps。串口出現(xiàn)的初期是為了實(shí)現(xiàn)連....

204B實(shí)戰(zhàn)應(yīng)用-LMK04821代碼詳解

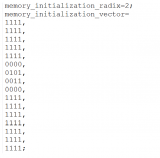

通過閱讀LMK04821數(shù)據(jù)手冊,我們可以從中知道,可以通過SPI協(xié)議對LMK04821進(jìn)行寄存器的....

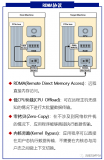

基于Corundum架構(gòu)的100G RDMA網(wǎng)卡設(shè)計(jì)

傳統(tǒng)TCP/IP技術(shù)處理數(shù)據(jù)包需通過操作系統(tǒng)和其他軟件層,導(dǎo)致數(shù)據(jù)在系統(tǒng)內(nèi)存、處理器緩存和網(wǎng)絡(luò)控制器....

如何脫離Vivado建立單獨(dú)仿真環(huán)境軟件呢?

FPGA項(xiàng)目開發(fā)的過程中,需要完成設(shè)計(jì)代碼開發(fā)、驗(yàn)證環(huán)境搭建、仿真分析、板級(jí)驗(yàn)證等操作,在這個(gè)過程中....

使用FPGA做的開源示波器

其實(shí)用FPGA做的示波器有很多,開源的相對較少,我們今天就簡單介紹一個(gè)使用FPGA做的開源示波器。

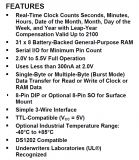

基于FPGA的RTC實(shí)時(shí)時(shí)鐘系統(tǒng)設(shè)計(jì)

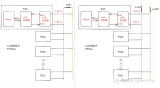

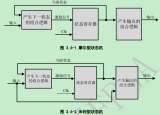

RTC(real time clock)實(shí)時(shí)時(shí)鐘,在電腦、手機(jī)等電子產(chǎn)品中都有,應(yīng)用較多。它的主要作....

設(shè)計(jì)一個(gè)計(jì)數(shù)器來講解時(shí)序邏輯

時(shí)序邏輯是Verilog HDL 設(shè)計(jì)中另一類重要應(yīng)用。從電路特征上看來,其特點(diǎn)為任意時(shí)刻的輸出不僅....

如何設(shè)計(jì)一顆AI芯片?AI芯片設(shè)計(jì)入門方案

機(jī)器學(xué)習(xí)(ML)已經(jīng)在在線活動(dòng)中變得無處不在。近年來,這些模型的規(guī)模和復(fù)雜性大幅增長,這有助于提高預(yù)....

基于FPGA Vivado的數(shù)字鐘設(shè)計(jì)(附源工程)

工程建立完畢,我們需要將lab2這個(gè)工程所需的IP目錄文件夾復(fù)制到本工程文件夾下。本工程需要兩個(gè)IP....

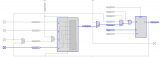

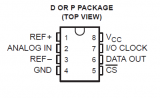

Vivado系列之TCL549驅(qū)動(dòng)設(shè)計(jì)

? 系統(tǒng)性的掌握技術(shù)開發(fā)以及相關(guān)要求,對個(gè)人就業(yè)以及職業(yè)發(fā)展都有著潛在的幫助,希望對大家有所幫助。本....

10行代碼輕松在ZYNQ MP上實(shí)現(xiàn)圖像識(shí)別的步驟

Xilinx Vitis-AI 是用于 Xilinx 硬件平臺(tái)上的 AI 推理的開發(fā)堆棧。它由優(yōu)化的....

英特爾Quartus Prime軟件v23.1上線

此外,Nios V/g 內(nèi)核還有著更大的軟件生態(tài)系統(tǒng),包括 FreeRTOS 和 Zephyr RT....

使用CCIX進(jìn)行高速緩存一致性主機(jī)到FPGA接口的評(píng)估

Chiplet技術(shù)和NoC技術(shù)目前已經(jīng)成為解決摩爾定律無法延續(xù)的一種重要方法,現(xiàn)在的CPU芯片對外的....

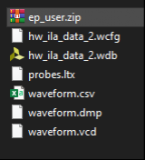

如何使用Python腳本調(diào)試賽靈思PCIe設(shè)計(jì)?

現(xiàn)在,您不僅可以使用 Python 腳本執(zhí)行調(diào)試分析,更重要的是,借由 Vivado ILA 所生成....

使用Vitis AI在Zynq MP上實(shí)現(xiàn)手勢識(shí)別

FPGA得益于其高可編程性以及低延遲,低功耗的特點(diǎn),在機(jī)器學(xué)習(xí)的推理領(lǐng)域已獲得了廣泛的關(guān)注。在過去,....

如何使Linux網(wǎng)絡(luò)協(xié)議棧中RFS功能優(yōu)化 MPSoC APU 的并行處理能力

? 本文介紹如何使能 Linux 網(wǎng)絡(luò)協(xié)議棧中的 RFS(receive flow steering....

FPGA零基礎(chǔ)學(xué)習(xí)之Vivado-FIFO使用教程

FIFO的英文全稱叫做First in First out,即先進(jìn)先出。這也就決定了這個(gè)IP核的特殊....

FPGA零基礎(chǔ)學(xué)習(xí)之Vivado-ROM使用教程

系統(tǒng)性的掌握技術(shù)開發(fā)以及相關(guān)要求,對個(gè)人就業(yè)以及職業(yè)發(fā)展都有著潛在的幫助,希望對大家有所幫助。本次帶....