摘 要: 在進(jìn)行非真實(shí)感渲染(NPR)處理時(shí)需要大量的計(jì)算,這對(duì)高幀率、高分辨率的視頻做實(shí)時(shí)的NPR渲染是一個(gè)難題。根據(jù)FPGA以并行運(yùn)算為主的特點(diǎn),對(duì)傳統(tǒng)的NPR算法做了改進(jìn)和簡(jiǎn)化,最終設(shè)計(jì)了一種基于FPGA的實(shí)時(shí)NPR系統(tǒng)。實(shí)驗(yàn)結(jié)果表明,該系統(tǒng)對(duì)高幀率、高分辨率的視頻做實(shí)時(shí)NPR處理具有運(yùn)算速度快、系統(tǒng)穩(wěn)定等特點(diǎn),同時(shí)還具有體積小、便于攜帶等優(yōu)點(diǎn)。

?

0 引言

非真實(shí)感渲染(NON-photorealistic rendering,NPR)是計(jì)算機(jī)圖形學(xué)的一類技術(shù),主要模擬藝術(shù)形式的畫面風(fēng)格,也用于發(fā)展新的繪制風(fēng)格。與傳統(tǒng)的追求真實(shí)感的計(jì)算機(jī)圖形學(xué)不同,NPR受到油畫、素描、技術(shù)圖紙和動(dòng)畫卡通的影響。它已經(jīng)以卡通造影的形式出現(xiàn)在電影和電子游戲中。非真實(shí)感繪制技術(shù)從20世紀(jì)80年代開始興起,當(dāng)時(shí)的研究進(jìn)展緩慢。直到90年代中期,尤其是EUROGRAPHICS和SIGGRAPH上關(guān)于這方面的幾篇論文才確立了這一領(lǐng)域的雛形[1]。近年來,NPR越來越多地被應(yīng)用到各個(gè)領(lǐng)域,例如視頻通信、視頻游戲、精密程度較高的醫(yī)學(xué)和科學(xué)插圖[2],由此可見高分辨率、實(shí)時(shí)的NPR系統(tǒng)越來越凸顯出重要的地位。

目前實(shí)現(xiàn)NPR處理主要有兩種途徑:一種是在PC機(jī)上進(jìn)行處理[3-7];另一種是在嵌入式系統(tǒng)中進(jìn)行處理[8]。參考文獻(xiàn)[3]和參考文獻(xiàn)[4]主要在PC上針對(duì)單幅圖片做了NPR處理,參考文獻(xiàn)[5]利用OpenCV API在計(jì)算機(jī)上對(duì)圖片和視頻實(shí)現(xiàn)了抽象處理,參考文獻(xiàn)[6]和[7]則在PC上用特征流法和光流法等特定算法對(duì)視頻做了抽象處理。在NPR系統(tǒng)中,圖像濾波、邊緣檢測(cè)、色彩變化等都需要大量復(fù)雜的運(yùn)算。因此在PC上很難對(duì)分辨率稍大或者幀率稍高的視頻做到實(shí)時(shí)處理。又由于PC機(jī)體積較大,不方便系統(tǒng)的移動(dòng),所以在嵌入式系統(tǒng)上做NPR是必然的趨勢(shì)。參考文獻(xiàn)[8]則是在一個(gè)以Xilinx Virtex-2 FPGA為核心的平臺(tái)上對(duì)單一圖片做了油畫處理,但是由于其平臺(tái)的限制,并未實(shí)現(xiàn)對(duì)視頻的實(shí)時(shí)處理。

本文在以Xilinx Virtex-5 FPGA為核心的自行設(shè)計(jì)的高速圖像處理平臺(tái)上,實(shí)現(xiàn)了對(duì)Camera Link接口相機(jī)采集到的視頻做實(shí)時(shí)的NPR渲染,并輸出到顯示器上進(jìn)行顯示。本文首先對(duì)NPR算法進(jìn)行講解,然后對(duì)系統(tǒng)和NPR算法的硬件結(jié)構(gòu)做出具體分析,最后給出實(shí)驗(yàn)結(jié)果及結(jié)論。

1 算法描述

雖然NPR渲染的具體實(shí)現(xiàn)方法多種多樣,但是它們的處理流程大致相同。經(jīng)過大量的文獻(xiàn)查閱,主流的NPR渲染流程都要經(jīng)過邊緣增強(qiáng)、擴(kuò)散濾波、量化光照信息三個(gè)步驟。本文也采用這種流程進(jìn)行處理,每個(gè)步驟所采用的具體方法將在下面進(jìn)行介紹。

1.1 邊緣增強(qiáng)

當(dāng)檢測(cè)到邊緣點(diǎn)之后,把邊緣點(diǎn)的RGB分量全部置為0,即可達(dá)到邊緣增強(qiáng)的效果。目前主流的邊緣檢測(cè)方法有差分邊緣檢測(cè)、Roborts算子、Prewitt算子、Kirsh算子、Laplace算子、LOG算子和Canny算子,考慮到在FPGA上實(shí)現(xiàn)的復(fù)雜性及資源利用率,本文采用的是Prewitt算子。

通常情況下,邊緣檢測(cè)每次只對(duì)圖像中3×3的圖像塊進(jìn)行處理,如圖1(a)所示。圖像塊的第一行和第三行的差近似x方向的導(dǎo)數(shù),第三列與第一列之差近似于y方向的導(dǎo)數(shù)[9]。如下所示:

Gx=(z7+z8+z9)-(z1+z2+z3)(1)

Gy=(z3+z6+z9)-(z1+z4+z7)(2)

上面就是Prewitt算子,Prewitt算子只有簡(jiǎn)單的加減法,非常適合于FPGA實(shí)現(xiàn)。Prewitt算子模板如圖1(b)和(c)所示。

1.2 擴(kuò)散濾波

NPR的另一個(gè)重要步驟是擴(kuò)散濾波,它能模糊較小的不連續(xù)和突出的邊緣,并且達(dá)到圖像色彩擴(kuò)散的效果。處理速度較快的經(jīng)典圖像濾波算法有鄰域平均法和中值濾波法等。由于要實(shí)現(xiàn)擴(kuò)散濾波的效果且要兼顧FPGA的運(yùn)算特點(diǎn),本文決定采用鄰域平均法。鄰域平均法是把相鄰像素的相應(yīng)分量值的平均值作為中心點(diǎn)像素相應(yīng)分量值。若輸入圖像中某點(diǎn)的各分量值為f(j,k),以其為中心,取N×N的窗口像素組成的點(diǎn)集用A表示(其中N=3,5,7…)。經(jīng)鄰域平均法濾波后,像素f(j,k)對(duì)應(yīng)的輸出為[10]:

此算法的優(yōu)點(diǎn)在于算法簡(jiǎn)單,適于在FPGA上實(shí)現(xiàn),而且能達(dá)到色彩擴(kuò)散的目的。

1.3量化光照信息

抽象效果的特點(diǎn)是原始輸入圖像中的很多細(xì)節(jié)信息被忽略,大塊區(qū)域的顏色比較接近或均勻[3]。因此,對(duì)圖像進(jìn)行亮度信息量化操作是必要的步驟,以此來實(shí)現(xiàn)分塊化效果。式(4)是量化的計(jì)算公式:

由于此計(jì)算公式需要進(jìn)行正切計(jì)算,對(duì)FPGA來說復(fù)雜度較高,所以本文只是將RGB各顏色分量的低位置1,只保留高3~4位的有效信息,這樣也能達(dá)到忽略細(xì)節(jié)信息的目的,讓以前顏色基本相同的區(qū)域都保持一致。

2 硬件設(shè)計(jì)

2.1 系統(tǒng)結(jié)構(gòu)

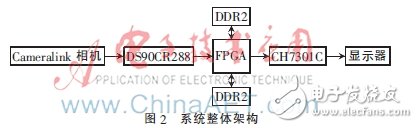

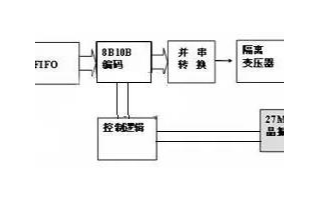

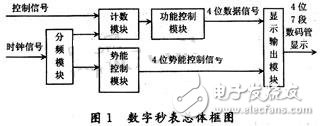

系統(tǒng)的前端采用的是一個(gè)Camera Link接口的工業(yè)相機(jī),用于視頻采集。相機(jī)分辨率為767×576,幀率為60 f/s,相機(jī)時(shí)鐘為36.15 MHz。視頻數(shù)據(jù)通過Camera Link線纜傳到圖像處理平臺(tái)上,然后由一個(gè)接收芯片DS90CR288將收到的差分信號(hào)轉(zhuǎn)換成24位RGB圖像數(shù)據(jù),再將數(shù)據(jù)傳到FPGA中。系統(tǒng)使用的處理器是Xilinx公司V5系列的一款FPGA芯片xc5vlx110t。FPGA利用兩片DDR2內(nèi)存對(duì)圖像進(jìn)行緩存、處理,最后控制DVI芯片CH7301C進(jìn)行實(shí)時(shí)顯示。系統(tǒng)的整體架構(gòu)如圖2所示。

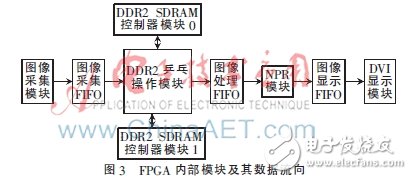

FPGA內(nèi)部首先由圖像采集模塊將圖像傳到圖像采集FIFO中,然后由乒乓操作模塊將圖像采集FIFO中的數(shù)據(jù)進(jìn)行乒乓操作暫存到DDR2里面,實(shí)現(xiàn)前后速度的匹配,再將數(shù)據(jù)輸出到圖像處理FIFO。NPR模塊讀取圖像處理FIFO中的數(shù)據(jù)進(jìn)行處理后輸出到圖像顯示FIFO,最后DVI顯示模塊讀取圖像顯示FIFO中的數(shù)據(jù)進(jìn)行顯示,F(xiàn)PGA內(nèi)部模塊及其數(shù)據(jù)流向如圖3所示。

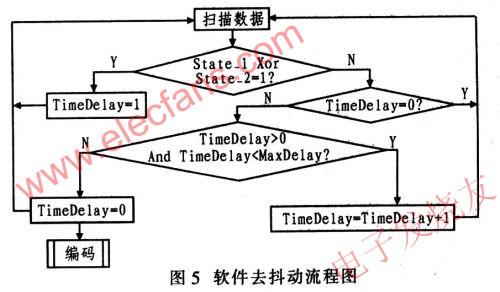

2.2 NPR模塊

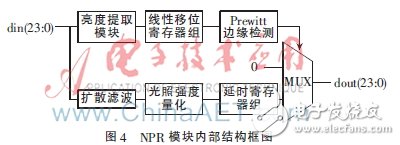

經(jīng)過DDR2乒乓緩存過后的24位RGB圖像數(shù)據(jù)輸出后會(huì)通過NPR模塊。在NPR模塊中,圖像數(shù)據(jù)分成兩路:一路數(shù)據(jù)進(jìn)行邊緣檢測(cè),首先通過亮度提取模塊進(jìn)行亮度提取,然后進(jìn)入一個(gè)行緩沖模塊,進(jìn)行三行完整圖像的緩存,最后進(jìn)入邊緣檢測(cè)模塊,進(jìn)行水平和垂直方向的邊緣檢測(cè)。另一路數(shù)據(jù)主要進(jìn)行色彩濾波和光照強(qiáng)度量化,以及為了達(dá)到時(shí)序匹配而做的延時(shí)。最后由選擇器進(jìn)行選擇輸出,若是邊緣則輸出黑色,否則輸出另一路處理過后的圖像數(shù)據(jù)。NPR模塊整體結(jié)構(gòu)如圖4所示。

2.2.1 亮度分量提取

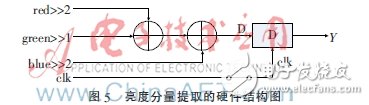

通常情況下,邊緣檢測(cè)是對(duì)灰度圖像進(jìn)行的,由于相機(jī)采集到的圖像是RGB圖像,所以必須進(jìn)行彩色圖像到灰度圖像的變換,即提取亮度分量。亮度分量Y和RGB的轉(zhuǎn)換公式是:

Y=0.229×red+0.587×green+0.114×blue(5)

考慮到FPGA中更適合于做加減及移位運(yùn)算,所以將式(5)做如下的近似變形,這樣用簡(jiǎn)單的移位運(yùn)算就可以輕松地實(shí)現(xiàn)亮度分量的提取:

這樣既能獲得較好的提取效果,又能將浮點(diǎn)運(yùn)算和乘法運(yùn)算轉(zhuǎn)化為簡(jiǎn)單的移位運(yùn)算。最后的硬件結(jié)構(gòu)如圖5所示。

2.2.2 邊緣檢測(cè)

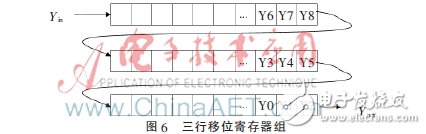

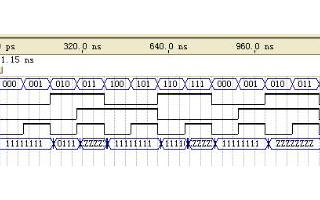

用Prewitt方法進(jìn)行邊緣檢測(cè),本質(zhì)上就是將上面介紹的Prewitt算子分別與灰度圖像做卷積,然后用梯度計(jì)算公式計(jì)算該點(diǎn)的梯度值。要實(shí)現(xiàn)圖像與模板的卷積,必須同時(shí)獲得三行圖像的數(shù)據(jù),為了達(dá)到這個(gè)目的,本系統(tǒng)使用一個(gè)三行移位寄存器組,用來存儲(chǔ)前一步得到的亮度信息,效果如圖6所示。

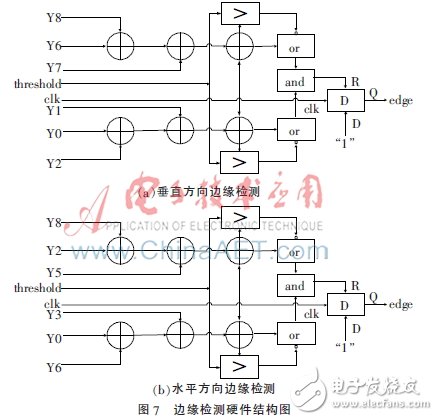

每次將這三行的前三個(gè)點(diǎn)組成的一個(gè)3×3矩陣分別與模板作卷積,就能分別得到垂直與水平方向的梯度。為了避免開方運(yùn)算,直接將垂直與水平方向的梯度與門限做比較,只要任一方向的梯度高于門限值,就認(rèn)定這個(gè)點(diǎn)是邊緣點(diǎn),上述操作雖然要求得到梯度值的絕對(duì)值,但與典型開方近似運(yùn)算JPL算法相比,減少了3個(gè)時(shí)鐘周期并且降低了算法復(fù)雜度。經(jīng)過多次實(shí)驗(yàn)對(duì)比驗(yàn)證,本系統(tǒng)最后選定了一個(gè)固定的門限值30。其垂直與水平方向的邊緣檢測(cè)硬件結(jié)構(gòu)圖分別如圖7(a)和(b)所示。

2.2.3 擴(kuò)散濾波

視頻中的圖像幀通常帶有時(shí)域和空域的噪聲,因此,首先需要對(duì)其進(jìn)行平滑去噪處理。通常情況下使用的是雙邊濾波,雙邊濾波是結(jié)合圖像的空間臨近度和像素值相似度的一種折中方法,離得較遠(yuǎn)的點(diǎn)不會(huì)對(duì)邊緣上的像素值造成太大影響,具有簡(jiǎn)單、非迭代、局部的特點(diǎn),可以實(shí)現(xiàn)邊緣保存,而維納濾波和高斯濾波都會(huì)有明顯的模糊邊緣。本文采用一種和雙邊濾波的局部特點(diǎn)相似的方法,將圖像分成2×2的小塊,同時(shí)進(jìn)行時(shí)域和空域的均值濾波。

首先進(jìn)行時(shí)間域?yàn)V波。這個(gè)模塊會(huì)把當(dāng)前像素點(diǎn)的值與過去該點(diǎn)的值做平均計(jì)算,其中過去的值存儲(chǔ)在一個(gè)FPGA上的block ram模塊里面,因?yàn)橄到y(tǒng)最后會(huì)把低位全部置為1,所以低位并沒有必要做處理,因此每個(gè)像素點(diǎn)只存RGB的高4位。本文決定使用4幀圖像來做平均值計(jì)算,因?yàn)檫@樣系統(tǒng)只需要將當(dāng)前值的1/4與過去值的3/4相加即可,而過去值的3/4可以表示為1減去1/4,這有利于FPGA實(shí)現(xiàn),將除法運(yùn)算變成了簡(jiǎn)單的移位運(yùn)算。公式如下所示:

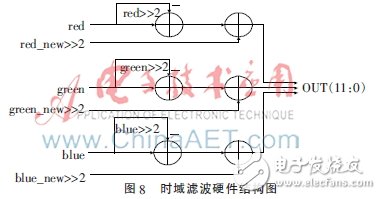

硬件實(shí)現(xiàn)如圖8所示。

然后進(jìn)行空間域的均值濾波。本文將圖像劃分為2×2的小塊,每次濾波都以這種小塊為基礎(chǔ),這個(gè)特點(diǎn)類似于雙邊濾波器的局部特性,有利于做到邊緣保持。具體做法是:先設(shè)計(jì)兩個(gè)計(jì)數(shù)器,用來模擬圖像的行計(jì)數(shù)Y與列計(jì)數(shù)X,然后將X與Y方向坐標(biāo)的最低位移除以產(chǎn)生block ram模塊的地址,這樣就使相鄰的4個(gè)點(diǎn)都參考block ram模塊的同一個(gè)點(diǎn)。使用此方法可以減少FPGA上實(shí)現(xiàn)block ram模塊的資源大小,節(jié)約資源。由于block ram模塊的讀和寫各需要一個(gè)時(shí)鐘周期,如果要做濾波,每個(gè)時(shí)鐘周期都需要從block ram模塊里面讀出一個(gè)舊值,同時(shí)還要存入前一個(gè)時(shí)鐘變化后的值,這就導(dǎo)致了一定的時(shí)序問題,但是由于系統(tǒng)是以2×2的塊進(jìn)行濾波,相鄰的四個(gè)點(diǎn)參考同一個(gè)點(diǎn),因此系統(tǒng)就可以用一個(gè)時(shí)鐘讀出block ram模塊里的數(shù)據(jù)并做處理,處理后的數(shù)據(jù)暫存在寄存器中,第二個(gè)時(shí)鐘周期到來的時(shí)候就可以將剛才寄存器中的數(shù)據(jù)拿來參加計(jì)算而不必重新從block ram模塊中讀出數(shù)據(jù)。與此同時(shí),利用列計(jì)數(shù)X的最低位來控制將變化后的數(shù)據(jù)存進(jìn)block ram模塊,以達(dá)到時(shí)序的匹配。至此,濾波結(jié)束。整個(gè)流程的硬件結(jié)構(gòu)如圖9所示。

2.2.4 量化光照信息

由于量化光照信息算法復(fù)雜度較高,不利于在FPGA上實(shí)現(xiàn),本文只簡(jiǎn)單地將紅綠藍(lán)通道低位全部置1。而人眼對(duì)綠色分量變化敏感,所以對(duì)綠色通道保留高4位的有效信息,紅和藍(lán)通道只保留高3位的信息,這樣做可以忽略色彩變化不明顯的區(qū)域,達(dá)到量化光照信息的目的。

3 實(shí)驗(yàn)結(jié)果

、

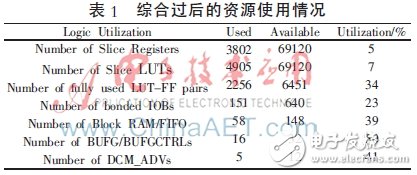

由于相機(jī)分辨率限制,本文只對(duì)分辨率為640×480、幀率為60 f/s的視頻進(jìn)行驗(yàn)證。由于NPR模塊需要緩存三行數(shù)據(jù),處理時(shí)鐘為64.8 MHz,所以總延時(shí)t可由式(8)計(jì)算得30 ?滋s,達(dá)到了實(shí)時(shí)處理的效果。由前面的算法分析知本系統(tǒng)采用流水線結(jié)構(gòu),時(shí)延小,完全可以對(duì)分辨率更高、幀率更高的視頻做實(shí)時(shí)NPR渲染。本系統(tǒng)在ISE下綜合之后的資源利用率如表1所示,系統(tǒng)僅消耗了整個(gè)FPGA slice資源的5%。但是由于要在FPGA上暫存1/4幀的圖像以及三行完整的圖像數(shù)據(jù),所以消耗了39%的Block RAM資源。如果圖像更大,可以考慮在FPGA外圍加上SRAM芯片,這樣可以避免占用太多FPGA片上的Block RAM資源。

4 結(jié)論

非真實(shí)感渲染技術(shù)越來越多地被應(yīng)用到各個(gè)領(lǐng)域中。本文使用VHDL語言設(shè)計(jì)了基于FPGA的實(shí)時(shí)NPR系統(tǒng),該系統(tǒng)在自行研發(fā)的以Virtex-5 FPGA為核心的高速圖像處理平臺(tái)上得到了實(shí)現(xiàn),并且具體分析了NPR算法的硬件實(shí)現(xiàn)流程及方法。由實(shí)驗(yàn)結(jié)果可知,該系統(tǒng)實(shí)時(shí)性好、體積小、便于攜帶,具有較強(qiáng)的工程應(yīng)用價(jià)值。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論