本文是電子發燒友網整理的最受工程師喜愛的ARM設計方案精華集錦,包括基于ARM的遠程無線視頻監控系統設計、基于Linux系統和ZigBee的智能家居系統方案、基于ARM微處理器的液晶觸摸屏接

2012-08-13 08:50:50 8711

8711 作為全球創新通信測試與測量解決方案供應商,安立生產的眾多測試設備已為世界多家移動通信設備制造商采用,對移動通信系統的發展做出了巨大貢獻。本文是關于安立LTE測試解決方案的精華集錦。

2013-03-11 16:51:13 4472

4472 40種彩電常見故障與維修(精華免費版)

2012-08-16 15:21:49

FPGA CPLD同步設計若干問題淺析摘要:針對FPGA/CPLD同步設計過程中一些容易被忽視的問題進行了研究,分析了問題產生的原因、對可靠性的影響,并給出了解決方案。關鍵詞:FPGA/CPLD

2009-04-21 16:42:01

FPGACPLD中常見模塊設計精華集錦

2012-08-17 22:22:42

`學習FPGA|CPLD|ASIC必須選擇好的參考書籍,好的書籍在知識的講解上邏輯清晰,編排合理。能夠對學習者起到添磚加瓦的作用。一本好的參考書對PLD、HDL的初學者是非常必要的,版主推薦初學者

2012-02-27 11:31:10

FPGA、CPLD常用protel庫FPGA&CPLD_LIB.ddb

2012-08-11 10:32:00

FPGA與CPLD的區別是什么,他與單片機的區別呢

2012-10-07 22:01:57

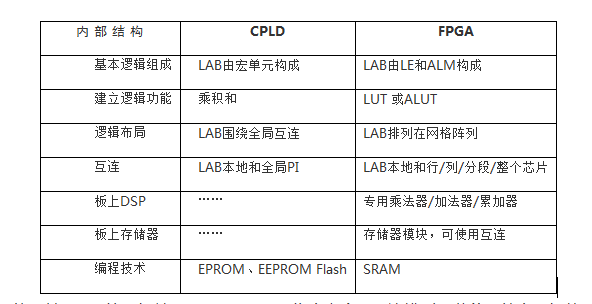

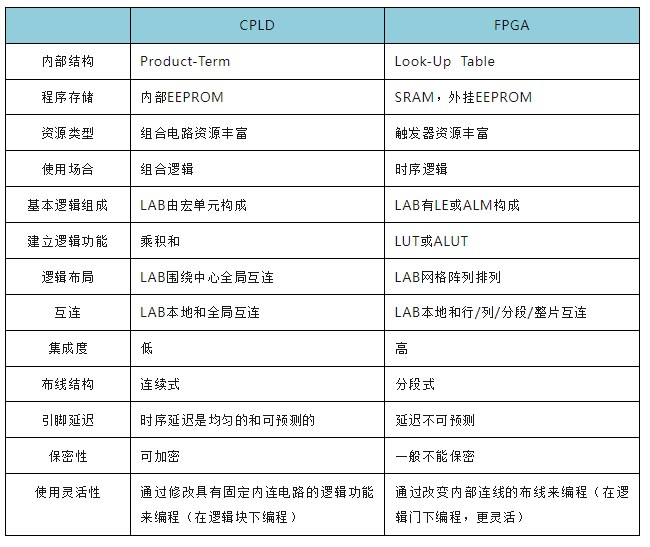

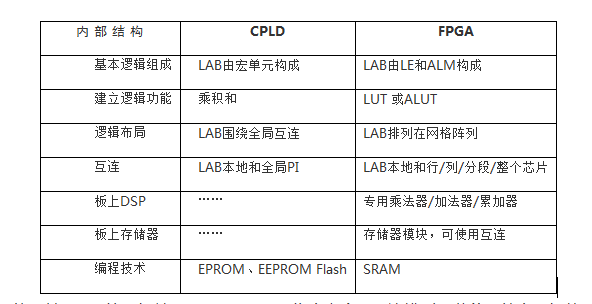

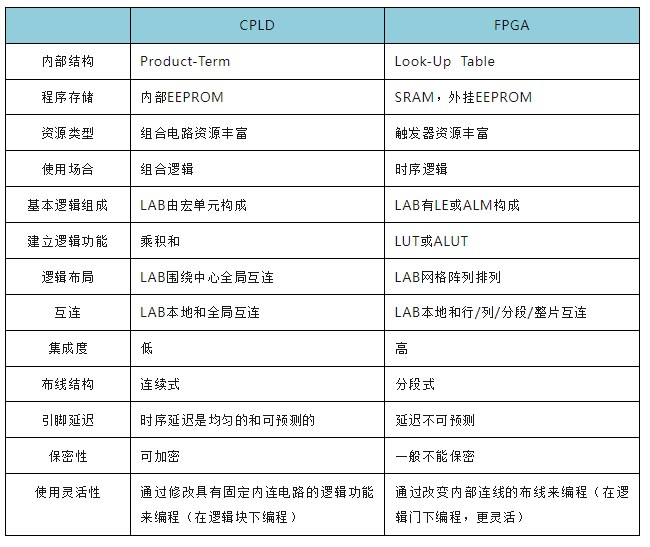

FPGA與CPLD的辨別和分類主要是根據其結構特點和工作原理。通常的分類方法是:將以乘積項結構方式構成邏輯行為的器件稱為CPLD,如Lattice的ispLSI系列、Xilinx的XC9500系列

2019-07-01 07:36:55

FPGA與CPLD的區別

盡管很多人聽說過CPLD,但是關于CPLD與FPGA之間的區別,了解的人可能不是很多。雖然FPGA與CPLD都是“可反復編程的邏輯器件”,但是在技術上卻有一些差異。簡單

2011-09-27 09:49:48

盡管很多人聽說過FPGA和CPLD,但是關于FPGA與CPLD之間的區別,了解的人可能不是很多。雖然FPGA與CPLD都是“可反復編程的邏輯器件”,但是在技術上卻有一些差異。簡單地說,FPGA就是將

2019-02-21 06:19:27

的路徑。這就是為何CPLD被認為是“邏輯豐富”型的。宏單元以邏輯模塊的形式排列(LB),每個邏輯模塊由16個宏單元組成。宏單元執行一個AND操作,然后一個OR操作以實現組合邏輯。每個邏輯群有8個邏輯模塊

2012-10-26 08:10:36

一、FPGA與CPLD的基本概念1.CPLD CPLD主要是由可編程邏輯宏單元(LMC,Logic Macro Cell)圍繞中心的可編程互連矩陣單元組成,其中LMC邏輯結構較復雜,并具有復雜的I

2020-08-28 15:41:47

FPGA典型設計方案精華匯總

2012-08-16 16:29:32

函數功能) CPLD(Complex Programmable Logic Device 復雜可編程邏輯器件,內部結構為“與或陣列”。該結構來自于典型的PAL、GAL器件的結構。任意一個組合邏輯都可以

2020-07-16 10:46:21

盡管很多人聽說過FPGA和CPLD,但是關于FPGA與CPLD之間的區別,了解的人可能不是很多。雖然FPGA與CPLD都是“可反復編程的邏輯器件”,但是在技術上卻有一些差異。簡單地說,FPGA就是將

2015-03-12 13:54:42

FPGA實驗(精華)

2012-05-08 11:00:10

本帖最后由 eehome 于 2013-1-5 10:00 編輯

好東西要與大家一起分享FPGA實驗(精華) 適合各種人群

2012-07-17 10:50:57

用vhdl實現cpld配置fpga,配置成功后在usermode下設置一個重新配置信號,當信號有效時對fpga進行重新配置;fpga配置程序放在flash內;現在遇到的問題是,上電cpld能夠正常配置fpga并且進入usermode ,但是加上重新配置語句過后就不能成功配置fpga,求高人指點~

2013-01-17 22:35:39

Altera FPGA/CPLD設計與Verilog數字系統設計教程從網上找到了一些Altera FPGA/CPLD經典教材,包含夏宇聞老師的Verilog數字系統設計教程(第2版)Altera FPGA/CPLD設計與Verilog數字系統設計教程

2014-02-17 09:22:18

C語言中有幾種基本數據類型呢?C語言中常見的數據溢出情況有哪些?

2022-02-25 07:55:32

本文討論了HDMI I/O設計和測試中常見到的和需要注意的問題以及解決的方法。

2021-06-02 06:28:52

LED驅動電源測量中常見技術有哪些

2021-03-11 08:11:38

LLC諧振變換器中常見MOSFET失效模式有哪幾種?怎么解決?

2021-09-18 07:30:41

本帖最后由 eehome 于 2013-1-5 10:11 編輯

Proteus常見問題精華集錦

2012-08-20 23:16:05

QuartesⅡ時序分析中常見的時間參數有哪些?

2021-09-18 08:41:47

XILINX FPGA/CPLD ISE下載教程 第一章 XILINX FPGA/CPLD ISE下載教程——下載.bit文件第二章 XILINX FPGA/CPLD ISE下載教程——燒錄Flash 圖文詳細資料!

2019-08-15 00:32:31

`內容簡介· · · · · ·CPLD/FPGA是目前應用最為廣泛的兩種可編程專用集成電路(ASIC),特別適合于產品的樣品開發與小批量生產。本書從現代電子系統設計的角度出發,以全球著名

2018-03-29 17:11:59

使用SPI對SD卡進行讀寫過程中常見的問題有哪些?如何解決?

2022-01-27 07:17:56

本帖最后由 eehome 于 2013-1-5 09:49 編輯

單片機設計經驗技巧精華集錦

2012-08-16 15:42:22

單片機設計經驗技巧精華集錦

2012-08-15 20:49:41

電子工程師_硬件單片機設計經驗技巧精華集錦

2013-08-03 18:43:48

討論一個在無線移動數據接收中常見的問題。

2021-04-14 06:48:09

MEMS陀螺儀信號中的常見噪聲源評估MEMS陀螺儀信號中常見噪聲源的簡單流程

2021-03-08 06:17:12

`實用電源電路精華集錦【史上最全半橋LLC諧振式開關電源視頻教程】開始預售啦,趕緊猛戳下方鏈接:http://t.elecfans.com/topic/65.html?elecfans_trackid=oxh`

2012-08-20 23:05:11

分享:嵌入式C-C++語言精華文章集錦.pdf

2012-07-05 22:58:14

嵌入式CC++語言精華文章集錦

2012-08-03 08:45:45

本文討論的四種常用FPGA/CPLD設計思想與技巧:乒乓操作、串并轉換、流水線操作、數據接口同步化,都是FPGA/CPLD 邏輯設計的內在規律的體現,合理地采用這些設計思想能在FPGA/CPLD設計工作種取得事半功倍的效果。

2021-04-29 06:04:14

平衡小車在移植過程中常見的問題有哪些?

2021-11-10 06:19:42

開關電源中常見的元器件有哪些?

2021-11-10 07:33:48

微機中常見的各類總線技術有哪幾種?

2021-10-14 06:28:52

數字系統的設計人員擅長在其印制電路板上用FPGA和CPLD將各種處理器、存儲器和標準的功能元件粘合在一起來實現數字設計。除了這些數字功能之外,FPGA和CPLD還可以使用LVDS輸入、簡單的電阻電容(RC)電路和一些FPGA或CPLD的數字邏輯單元實現共模功能,從而構建模數轉換器(ADC)。

2019-08-19 06:15:33

屬于系統總線的有哪幾種?什么是總線復用?總線復用有何功能?總線特性包括哪幾種?控制總線中常見的控制信號包括哪些?

2021-08-11 07:28:49

本帖最后由 eehome 于 2013-1-5 10:07 編輯

最受工程師喜愛的ARM設計方案精華集錦

2012-08-15 19:04:11

點擊率最高太陽能應用電路圖精華集錦

2012-08-20 17:26:04

。--- 串行外設用到RS232-C異步串行接口,一般采用專用的集成電路即UART實現。如8250、8251、NS16450等芯片都是常見的UART器件,這類芯片已經相當復雜,有的含有許多輔助的模塊(如FIFO

2012-05-23 19:37:24

電子設備設計研發中常見的問題有哪些?

2021-05-08 09:22:17

電源中常見的故障現象如何維修

2021-03-11 07:24:44

算法移植到STM32單片機中常見的問題有哪些?

2021-11-22 07:10:19

推薦使用)。成本提高了N倍不說,還給生產、文檔等工作增添數倍的工作。 常見問題四:我們的系統要求這么高,包括MEM、CPU、FPGA等所有的芯片都要選最快的 通用辦法:在一個高速系統中并不是每一部分都工作

2017-02-04 09:23:54

高壓連接器設計中常見的故障有哪些?如何解決這些問題?

2021-06-08 06:43:32

的見解!HarmonyOS開箱直播精華問答(一) HarmonyOS開箱直播精華問答(二)HarmonyOS開箱直播精華問答(三)HarmonyOS開箱直播精華問答(四)HarmonyOS開箱直播精華

2020-10-10 15:13:01

《Altera FPGA/CPLD設計(高級篇)》結合作者多年工作經驗,深入地討論了Altera FPGA/CPLD的設計、優化技巧。在討論FPGA/CPLD設計指導原則的基礎上,介紹了Altera器件的高級應用;引領讀者

2009-02-12 09:19:12 4799

4799 altera fpga/cpld設計 基礎篇結合作者多年工作經驗,系統地介紹了FPGA/CPLD的基本設計方法。在介紹FPGA/CPLD概念的基礎上,介紹了Altera主流FPGA/CPLD的結構與特點,并通過豐富的實例講解

2009-07-10 17:35:45 57

57 WinCE 驅動開發問題精華集錦:在mediaplayer 全屏播放的時候,我可以用鍵盤上的某一個鍵調節聲音大小,現在我想在屏幕上顯示調節的結果就跟我們看電視一樣能出來一些標記。當聲音

2009-09-28 12:19:46 46

46 UART 是廣泛使用的串行數據通訊電路。本設計包含UART 發送器、接收器和波特率發生器。設計應用EDA 技術,基于FPGA/CPLD 器件設計與實現UART。關鍵詞 :FPGA/CPLD;UART;VHDLUART(即U

2009-09-29 08:01:20 23

23 嵌入式C/C++語言精華文章集錦

面對一個人的大型C/C++程序時,只看其對struct 的使用情況我們就可以對其編寫者的編程經驗進行評估。因為一個大型的C/C++程序,勢

2010-03-10 09:06:02 91

91 攝像頭使用常見問題集錦

隨著網絡視頻聊天的熱潮侵襲,攝像頭已經成為了網民密不可分的工具。不過大家在使用時還是能夠遇見一些常見的問

2010-02-24 13:47:31 360

360 常用FPGA/CPLD四種設計技巧

FPGA/CPLD的設計思想與技巧是一個非常大的話題,本文僅介紹一些常用的設計思想與技巧,包括乒乓球操作、串并轉換、流水線操作和數據接口

2010-05-12 11:10:43 766

766

本文討論的四種常用FPGA/CPLD設計思想與技巧:乒乓操作、串并轉換、流水線操作、數據接口同步化,都是FPGA/CPLD邏輯設計的內在規律的

2010-11-04 10:11:28 625

625

在本專題的《嵌入式電路圖精華集錦》中,電子發燒友網將為大家奉上嵌入式接口、單片機、應用方案和熱門電路圖,以期在進行嵌入式設計時有參考借鑒意義。

2012-06-15 17:13:25

《逆變器的作用_車載逆變器-應用精華集錦》技術專題內容涵蓋逆變器工作原理、逆變器的作用、逆變器應用分類(電源逆變器、車載逆變器、大功率逆變器、光伏逆變器、太陽能逆變器)、逆變器電路圖以及逆變器制作。本專題內容豐富、實用、整合性強,是電子發燒友必備的資料大全。

2012-07-13 10:26:23

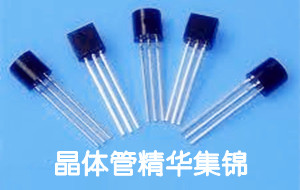

《晶體管精華集錦》技術專題主要介紹了晶體管新品資訊、晶體管原理、晶體管手冊、晶體管電路圖、晶體管電路設計、晶體管應用(主要含晶體管收音機、晶體管測試儀)以及常見的晶體管(如:場效應晶體管,mos晶體管,絕緣柵雙極晶體管等)。本專題內容豐富、包羅萬象,希望對各位有所幫助!

2012-08-03 09:12:48

電子發燒友網核心提示 :本文是電子發燒友網小編從電子發燒友網論壇FPGA論壇找到的一篇關于Quartus II 9.0版本常見問題集錦。在此跟大家一起分享。本文原文如下:之前已經接觸QUART

2012-10-24 16:44:08 7498

7498

電子發燒友網核心提示:本文是關于ADI數據轉換器基礎知識精華集錦,其中闡述了逐次逼近模數轉換器的基本原理、算法及優缺點;ADC和DAC的直流規格和交流規格分析;DAC數模轉換

2012-10-30 15:32:26 8653

8653 FPGA論壇精華帖摘選,主要是講述驗證、仿真方面的技術。

2015-11-30 17:41:48 0

0 FPGA和CPLD的區別,以及設計思路思想

2016-02-17 11:20:56 38

38 CPLD和FPGA的區別,好東西,喜歡的朋友可以下載來學習。

2016-02-19 16:59:55 0

0 嵌入式 C C++語言精華文章集錦

2017-02-08 01:28:39 10

10 基于FPGA/CPLD的UART功能設計

2017-01-23 20:45:37 30

30 CPLD和FPGA都是我們經常會用到的器件。有的說有配置芯片的是FPGA,沒有的是CPLD;有的說邏輯資源多的是FPGA,少的是CPLD;有的直接就不做區分,把他們都叫做FPGA。那么兩者到底有什么區別呢?下面我們就以Altera公司的CPLD和FPGA為例來說說兩者的區別。

2017-09-18 16:35:32 5

5 使用GPS模塊過程中常見的4個問 1、GPS模塊的66個捕獲通道是什么含義?

GPS模塊有一個通道數量的參數,例如最新型的為66個捕獲通道,它表示該模塊最大可以同時和66顆衛星建立通訊,模塊只有同時收到3顆以上衛星信號后,經過復雜運算后才能獲得正確的定位數據。

2017-09-27 15:08:44 6

6 FPGA/CPLD能完成任何數字器件的功能,上至高性能CPU,下至簡單的74電路,都可以用FPGA/CPLD來實現。 FPGA/CPLD如同一張白紙或是一堆積木,工程師可以通過傳統的原理圖輸入法

2017-10-09 09:52:20 14

14 FPGA(Field-Programmable Gate Array),即現場可編程門陣列,它是在PAL、GAL、CPLD等可編程器件的基礎上進一步發展的產物。它是作為專用集成電路(ASIC)領域

2017-10-24 10:04:00 46702

46702 嵌入式C/C++語言精華文章集錦

2017-10-27 14:48:47 65

65 FPGA LAB和CPLD的LAB設計不同。CPLD LAB由宏單元構成,包括自己的本地可編程陣列,而FPGA LAB由大量的邏輯模塊構成,這些模塊被稱為邏輯單元,即LE,而且本地互連和邏輯分開。LE看起來可能和CPLD宏單元相似,但更容易配置,有更豐富的特性來提高性能,減少邏輯資源的浪費。

2018-04-17 17:02:00 1979

1979

PLD和FPGA都是由邏輯陣列模塊構成的,但是CPLD LAB基于乘積和宏單元,而FPGA LAB使用基于LUT的邏輯單元。CPLD LAB圍繞中心全局互連排列,隨著器件中邏輯數量的增加,呈指數增長。

2018-04-17 17:08:00 2951

2951

集中式數據中心與邊緣計算白皮書精華集錦

2018-03-01 09:39:58 3

3 CPLD和FPGA都是我們經常會用到的器件。有的說有配置芯片的是FPGA,沒有的是CPLD;有的說邏輯資源多的是FPGA,少的是CPLD;有的直接就不做區分,把他們都叫做FPGA。那么兩者到底有什么區別呢?下面我們就以Altera公司的CPLD和FPGA為例來說說兩者的區別。

2018-05-24 02:03:00 49472

49472

本文檔詳細介紹的是FPGA教程之CPLD與FPGA的基礎知識說明主要內容包括了:一、復雜可編程邏輯器件簡介二、CPLD的組成與特點三、FPGA的組成與特點四、CPLD與FPGA的異同五、主要的PLD廠商

2019-02-27 17:09:32 32

32 本文檔詳細介紹的是FPGA教程之CPLD和FPGA的配置與下載的詳細資料說明主要內容包括了:一、CPLD/FPGA器件的配置,二、MAX系列非易失性器件的下載配置,三、FLEX/ACEX系列FPGA的下載配置,四、ALTERA的編程文件

2019-02-28 09:56:18 17

17 FPGA/CPLD能完成任何數字器件的功能,上至高性能CPU,下至簡單的74電路,都可以用FPGA/CPLD來實現。

2020-01-20 09:29:00 3264

3264 I/O單元、基本邏輯單元、布線池和其他輔助功能模塊構成。 可編程邏輯單元 作用與FPGA的基本I/O口相同,但是CPLD應用范圍局限性較大,I/

2020-09-25 14:56:33 12233

12233

CPLD/FPGA的基本知識講解。

2021-03-30 09:55:18 27

27 Altera FPGA CPLD學習筆記(肇慶理士電源技術有限)-Altera FPGA CPLD學習筆記? ? ? ? ? ? ? ? ?

2021-09-18 10:54:41 79

79 FPGA CPLD數字電路設計經驗分享.(電源技術發展怎么樣)-FPGA CPLD數字電路設計經驗分享? ? ? ? ? ? ? ? ? ??

2021-09-18 10:58:03 51

51 FPGA CPLD中的Verilog設計小技巧(肇慶理士電源技術有限)-FPGA CPLD中的Verilog設計小技巧? ? ? ? ? ? ? ? ?

2021-09-18 16:49:18 35

35 數據接口的同步是 FPGA/CPLD 設計的一個常見問題,也是一個重點和難點,很多設計不穩定都是源于數據接口的同步有問題。在電路圖設計階段,一些工程師手工加入 BUFT 或者非門調整數據延遲,從而保證本級模塊的時鐘對上級模塊數據的建立、保持時間要求。

2022-12-01 09:38:52 724

724 都是FPGA/CPLD邏輯設計的內在規律的體現,合理地采用這些設計思想能在FPGA/CPLD設計工作種取得事半功倍的效果。

2023-05-18 08:56:57 350

350

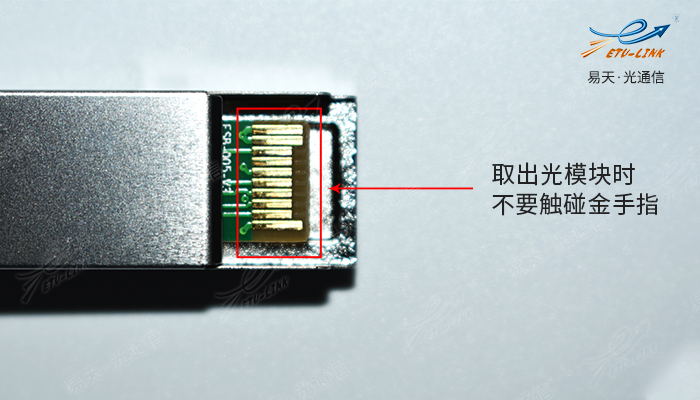

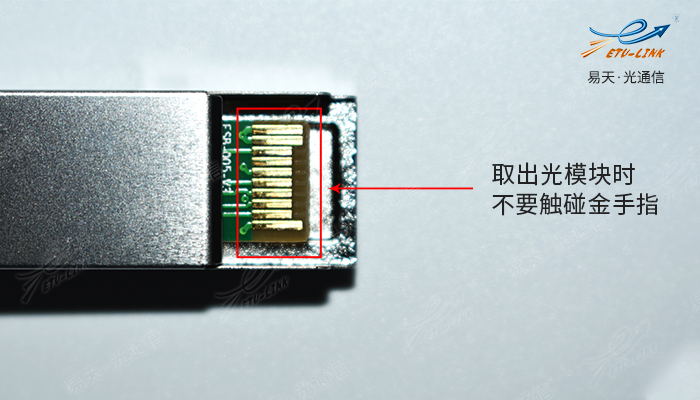

光模塊是一種較為敏感的光學器件,在使用過程中常常會出現很多問題,在本文中將光模塊的一些常見問題進行了匯總。

2023-05-23 16:08:35 911

911

CPLD和FPGA都是由邏輯陣列模塊構成的,但是CPLD的LAB基于乘積和宏單元,而FPGA的LAB使用基于LUT的邏輯單元。

2023-06-28 11:28:04 862

862

原文標題:精華集錦!重溫紫光同芯2023MWC上海精彩時刻 文章出處:【微信公眾號:紫光同芯】歡迎添加關注!文章轉載請注明出處。

2023-07-01 22:30:01 289

289

可編程邏輯包括 PAL、GAL、PLD 等。通過不斷發展,它已經發展成為現在的CPLD/FPGA。CPLD(復雜可編程邏輯器件)和FPGA(現場可編程門陣列)的功能基本相同,只是實現原理略有不同

2023-07-03 14:33:38 6041

6041

直線導軌使用中常見的問題有哪些?

2023-08-03 17:43:35 722

722

CPLD和FPGA都是由邏輯陣列模塊構成的,但是CPLD的LAB基于乘積和宏單元,而FPGA的LAB使用基于LUT的邏輯單元。CPLD的LAB圍繞中心全局互連排列,隨著器件中邏輯數量的增加,呈指數

2024-01-23 09:17:04 280

280

電子發燒友App

電子發燒友App

評論