在各種不同的場合中,人們需要將大批數據從一個設備無差錯地傳輸到另一個設備上。對于設備間距離較近的場合,可以選擇PCIE(典型距離是15~30 cm)或者USB(最長傳輸距離5 m)等接口。而對于距離較遠的場合,可以選擇RS232、RS485、以太網等傳輸介質,并在此基礎上,通過上層協議來保證數據的可靠性。上層協議通常用檢錯重傳機制來實現數據的可靠傳輸,如TFTP、TCP/IP、SCTP以及可靠UDP等。這些協議都必須依靠較為復雜的CPU運算和內存拷貝來實現數據可靠傳輸的功能。比如在Linux下,TCP/IP協議每發送一個數據包,CPU需要執行約14 000條指令[1]。因此CPU的工作頻率、內存的讀寫速度、硬件I/O帶寬都會影響TCP/IP的速度。一些嵌入式系統上TCP性能測試如表1所示。

CPU處理能力越強,TCP傳輸速度越高。與此同時,在最大傳輸單元為9 000 B時(即相對MTU1 500包長度增加6倍,包處理頻度下降6倍),則傳輸速度大幅提高。這也從側面說明了CPU處理能力對TCP傳輸速度的影響。

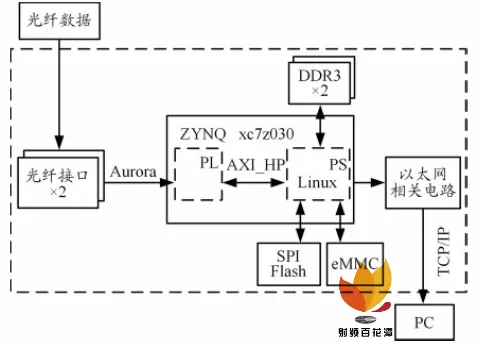

在點對點傳輸和局域網傳輸中,往往不需要完善的路由機制和流量控制,但同樣需要一種可靠的數據傳輸手段。傳統的TCP協議依賴CPU運算的特性,使得傳輸速度受到限制,并且受CPU負荷變化影響而速率不穩定[2]。從提高傳輸效率和減輕對CPU的依賴兩方面考慮,提出一種基于硬件實現的高速可靠數據傳輸方法,將CPU從頻繁的協議運算中解放出來。該方法可以在千兆以太網PHY所提供的物理層通信鏈路的基礎上,通過編寫FPGA邏輯,在硬件上實現可靠數據傳輸的協議,然后使用如PCIE這樣的接口將數據提供給計算機系統。系統結構如圖1所示。

1 選擇重發機制提供可靠數據傳輸保證

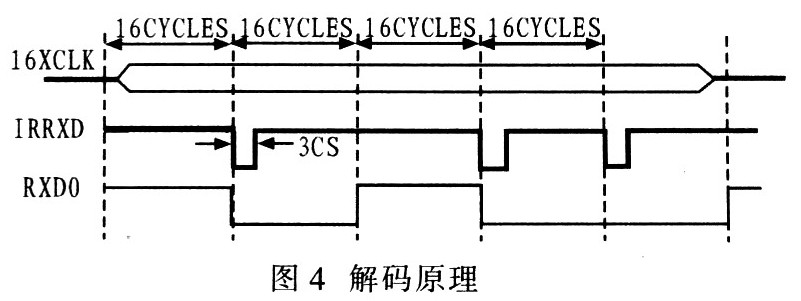

數據傳輸過程中的可靠性有多種方式,如糾錯碼、信息反饋和檢錯重發機制。選擇重發是檢錯重發的實現方法之一,相對于等待重發和退回重發,它具有高效率的特點,因而被廣泛采用。比如在TCP/IP網絡中,就是用檢錯重發機制的原理。但TCP協議中包括較為復雜的流量控制機制和擁塞控制機制,它們被設計來應對異構的、大范圍的復雜網絡環境。而在點對點傳輸的應用中,或者在任務明確、拓撲簡單的局域網中,不需要復雜的路由機制和流量控制,因而可以簡化被廣泛使用的檢錯重傳機制,使得可靠性協議可以通過硬件實現。 如圖2所示,將數據可靠傳輸的過程概括如下:

(1)待發送的數據在發送端打包,加上必要的識別信息和校驗信息,存入發送端的緩存;

(2)待以太網信道可用之后將數據包通過千兆以太網發送給接收方;

(3)接收方收到數據包之后對內容進行校驗,確認數據無誤之后將識別信息通過ACK數據包反饋給發送方;

(4)發送方的緩存接收識別信息后確認數據已安全抵達接收方,清空緩存等待發送下一個數據包;

(5)發送方在設定的時間內沒有接收到帶有相應識別信息的ACK反饋,則進行重新發送,重發超過一定次數則報錯。

校驗信息選擇使用和以太網兼容的CRC32,編碼冗余度較低(為0.26%)。可以預見,在一般的誤碼率情況下(1×10-10),該方法可以實現高速的可靠傳輸[4]。

2 可靠數據傳輸的硬件實現

用硬件的方式實現所述的可靠傳輸,將會極大地降低對發送方和接收方在協議運算上對CPU資源的依賴,這點與TCP協議大為不同。 如圖3所示,相較于TCP協議,硬件協議在接收數據時數據流大大簡化。

TCP協議的數據流:

(1)網卡接收以太網數據通過PCIE以DMA的方式寫入上位機內存,并觸發中斷;

(2)網絡包內存拷貝進入OS協議層;

(3)對網絡包的協議運算,檢查包頭信息和CRC校驗等;

(4)確定無誤后發送ACK包;

(5)將有效數據提供給上層用戶。

硬件協議的數據流:

(1)設備卡FPGA檢驗數據正確性自發產生ACK回應包,將有效數據通過PCIE以DMA的方式寫入上位機內存,可選擇觸發中斷或輪詢;

(2)驅動層直接將數據提供給用戶。

發送過程與接收過程相反,情況類似,不再贅述。可見,利用FPGA實現的硬件協議省去了上位機軟件協議運算和內存拷貝,直接將有效數據提供給上層用戶,提高了數據傳輸的效率和速度,極大地減輕了CPU運算負荷,省去了對CPU的頻繁中斷,從而獲得不依賴于CPU性能的穩定高速的可靠數據傳輸。這點是軟件協議優化難以實現的。

2.1 硬件平臺設計

PCIE接口設備卡,搭載Xilinx Spartan 6 FPGA和Broadcom千兆以太網PHY芯片。FPGA是設備的核心。在FPGA上部署PCIE接口模塊和Ethernet接口模塊,并設計內部邏輯實現數據的可靠傳輸。

2.2 FPGA邏輯模塊的設計

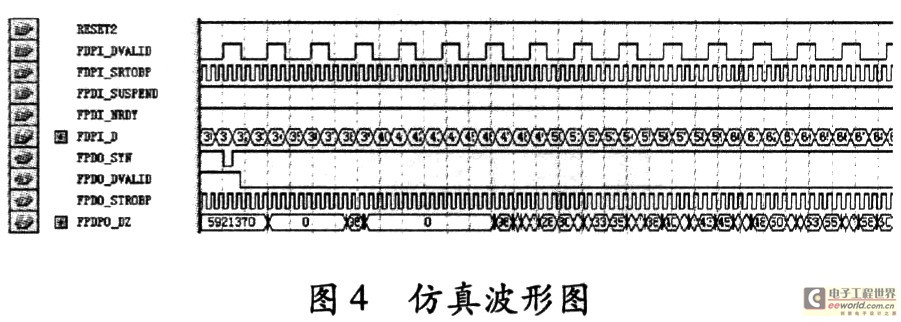

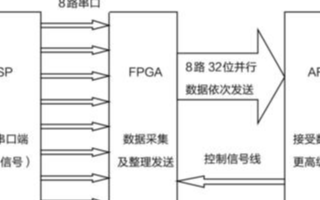

FPGA的邏輯設計需要保證數據流的順暢,各個模塊的互聯。采用硬件算法,實現對數據的分組打包和節點間的應答握手機制,保證每個數據包正確無誤地抵達目標設備。FPGA內部的邏輯結構如圖4所示,其中對于數據的可靠傳輸是在Tx和Rx模塊中的狀態機控制下實現的,Ethernet模塊為Xilinx的TriMode Ethernet MAC Core,提供了對各種速率(10/100/1 000 M)的以太網PHY的支持。位于邏輯核心區域的InterConnect模塊為多個端口之間提供了可動態配置的互聯,因而為可能的網絡拓撲提供支持。PCIE模塊為上位機提供了訪問FPGA 的數據和命令通道。

FPGA各個模塊的說明:

(1)PCIE,使用Xilinx的s6_pcie:2.4 Logic Core[5]。開辟兩個用戶地址空間,一個用于訪問內部狀態控制寄存器,另一個用于訪問FPGA數據。

(2)InterConnect,在內部寄存器的控制下,將各個Ethernet端口和上位機數據端口按照一定的規則互聯起來,可以做到指定端口之間的轉發和特定端口的收發操作。并且在verilog編碼中采用參數化的風格,方便多端口的擴展。這樣,在上位機控制軟件的配合下,可以實現多個端口之間的靈活轉發,因而可以方便地組建數據傳輸網絡。InterConnect數據位寬可靈活配置,對于千兆網應用可配置為16位寬。該模塊包括FPGA內部其他模塊,時鐘頻率為75 MHz。

(3)Tx模塊,其他端口的轉發數據或者上位機的發送數據經由InterConnect傳送到Tx模塊中,在Tx模塊的邏輯調度下以數據包為單位暫存在某一個Buffer中。每個Buffer都有獨立的狀態機控制。數據包在Buffer中準備好之后會在Tx模塊的邏輯調度下發送至Ethernet模塊,相應的Buffer狀態機處于等待ACK的狀態。在計數器超時后觸發重傳,重傳一定次數依然沒有正確ACK回應則報錯。每個Tx模塊中可以參數化地配置多個Buffer,通過多個Buffer的協作可以極大地提高信道利用效率。

(4)Rx模塊,內部邏輯維護一個類似FIFO的存儲結構。每當接收一個數據幀時,通過累加寫指針將數據暫存入RAM中,并在狀態機控制下記錄當前幀的目的/源地址、幀類型,序號等信息。如果是ACK幀則把相應的幀識別信息傳遞給Tx模塊;如果是需要接收的幀則在幀接收完后指示存儲器數據有效,數據有效信號將促使待轉發模塊或者CPU接收FIFO讀取該幀。Rx和Tx的以太網端口數據位寬為8位,接口時鐘頻率為125 MHz。

(5)Ethernet模塊,使用Xilinx的tri_mode_eth_mac:4.6 Logic Core[6]。該模塊提供CRC32編碼和校驗功能,提供對不同速率以太網的支持,并且對內部邏輯提供統一的數據接口。3 系統性能測試為了盡可能完善地測試系統性能,從邏輯仿真和實測兩方面進行測試。

3.1 邏輯仿真測試

邏輯仿真是利用Xilinx ISim仿真器對FPGA邏輯的行為進行仿真預測。

仿真測試的優點是測試準備簡單,測試方法靈活;缺點是只能仿真FPGA邏輯部分,無法仿真其他硬件。

考慮到本數據傳輸系統的核心在FGPA上,并通過與實測數據比對,邏輯仿真可以在很大程度上真實反映系統性能。測試的是兩個節點之間的點對點傳輸。

(1)固定幀長1 024 B測試結果:帶寬利用效率為96.4%,數據傳輸速度為120.5 MB/s。

(2)隨機幀長測試結果:數據傳輸速度為99.4 MB/s,帶寬利用效率為79.5%。

仿真波形如圖5所示,rgmii_txen_A信號表明在這種情況下信道利用出現間隙。這是由于幀長度突然變長,需要等待內部數據寫入Buffer。這種特殊情況可以通過增加Tx_buffer的數量來解決。

(3)人為添加誤碼測試結果:數據傳輸速度為106.7 MB/s,帶寬利用效率為85.3%。

測試幀長度為1 024 B,設定FPGA在發送端口隨機添加誤碼,測試添加誤碼率為0.000 76%。一般情況下誤碼率很低(平均一個誤碼造成一個數據包重傳)。單次誤碼造成的等待和重傳開銷是一定的,因而傳輸速度的變化值與誤碼率的關系可以近似看成正比關系(?駐x:傳輸速率比變化;?駐e:誤碼率):?駐x=k?駐e。

測試時,人為添加誤碼率?駐e=0.000 76%,?駐x=-13.8 MB/s,求得k=-1.82×106 MB/s。由此估計,在一般情況下(即誤碼率為1×10-10),傳輸速度變化?駐x=-1.82 106 MB/s×10-10,為-18.2 KB/s,傳輸帶寬仍接近120.5 MB/s。

3.2實際傳輸測試

測試兩個節點間點對點傳輸,需要兩個數據節點。節點A產生測試數據,節點B接收、校驗測試數據,并通過PCIE以DMA方式發送到PC端。通過PC端軟件檢查并統計100 s傳輸數據,接收11 742 592幀,共計12.024 GB數據。測試結果:數據傳輸速度為120.2 MB/s;帶寬利用效率為96.2%,與仿真結果(96.4%)基本持平。

3.3 結論

根據測試結果,該硬件協議可以有效地進行可靠數據傳輸。在實際測試情況和可以預計的誤碼率情況下,順序傳輸大塊數據的傳輸速度可達到千兆以太網極限帶寬125 MB/s的96%,即120 MB/s。這個數據與TCP協議在MTU 9 000超長幀設定下的PowerPC405系統上的表現基本持平(平均考慮收和發),而遠高于MTU 1 500設定下的表現。TCP協議在低處理頻度下可換來更高的速度,這說明軟件協議的傳輸速度受CPU運算影響大,易產生波動。穩定的高數據率則是硬件協議的優點所在。

? ? ? ? 數據的可靠傳輸是一個具有普遍意義的話題。本文所闡述的在現有成熟以太網技術基礎上,利用FPGA硬件實現數據的高速、可靠的傳輸。相較于復雜的TCP軟件協議,使用硬件協議能夠有效降低CPU負荷,并因此得到穩定的高速數據傳輸速率。本文所述的硬件平臺支持多個以太網端口的擴展。節點內端口之間的可配置轉發功能在板載MCU的控制下可實現靈活路由。這樣多個節點可以組成數據傳輸網絡,因而為諸如高速數據采集網絡、局域網傳輸等網絡應用提供了可行方案。

電子發燒友App

電子發燒友App

評論