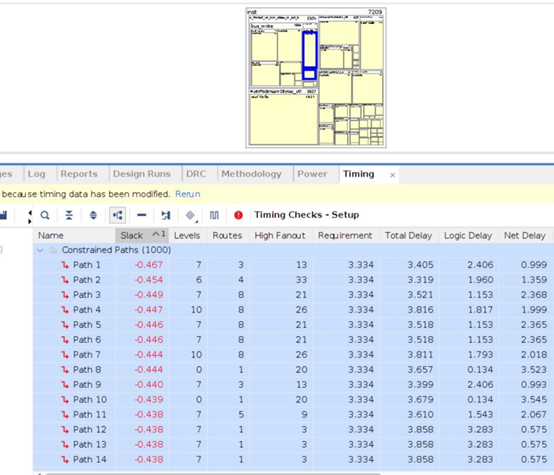

《UltraFast 設計方法時序收斂快捷參考指南》提供了以下分步驟流程, 用于根據《UltraFast設計方法指南》( UG949 )中的建議快速完成時序收斂: 1初始設計檢查:在實現設計前審核

2021-11-05 15:10:26 4603

4603

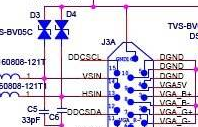

在高速系統中FPGA時序約束不止包括內部時鐘約束,還應包括完整的IO時序約束和時序例外約束才能實現PCB板級的時序收斂。因此,FPGA時序約束中IO口時序約束也是一個重點。只有約束正確才能在高速情況下保證FPGA和外部器件通信正確。

2022-09-27 09:56:09 1382

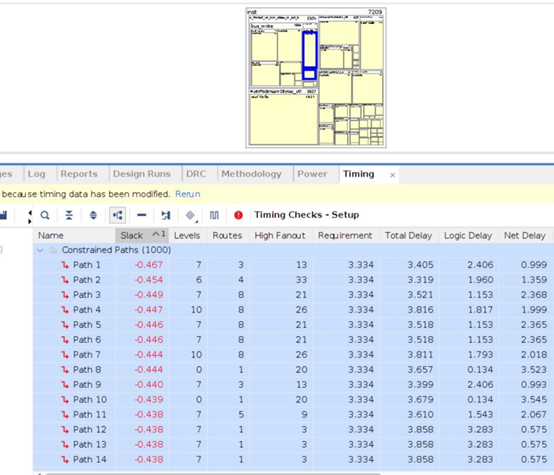

1382 在之前的文章里面介紹了Canny算法的原理和基于Python的參考模型,之后呢在FPGA上完成了Canny算法的實現,可是遇到了時序不收斂的問題,記錄一下。

2023-11-18 16:38:28 450

450

知道“時間分析器”和“planahead”可以幫助我,但我無法理解它的報告。我該怎么做才能解決時間問題。我找不到一些材料來幫助我理解“時序分析”,“代碼風格”,“如何糾正時間問題” ','時序收斂'等等

2019-03-18 13:37:27

經過兩天的惡補,特別是學習了《第五章_FPGA時 序收斂》及其相關的視頻后,我基本上明白了時序分析的概念和用法。之后的幾天,我會根據一些官方的文件對時序分析進行更系統、深入的學習。先總結一下之前

2011-09-23 10:26:01

的時序約束。FPGA作為PCB上的一個器件,是整個PCB系統時序收斂的一部分。FPGA作為PCB設計的一部分,是需要PCB設計工程師像對待所有COTS器件一樣,閱讀并分析其I/O Timing

2016-06-02 15:54:04

(InputDelay、OutputDelay)、上下拉電阻、驅動電流強度等。加入I/O約束后的時序約束,才是完整的時序約束。FPGA作為PCB上的一個器件,是整個PCB系統時序收斂的一部分。FPGA作為

2017-12-27 09:15:17

FPGA畢竟不是ASIC,對時序收斂的要求更加嚴格,本文主要介紹本人在工程中學習到的各種時序約束技巧。 首先強烈推薦閱讀官方文檔UG903和UG949,這是最重要的參考資料,沒有之一。它提倡

2020-12-23 17:42:10

每日開講---學習STM32不得不看的剖析(詳細分析stm32f10x.h)摘要: 學習STM32不得不看的剖析(詳細分析stm32f10x.h)。/**這里是STM32比較重要的頭文件***************************************************************************

2021-08-05 07:44:05

本文跟大家一起詳細分析一下USB協議。

2021-05-24 06:16:36

上一篇文章中,我們詳細分析了VTIM和VMIN的功能,《嵌入式Linux 串口編程系列2--termios的VMIN和VTIME深入理解》 也明白了這兩個參數設計的初衷和使用方法,接下來我們 就詳細

2021-11-05 07:09:55

在嵌入式Linux專題(一)中已經對嵌入式Linux系統的架構及啟動流程有了初步的介紹,本文將詳細分析嵌入式Linux系統啟動流程。

2021-11-05 09:25:29

DVI接口詳細分析DVI 接口規格和定義 DVI 有DVI 1.0 和DVI 2.0 兩種標準,其中 DVI 1.0 僅用了其中的一組信號傳輸信道(data0-data2 ),傳輸圖像的最高像素時鐘

2012-08-11 09:51:00

[url=]uboot代碼詳細分析[/url]

2016-01-29 13:51:41

《FPGA設計時序收斂》,很好的PPT!推薦給大家[hide][/hide]

2011-07-26 11:24:49

個器件,是整個PCB系統時序收斂的一部分。FPGA作為PCB設計的一部分,是需要PCB設計工程師像對待所有COTS器件一樣,閱讀并分析其I/O Timing Diagram的。FPGA不同于COTS

2017-10-20 13:26:35

三極管特性曲線詳細分析,特性曲線看不懂,

2015-06-29 16:34:40

。掌握分析和確定關鍵路徑時序的方法,并通過分析找出關鍵路徑的時序問題,再對關鍵路徑進行優化,通過RTL層面的不斷優化,不斷修煉自己的設計能力,讓設計出來的電路更為靠譜有效!本資料屬大西瓜FPGA開發團隊,在此開源,與大家一起學習FPGA!

2017-02-26 09:42:48

有誰來解答一下如何去消除綜合與時序導致的差異嗎?

2021-04-30 06:20:15

如何使用基于圖形的物理綜合加快FPGA設計時序收斂?

2021-05-06 09:19:08

工程師應該掌握的20個模擬電路(詳細分析及參考答案)

2013-08-17 09:58:13

工程師應該掌握的20個模擬電路(詳細分析及參考答案).pdf

2013-04-07 13:28:38

什么是時序收斂?如何去解決物理設計中時序收斂的問題?

2021-04-26 06:38:50

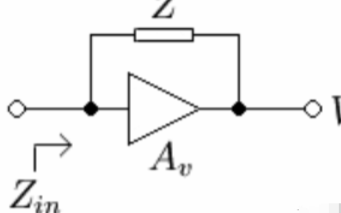

詳細分析一下電路原理,尤其是運算放大器和各種三極管的開關作用,電路走向,感激不盡

2017-10-18 16:53:13

求大神詳細分析電路圖個元器件作用

2013-08-04 15:46:35

求大神詳細分析一下,非專業人士,我不懂

2017-01-13 23:43:32

內含參考答案以及詳細分析

2023-10-07 07:15:56

本文檔的主要內容詳細介紹的是硬件工程師必須掌握的20個重要模擬電路的概述和參考答案以及詳細分析

2023-09-27 08:22:32

電子工程師需要掌握的20個模擬電路的詳細分析

2023-09-28 06:22:26

急 幫幫忙 詳細分析

2017-08-27 17:03:30

本帖最后由 eehome 于 2013-1-5 09:52 編輯

電源電路圖最最最最最詳細分析(轉一網友)

2012-07-31 11:37:21

請問各位大神誰有hifi功放電路圖詳解的資料,電路分析的越詳細越好,最好是每一個元件做什么用都能講到.元件用得越復雜越好.謝謝各位大神了.1.前置放大器電路圖,2.功率放大器電路3.HiFi功放電路4.AB類功放

2019-09-27 08:38:09

給大家詳細分析一下艾德克斯車載充電機的測試方案

2021-05-08 08:38:05

參考ug612。4.輸出時序約束輸出就是輸入的逆,因此分析的過程是類似的,分類也是類似的。針對時鐘的不同,有系統同步和源同步兩種。此處不再詳細說明。系統同步SDR源同步DDR(一般來說不給約束就可以)5.

2019-07-09 09:14:48

請問一下怎樣對stm32的啟動代碼進行詳細分析呢?

2021-11-26 07:10:48

延時開關電路圖及詳細分析

2019-10-14 09:10:33

`哪個高手能給我詳細分析已下逆變器內部構造,主要元器件名稱及作用。謝謝!`

2018-12-29 13:23:01

為什么采用高距離分辨力單脈沖技術為可以消除距離閃爍?求業內高手詳細分析

2015-06-28 21:30:21

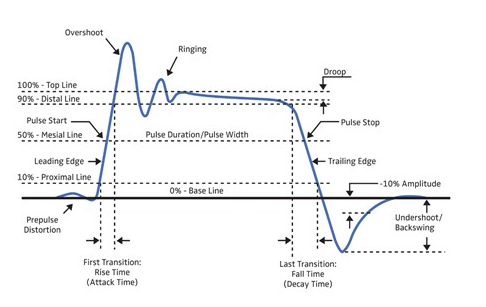

在PCB走線的延時,因此上圖只是一個理想過程,即沒有考慮PCB走線的延時,而我們的時序分析工具確實將其考慮在內了,所以,我們的FPGA建立時間,除了包括數據保持穩定的時間外,還應加上這段走線延時的時間

2015-03-31 10:35:18

給我們的FPGA做內部時鐘,在輸出到外部做SDRAM的工作時鐘,所以上圖中,晶振到外部器件的時鐘路徑,應該是PLL的輸出到SDRAM的輸出路徑還有,我們之前做的靜態時序分析,是基于在FPGA內部的,所以數據

2015-03-31 10:20:00

本文詳細分析了ADSL系統中ATM層和物理層之間的UTOPIA LEVEL2接口時序,采用FPGA實現了UTOPIA接口設計,應用在ADSL系統中,數據收發正確,工作穩定;該方案的實現對解決現有專門通信芯

2010-07-28 16:54:10 19

19 延長指紋鎖使用壽命的詳細分析

進入21世紀,中國的生物識別技術燃起烽火,使指紋鎖行業得到了迅速發展。但是某些

2007-10-16 16:15:49 1605

1605 延時開關電路圖及詳細分析

圖1:

2007-11-08 10:20:09 13453

13453 超級電容器原理及電特性詳細分析

超級電容器是一種高能量密度的無源儲能元件,隨著它的問世,如何應用好超級電容器,提高電子線路的性能和研發新的電路、

2009-12-08 08:40:43 4320

4320 筆記本使用十大陋習詳細分析

電腦越來越平民化,可是電腦卻總是出問題 由于摩爾法則的影響,整個IT產品業界的產品售價正在

2010-01-20 14:18:53 316

316 焊接技術詳細分析

焊接實質上是將元器件高質量連接起來最容易實現的方法,對于DIY高手來說,光能掌握電腦配件的性能和參數

2010-01-26 10:46:22 1630

1630 大屏幕顯示技術的發展趨詳細分析介紹

引言 隨著網絡技術、計算機信息技術、自控技術在煤炭生產企業的迅速普及,礦井的自

2010-02-21 16:56:17 615

615 電子整流器工作原理詳細分析

2010-02-27 10:43:51 24851

24851 施密特觸發器原理圖解詳細分析

重要特性:施密特觸發器具有如下特性:輸入電壓有兩個閥值VL、VH,VL施密特觸發器通常

2010-03-08 14:23:43 68176

68176 主板設計的5大缺陷詳細分析

第1頁:顯卡聲卡不兼容一覽

“太慘了!剛買的散熱器竟然用不上!”“好郁悶,PCI擴展槽竟然裝不上聲卡。”

有的時候,我們經

2010-03-15 10:52:21 1509

1509 介紹了采用STA (靜態時序分析)對FPGA (現場可編程門陣列)設計進行時序驗證的基本原理,并介紹了幾種與STA相關聯的時序約束。針對時序不滿足的情況,提出了幾種常用的促進 時序收斂的方

2011-05-27 08:58:50 70

70 摘 要: 時序相似搜索被認認最有前途的技術之一然而時序數據是典型的高維海量數據,本內容提供了高效時序相似搜索技術的詳細分析

2011-07-27 15:52:49 23

23 uboot 1-1-6版本的 代碼詳細分析

2015-11-02 11:02:19 25

25 FPGA時序約束方法很好地資料,兩大主流的時序約束都講了!

2015-12-14 14:21:25 19

19 十二五規劃教材大學電路(邱關源、羅先覺版)二端口網絡的詳細分析和經典例題以及解題方法

2015-12-23 18:15:36 0

0 電子工程師必須掌握的20個模擬電路詳細分析

2016-06-08 17:52:35 34

34 近期的幾個單片機例程及詳細分析,感興趣的可以看看。

2016-06-21 17:02:48 3

3 fpga時序收斂

2017-03-01 13:13:34 23

23 采用MATLAB對SPWM進行輔助設計與詳細分析和解決方法

2017-09-14 14:22:28 18

18 半橋電源源高頻鏈逆變電路的詳細分析

2017-09-14 15:23:44 19

19 DC-DC變換器突加負載時的動態性能研究詳細分析與實驗驗證

2017-09-15 08:45:09 21

21 Buck變換器原理詳細分析

2017-09-15 17:26:25 30

30 介紹了一種在多工藝角多工作模式下快速實現時序收斂的技術MCMM(Multicorner-Multimode)技術,該技術將工藝角和模式進行組合,對時序同時進行分析和優化,到達快速實現時序收斂的目的

2017-10-20 15:21:11 3

3 一個好的FPGA設計一定是包含兩個層面:良好的代碼風格和合理的約束。時序約束作為FPGA設計中不可或缺的一部分,已發揮著越來越重要的作用。毋庸置疑,時序約束的最終目的是實現時序收斂。時序收斂作為

2017-11-17 07:54:36 2326

2326

問題的惱人之處在于沒有哪種方法能夠解決所有類型的問題。由于客戶對于和現場應用工程師共享源代碼通常非常敏感,因此我們通常都是通過將工具的潛力發揮到極致來幫助客戶解決其時序問題。

2017-11-24 19:49:44 9123

9123

濾波電容器、共模電感、磁珠在EMC設計電路中是常見的身影,也是消滅電磁干擾的三大利器。對于這這三者在電路中的作用,相信還有很多工程師搞不清楚。本文從設計設計中,詳細分析了消滅EMC三大利器的原理。

2017-12-01 10:12:13 11403

11403

OpenWrt是一個開放的linux平臺,主要用于帶wifi的無線路由上。類似于Ubuntu、Red Hat、之類的linux發行版本,它也有一套自己的啟動流程。本文主要介紹了openwrt啟動過程及詳細分析。

2017-12-27 09:17:39 12398

12398

降低通信應用開發風險”將詳細分析高速通信和數據中心的時序要求,并介紹Silicon Labs經市場驗證的時鐘振蕩器解決方案,幫助工程人員克服日益艱鉅的高速網絡定時設計挑戰。

2018-01-26 16:20:52 7551

7551 FPGA時序收斂讓你的產品達到最佳性能!

2018-04-10 11:38:48 18

18 物聯網的產業生態是怎樣的詳細分析概述

2018-12-08 10:00:07 4642

4642 本文檔的主要內容詳細介紹的是繪制原理圖的基本規測和各種電氣控制原理圖詳細分析。

2019-08-25 11:36:36 5477

5477 本文檔的主要內容詳細介紹的是硬件工程師必須掌握的20個重要模擬電路的概述和參考答案以及詳細分析

2019-11-13 16:24:26 133

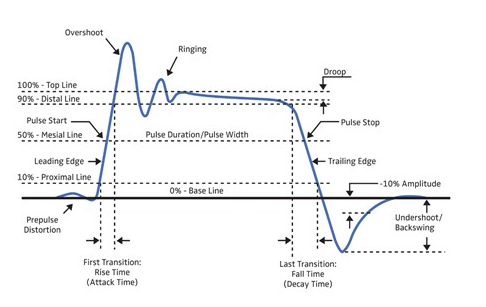

133 Boonton的功率表非常詳細的波形跟蹤可實現精確的測量,有效的校準,以及對線性和脈沖射頻部件及系統的詳細分析。

2020-01-10 09:56:00 847

847

本文檔的主要內容詳細介紹的是電子電路的復習題詳細分析

2020-04-15 08:00:00 15

15 本文檔的主要內容詳細介紹的是一些開關電源的拓撲結構詳細分析。

2021-01-06 00:16:00 20

20 電子發燒友網站提供《華為Mate40Pro的拆解報告詳細分析.pdf》資料免費下載

2020-11-26 07:01:00 89

89 本文檔的主要內容詳細介紹的是華為FPGA硬件的靜態時序分析與邏輯設計包括了:靜態時序分析一概念與流程,靜態時序分析一時序路徑,靜態時序分析一分析工具

2020-12-21 17:10:54 18

18 在高速系統中FPGA時序約束不止包括內部時鐘約束,還應包括完整的IO時序約束利序例外約束才能實現PCB板級的時序收斂。因此,FPGA時序約束中IO口時序約束也是重點。只有約東正確才能在高速情況下保證FPGA和外部器件通信正確

2021-01-13 17:13:00 11

11 本文檔的主要內容詳細介紹的是FPGA的時序分析的優化策略詳細說明。

2021-01-14 16:03:59 17

17 本文檔的主要內容詳細介紹的是FPGA的時序分析的優化策略詳細說明。

2021-01-14 16:03:59 19

19 本文檔的主要內容詳細介紹的是如何實現LTE無線網絡優化案例的詳細分析。

2021-01-14 16:55:41 21

21 本文檔的主要內容詳細介紹的是功率放大電路的仿真資料詳細分析。

2021-02-01 11:28:50 28

28 電子發燒友網為你提供隔離設計中的共模 (CM) 噪聲詳細分析資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-03-31 08:41:49 9

9 ,能夠有效減少時序路徑問題分析所需工作量。 時序路徑問題分析定義為通過調查一條或多條具有負裕量的時序路徑來判斷達成時序收斂的方法。當設計無法達成時序收斂時,作為分析步驟的第一步,不應對個別時序路徑進行詳細時序分

2021-05-19 11:25:47 2677

2677

正激有源鉗位的詳細分析介紹。

2021-06-16 16:57:07 56

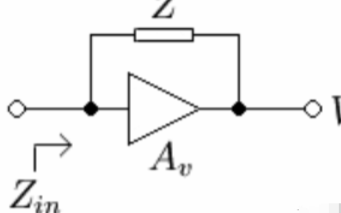

56 本文介紹了米勒效應的由來,并詳細分析了MOSFET開關過程米勒效應的影響,幫助定性理解米勒平臺的形成機制。最后給出了場效應管柵極電荷的作用。

2022-03-10 14:44:18 6226

6226

本文旨在提供一種方法,以幫助設計師判斷給定模塊是否能夠在空裸片上達成時序收斂。 如果目標模塊無法在空裸片上達成非關聯 (OOC) 時序收斂,則恐難以與設計其余部分達成關聯性時序收斂。設計師可從完整

2022-08-02 11:37:35 318

318

在 FPGA 設計進程中,時序收斂無疑是一項艱巨的任務。低估這項任務的復雜性常常導致工作規劃面臨無休止的壓力。賽靈思提供了諸多工具,用于幫助縮短時序收斂所需時間,從而加速產品上市。本篇博文描述了一種方法,能夠有效減少時序路徑問題分析所需工作量

2022-08-02 09:25:06 425

425

FPGA時序不收斂,會出現很多隨機性問題,上板測試大概率各種跑飛,而且不好調試定位原因,所以在上板測試前,先優化時序,再上板。

2023-06-26 15:41:31 1112

1112

電子發燒友網站提供《UltraFast設計方法時序收斂快捷參考指南(UG1292).pdf》資料免費下載

2023-09-15 10:38:51 0

0

電子發燒友App

電子發燒友App

評論