本帖最后由 lee_st 于 2017-10-31 08:46 編輯

Verilog HDL代碼書寫規范

2017-10-21 20:53:14

1. 目的本規范的目的是提高書寫代碼的可讀性、可修改性、可重用性,優化代碼綜合和仿真的結果,指導設計工程師使用VerilogHDL規范代碼和優化電路,規范化可編程技術部的FPGA設計輸入,從而做到

2017-12-08 14:36:30

Verilog HDL代碼書寫規范

2017-09-30 08:55:28

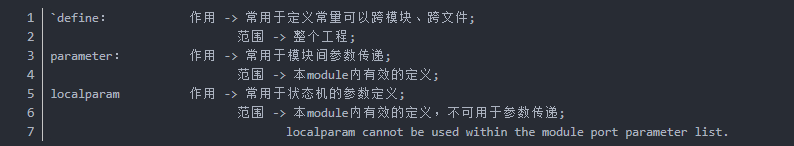

Verilog 預編譯Verilog 語言支持宏定義(`define),參數 parameter,局域參數(localparam)以及`include等內容。這些數據常量的支持極大方便數字系統

2021-08-11 09:31:48

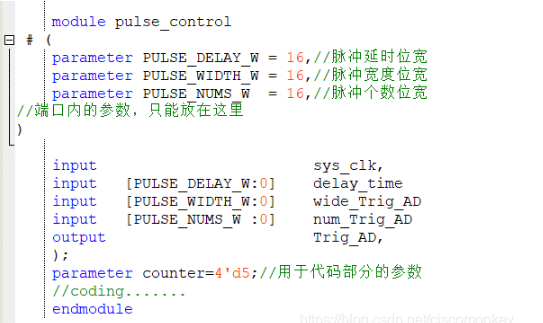

就可以了。3、作用parameter可以用作例化時的參數傳遞。具體方法參見《Verilog例化時的參數傳遞》一文在使用狀態機時候區別挺大的狀態機的定義可以用parameter 定義,但是不

2013-04-25 14:32:24

在Verilog定義函數的時候,有位寬的定義,我想問下諸位大俠,這個定義可以不要嗎?這個位寬是不是該函數處理數據的能力的一種?還是有其他用途。請諸位大神賜教

2013-07-20 10:00:56

本帖最后由 lee_st 于 2017-10-31 08:46 編輯

Verilog語法基礎講解之參數化設計

2017-10-21 20:56:17

1.1 parameter與localparam使用區別1.1.1 本節目錄1)本節目錄;2)本節引言;3)FPGA簡介;4)parameter與localparam使用區別;5)結束語。1.1.2

2021-07-26 07:55:51

PARAMETERS//*****************************parameter//函數名、宏定義、參數定義用大寫//*****************************// DEFINE

2015-03-09 20:22:13

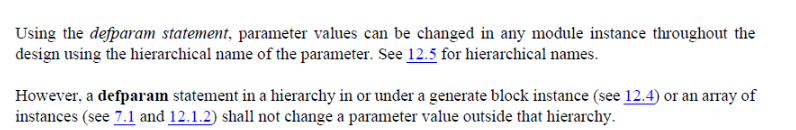

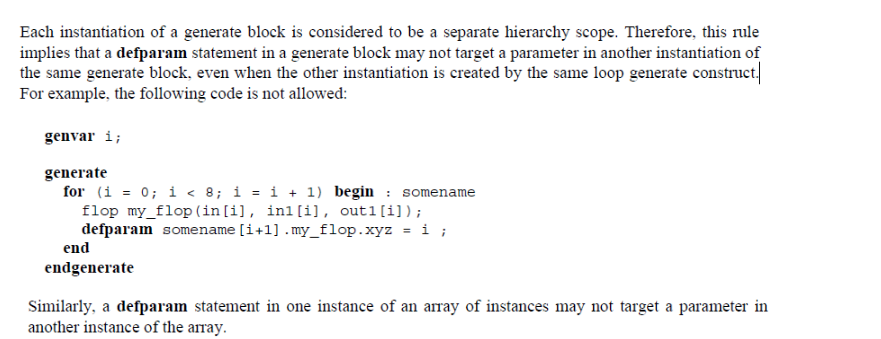

generate為verilog中的生成語句,當對矢量中的多個位進行重復操作時,或者當進行多個模塊的實例引用的重復操作時,或者根據參數的定義來確定程序中是否應該包含某段Verilog代碼的時候

2020-12-23 16:59:15

verilog中初值定義 -----initial是否可以被綜合。

2018-09-14 11:49:40

明德揚設計規范對電路設計做了較高的要求,其目就在于用最簡單的代碼、最簡潔的方式,設計出最易讀、最健壯、最高效的Verilog代碼。按照明德揚設計規范進行代碼設計的具體要求如下。下面是初學者學習時定

2015-05-22 17:01:04

1.1 FPGA雙沿發送之Verilog HDL實現1.1.1 本節目錄1)本節目錄;2)本節引言;3)FPGA簡介;4)FPGA雙沿發送之Verilog HDL實現;5)結束語。1.1.2 本節

2021-07-26 06:20:59

1.1 FPGA雙沿采樣之Verilog HDL實現1.1.1 本節目錄1)本節目錄;2)本節引言;3)FPGA簡介;4)FPGA雙沿采樣之Verilog HDL實現;5)結束語。1.1.2 本節

2021-07-26 07:44:03

`FPGA寶貴實戰經驗及Verilog編程規范`

2013-06-10 12:03:11

此篇將圍繞設計操作規程中的建元件庫、做元件這一步驟展開,在此您不但可以學到PCB元件制作的標準、了解PCB設計的操作規程,讓您的設計工作規范化;同時還可以學會使用PowerPCB軟件做元件的相關操作方法,最終掌握并達到通過PowerPCB來實現設計標準化的目的。點擊下載

2019-04-29 13:49:28

STM32野火平衡小車之如何搭建之PID與MPU6050初始化

2021-10-13 06:04:02

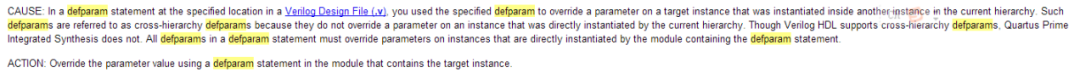

本文討論了一些System Verilog問題以及相關的SystemVerilog 語言參考手冊規范。正確理解這些規格將有助于System Verilog用戶避免意外的模擬結果。

2020-12-11 07:19:58

本文討論了一些System Verilog問題以及相關的SystemVerilog 語言參考手冊規范。正確理解這些規格將有助于System Verilog用戶避免意外的模擬結果。

2020-12-24 07:07:04

PYCPLD的IP 設計規范本文討論建立一種Python的模塊腳本,將verilog語言變成python的程序塊,方便以python的方式來組織IP,方便應用工程師更快的使用IP. 1. 如何將IP

2016-12-12 22:27:39

時鐘頻率是中代碼計時計數器的重要參數,為提高代碼的可讀性及移植性,可通過一個參數定義時鐘頻率參數,請用parameter定義CLK_FRE為50MHz的時鐘頻率參數

2023-08-29 09:30:19

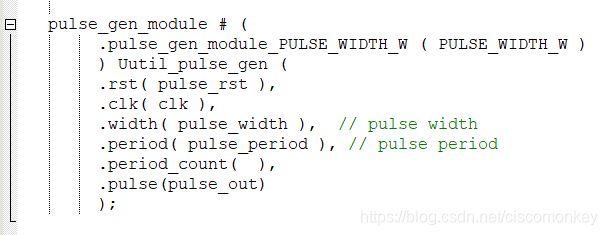

基于上一題目模塊中定義的parameter參數,在例化該模塊時實現參數傳遞

2023-08-30 11:23:51

這幾天一直忙著辦理離職手續,整理以前做的工作,方便交接,小鋼炮的使用就暫時擱淺了。前面看到 小鋼炮的源碼時,覺得分類不規范,看的蛋疼。接合原子的例子,特意重新建了一個工程。下面是分類:典型的原子風格

2016-02-24 15:32:59

);//輸入輸出信號列表//說明reg //寄存器wire//線網parameter//參數input//輸入信號output//輸出信號inout//輸入輸出信號function//函數task//任務

2018-09-18 09:37:40

FPGA verilog代碼書寫規范,很好的借鑒

2015-05-21 11:36:27

,參數定義建議大寫,另外信號命名最好體現信號的含義。規范建議以下是一些書寫規范的要求:1、用有意義的有效的名字如sum、cpu_addr等。2、用下劃線區分詞語組合,如cpu_addr。3、采用一些前綴

2020-09-21 16:48:48

/jishu_524793_1_1.html29【芯航線FPGA學習平臺眾籌進度帖】Verilog語法基礎講解之參數化設計:https://bbs.elecfans.com/jishu_528770_1_1.html30【連載視頻教程

2015-11-26 10:50:51

的定義和使用,參數型常數經常用于定義延遲時間和變量寬度。

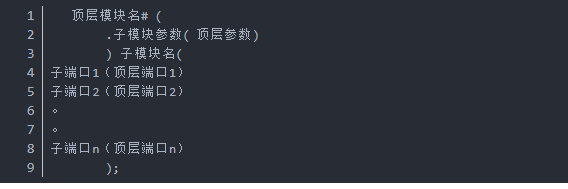

parameter可用作在頂層模塊中例化底層模塊時傳遞參數的接口,localparam的作用域僅僅限于當前module,不能作為參數傳遞的接口

2023-05-17 16:26:53

代碼規范化如何學習,單片機也要求規范化么?

2023-10-12 07:19:17

關于發帖標題規范化管理公告由于論壇管理事物繁重,很多時候由不得我們幾個管理員的眼睛和手指去處理,為了大家的問題能夠更好,更直接的讓各位大大們過目,讓大家的問題都能得到解決,管理員團隊特出發帖標題規范

2014-11-04 17:11:07

] b; //定義一個八位的wire數據reg [7:0] b; //定義一個八位的reg數據其中。[7:0]表示位寬,只要是整數就好,當然分號左邊的數要大于右邊的。4、參數定義:parameter

2016-03-16 10:45:02

`勇敢的芯伴你玩轉Altera FPGA連載34:Verilog代碼書寫規范特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1i5LMUUD 雖然沒有

2017-12-27 09:41:12

求大神給下我單片機C語言模塊化程序,讓我好好學習,規范化我的代碼編寫

2013-07-23 14:57:44

單片機開發之C語言編程基本規范為了提高源程序的質量和可維護性,從而最終提高軟件產品生產力,特編寫此規范。本標準規定了程序設計人員進行程序設計時必須遵循的規范。本規范主要針對單片機編程語言和08編譯器

2017-10-07 11:53:15

本規范主要針對單片機編程語言和08編譯器而言,包括排版、注釋、命名、變量使用、代碼可測性、程序效率、質量保證等內容。 1.基本規則 格式清晰、注釋簡明扼要、命名規范易懂、函數模塊化、程序易讀易維護

2017-08-06 09:46:54

很反感很反感很反感很反感

2016-06-27 14:14:17

方式:some.where.else.theSignal.pull()在生成RTL代碼時,會講該信號聲明一個端口鏈接偷穿到我們這一級的Component。Component參數化設計與我們編寫Verilog時相同,在SpinalHDL里

2022-07-21 14:20:23

有沒有人對如何用參數化加法器樹編寫Verilog有任何建議,輸入參數是操作數的數量?加布里埃爾以上來自于谷歌翻譯以下為原文Does anyone have any suggestions

2019-04-25 13:28:42

本文檔為作者 在嵌入式和嵌入式 linux C語言的學習和工作中所總結的代碼規范 ,是作者從 STM32單片機開發向 Linux C開發的時候為了擺脫遺留的編碼規范陋習而編寫的 。因此,本文檔 主要

2020-01-14 10:25:08

電力企業安全工器具規范化操作指導系統 一、系統概述 對電力生產人員來說,了解各種安全工器具的性能和用途,正確掌握它們

2010-11-18 14:02:42

》踩到的坑在很早之前,曾寫過如何在SpinalHDL中例化之前用Verilog/SystemVerilog所寫的代碼,可參照文章《[SpinalHDL——集成你的RTL代碼]》一文。在

2022-08-31 14:58:31

時對ddr初始化,但是在6678數據手冊Table 2-23 DDR3 Boot Parameter Table 中并未找到與之相關的配置參數。謝謝

2018-08-06 08:34:24

貼片知識課堂九,PCB設計規范化第一節PCB設計和生產的關系到底有多大?這一直是許多工程師懷疑,甚至想弄明白的問題!今天麥斯艾姆(massembly)貼片知識課堂,為廣大工程師朋友直觀地講解一些

2012-09-14 09:24:42

本帖最后由 eehome 于 2013-1-5 10:04 編輯

麥斯艾姆(massembly)貼片知識課堂十一,PCB設計規范化第三節麥斯艾姆(massembly)貼片知識課堂繼續上次的話

2012-10-31 14:16:16

麥斯艾姆(massembly)貼片知識課堂十,PCB設計規范化第二節麥斯艾姆(massembly)貼片知識課堂繼續上次的話題“PCB設計規范化”。1, 散熱焊盤,對于某些功率器件,包括功放,電源

2012-10-31 14:12:59

麥斯艾姆(massembly)貼片知識課堂十,PCB設計規范化第二節麥斯艾姆(massembly)貼片知識課堂繼續上次的話題“PCB設計規范化”。1, 散熱焊盤,對于某些功率器件,包括功放,電源

2012-09-18 09:43:27

s-parameter calculator:S參數計算工具.input S11,S22,S12,S21等參數,就可以進行參數計算。

2008-10-23 15:24:23 31

31 Verilog代碼書寫規范

本規范的目的是提高書寫代碼的可讀性、可修改性、可重用性,優化代碼綜合和仿真的結果,指導設計工程師使用

2010-04-15 09:47:00 106

106 云計算作為物聯網快速增長的重要部分,市場規模年均復合增長達到91.5%。為更好地完善和建立云計算服務市場準入制度,加快云計算服務質量、資源整合,云計算產業發展擬定五項規范化要求。

2013-06-13 17:00:27 561

561 verilog代碼規范,學會寫代碼還不行,我們需要更加的規范。

2016-03-25 14:43:38 24

24 verilog代碼規范,學會寫代碼還不行,我們需要更加的規范。

2016-03-25 14:42:02 145

145 verilog代碼規范,學會寫代碼還不行,我們需要更加的規范。

2016-03-25 14:36:05 34

34 verilog代碼規范,學會寫代碼還不行,我們需要更加的規范。

2016-03-25 14:28:34 35

35 verilog代碼規范,學會寫代碼還不行,我們需要更加的規范。

2016-03-25 14:26:26 24

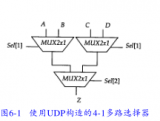

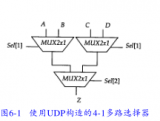

24 本章講述Verilog HDL指定用戶定義原語UDP的能力。UDP的實例語句與基本門的實例語句完全相同,即U D P實例語句的語法與基本門的實例語句語法一致。verilog相關教程材料,有興趣的同學可以下載學習。

2016-04-25 16:09:32 12

12 在C語言中我們不遵循編譯器就會報錯的規定叫規則;約定成俗但不遵守也不會出錯的規定叫規范。比如變量必須先定義后使用,如果我們不定義就直接使用就會出錯。

2016-07-26 15:44:42 5

5 cordic算法verilog實現(簡單版)(轉載)module cordic(clk, phi, cos, sin); parameter W = 13, W_Z = 14; input clk; input [W_Z-1:0] phi; output[W-1:0]

2017-02-11 03:06:11 3044

3044

華為的verilog編碼規范

2017-11-01 08:41:26 40

40 推特文本中包含著大量的非標準詞,這些非標準詞是由人們有意或無意而創造的。對很多自然語言處理的任務而言,預先對推特文本進行規范化處理是很有必要的。針對已有的規范化系統性能較差的問題,提出一種創新

2017-12-15 14:12:59 0

0 在該工程中,國網河北省電力公司嚴格落實規范化開工要求,占地協調、林木清理、三線遷改等工程通道補償協議簽訂及合規性手續辦理已全面滿足連續施工條件。 3月22日,北京西—石家莊1000千伏交流 特高壓

2018-04-07 19:35:00 3918

3918 對關系的規范化是改造關系模式過程,首先,根據一組不同級別的范式判定關系的規范化程度,確定不正常的數據依賴關系,通過模式分解將一個低一級范式的關系模式,轉換為若干個高一級的范式的關系模式的集合,消除其中不合適的數據依賴,以解決插入異常、刪除異常、更新異常和數據冗余問題。

2018-09-05 14:26:00 5

5 設計規范化與自由創作之間沒有任何矛盾。它只是制約了那些可能出錯或者低效的行為,令設計思路更加明朗、設計效率得到提高、設計質量充分保證。

2018-10-09 11:10:23 2987

2987 很多人認為,IC/FPGA屬于設計范疇。設計是一個需要設計師自由創作的過程,怎么可能被一些條條框框所局限呢?其實,設計規范化與自由創作之間沒有任何矛盾。

2018-10-11 09:59:31 3140

3140 ,如receive_clk_b; ③ 由parameter定義的常量要求全部字母大寫,自己定義的參數、類型用大寫標識,推薦使用parameter來定義有實際意義的常數,包括單位延時、版本號、板類型、單板在位信息、LED

2020-11-24 12:12:08 2989

2989 ADPA1105 S-Parameter

2021-01-27 19:48:15 0

0 AD9650 S-Parameter

2021-01-28 09:56:09 1

1 ADRF5046 - S-Parameter

2021-01-28 14:33:26 1

1 ADRF504 7 - S-Parameter

2021-01-28 14:35:27 0

0 ADL6012 S-Parameter

2021-01-30 09:17:06 0

0 LTC5597 S-Parameter

2021-01-30 09:36:07 0

0 ADRF5043 S-Parameter

2021-01-30 09:38:07 0

0 ADRF5042 s-parameter

2021-01-30 09:40:07 0

0 HMC798A S-parameter

2021-01-30 12:23:18 0

0 HMC966 S-Parameter

2021-02-01 11:31:16 0

0 ADPA7005 S-Parameter

2021-02-02 10:14:13 1

1 ADPA7005 S-Parameter

2021-03-05 10:47:16 0

0 用戶定義的原語 在前一章中,我們介紹了Verilog HDL提供的內置基本門。本章講述Verilog HDL指定用戶定義原語U D P的能力。 U D P的實例語句與基本門的實例語句完全相同

2021-03-05 15:30:36 1426

1426

ADL5725 S-Parameter

2021-03-11 13:11:30 0

0 ADRF6780 S-Parameter

2021-03-11 13:55:32 0

0 時的檢測效果不理想。因此,提出一種基于規范化函欻的深度金字塔模型(Norm-DP)算法,使用規范化函數融合可變形部件模型和卷積神經網絡模型,直接從金字塔特征中提取正負樣本,使用隱變量攴持向量杋進行模型訓練,結合柔性非

2021-03-30 14:09:02 14

14 作者 | 濤姐濤哥 鏈接 | cnblogs.com/taojietaoge/p/11575376.html 如何更規范化編寫Java 代碼 Many of the happiest people

2021-08-27 09:31:30 3415

3415 鋼網開孔設計規范定義

2021-10-18 11:27:31 9

9 parameter關鍵字定義模塊特定的參數,該參數在特定模塊實例的范圍生效。參數用于為模塊實例提供不同的自定義,例如,輸入或輸出端口的寬度。以下是使用parameter關鍵字的示例:

2022-06-26 10:46:20 1037

1037 在前一章中,我們介紹了Verilog HDL提供的內置基本門。本章講述Verilog HDL指定用戶定義原語U D P的能力。

2022-08-08 11:46:46 733

733 在實際工作中,許多公司對Verilog程序編寫規范都有要求。在公司內部統一Verilog程序編寫規范不僅可以增強程序的可讀性、可移植性,而且也有助于邏輯工程師之間交流、溝通,提升邏輯組成員之間的團隊協作能力。本文就大部分公司常見的Verilog程序編寫規范作一個介紹。

2022-09-15 09:35:58 3412

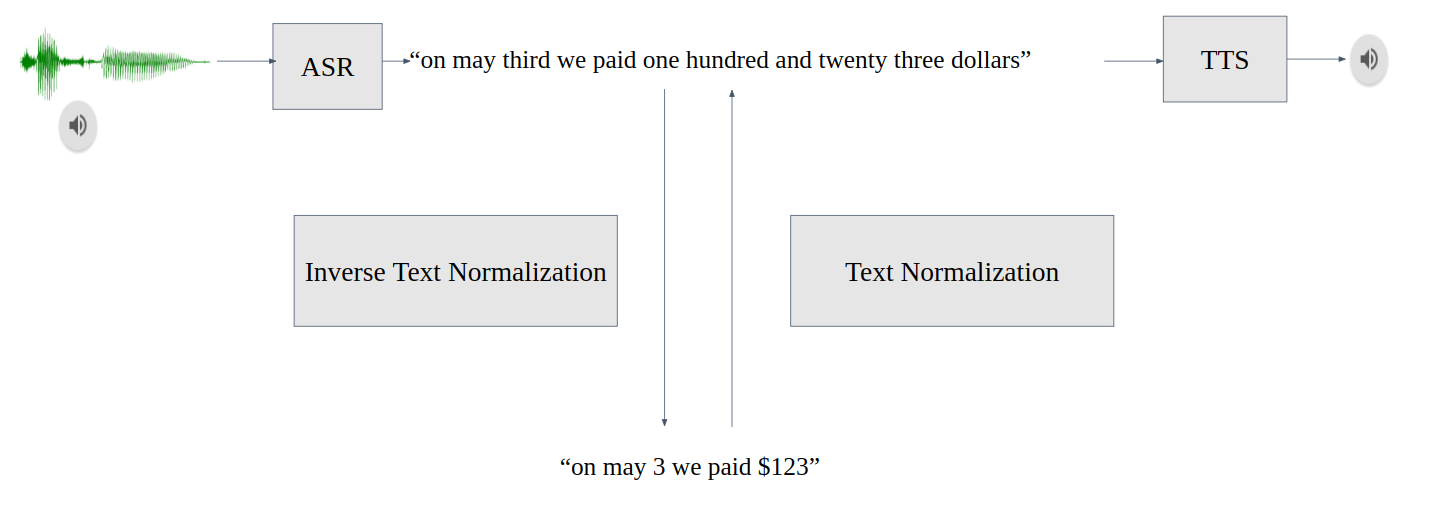

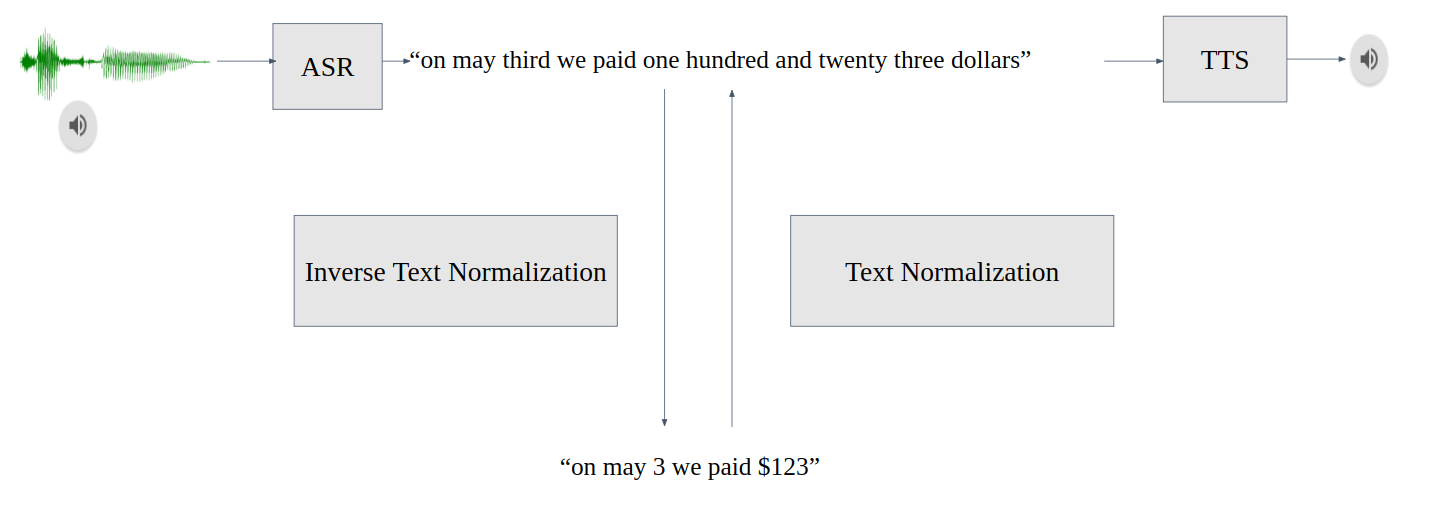

3412 文本規范化( TN )將文本從書面形式轉換為口頭形式,是文本到語音( TTS )之前的一個重要預處理步驟。 TN 確保 TTS 可以處理所有輸入文本,而不會跳過未知符號。例如,“ 123 美元”轉換為“一百二十三美元”

2022-10-11 11:41:12 1411

1411

本規范的目的是提高書寫代碼的可讀性 可修改性 可重用性 優化代碼綜合和仿真的結 果 指導設計工程師使用VerilogHDL規范代碼和優化電路 規范化公司的ASIC設計輸入從而做到。

2022-11-23 17:28:18 791

791 在testbench中避免使用絕對的時間,如#20,#15或#(CYC+15)等,應該在文件前面使用parameter定義一些常量,使得時間的定義象#(CYC+OFF0)的形式,便于修改。

2022-11-25 09:26:41 788

788 FPGA 設計的硬件語言Verilog中的參數化有兩種關鍵詞:define 和 paramerter,參數化的主要目的是代碼易維護、易移植和可讀性好。

2022-12-26 09:53:10 676

676 我們將介紹如何使用verilog參數和generate語句來編寫可重用的verilog 代碼。

與大多數編程語言一樣,我們應該嘗試使盡可能多的代碼可重用。這使我們能夠減少未來項目的開發時間

2023-05-11 15:59:21 647

647 注:以R起頭的是對編寫Verilog代碼的IP設計者所做的強制性規定,以G起頭的條款是建議采用的規范。每個設計者遵守本規范可鍛煉命名規范性。

2023-08-15 16:23:41 1089

1089 Verilog規范對于一個好的IC設計至關重要。

2023-08-17 10:14:07 580

580

c語言帶參數的宏定義? C語言宏定義是一種宏替換機制,它可以將一個標識符替換為一個代碼片段。宏定義通常在程序中用來方便地進行常量定義或函數模板定義。在C語言中,宏定義有以下幾種類型: 1. 簡單

2023-09-04 17:45:18 1515

1515

電子發燒友App

電子發燒友App

評論