鎖相環(PLL)電路存在于各種高頻應用中,從簡單的時鐘凈化電路到用于高性能無線電通信鏈路的本振(LO),以及矢量網絡分析儀(VNA)中的超快開關頻率合成器。

2018-08-15 14:13:11 75978

75978

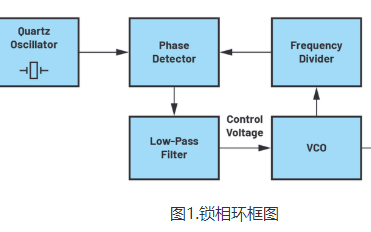

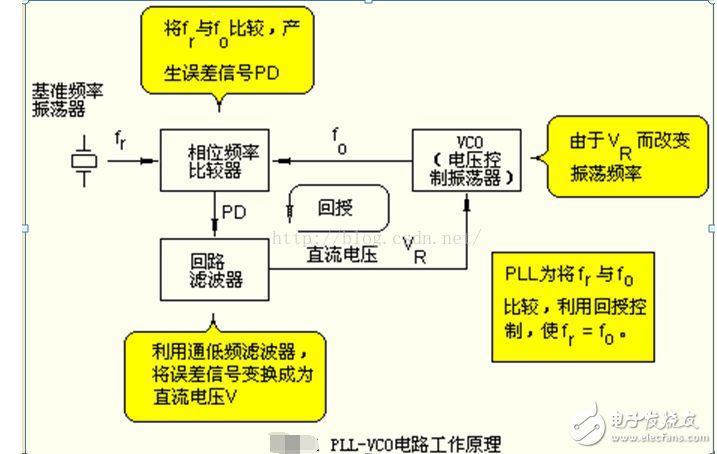

鎖相環英文名稱PLL(Phase Locked Loop),中文名稱相位鎖栓回路,現在簡單介紹一下鎖相環的工作原理。

2023-04-28 09:57:31 4380

4380

PLL(鎖相環)電路原理是什么?

2022-01-21 07:03:37

RCU學習筆記Chapter 1 時鐘1.1 名詞解釋PLL:PLL(Phase Locked Loop): 為鎖相回路或鎖相環,用來統一整合時鐘信號,使高頻器件正常工作,如內存的存取資料等。PLL

2022-01-26 07:17:01

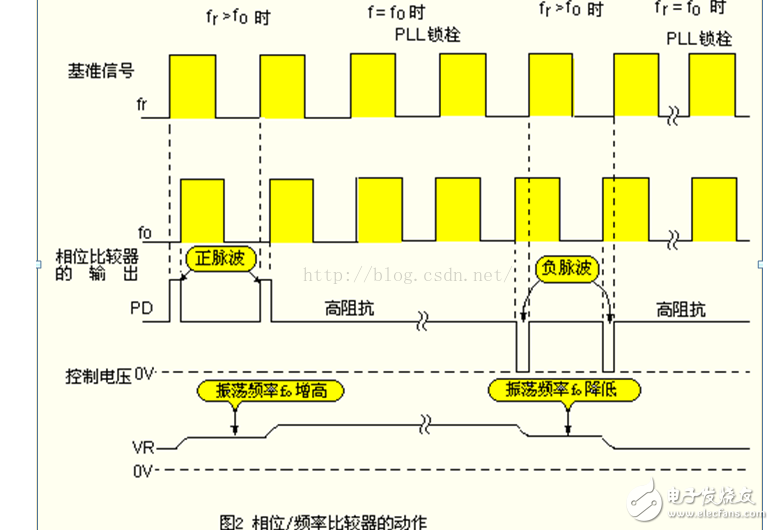

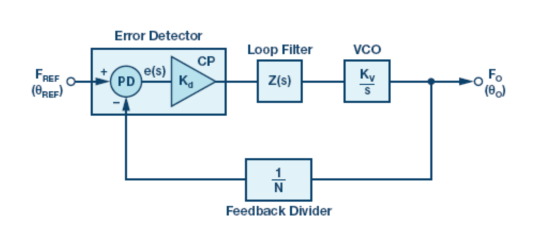

壓控振蕩器的輸入控制電壓Uc(t)。(3)VCO:壓控振蕩器,它是電壓-頻率轉換器,其振蕩頻率由Uc(t)決定。2. PLL電路的特征在一定的頻率輸入范圍內,鎖相環可以鎖定帶有固定頻率的輸入時鐘。VCO的振蕩

2020-11-17 09:52:01

設計并調試鎖相環(PLL)電路可能會很復雜,除非工程師深入了解PLL理論以及邏輯開發過程。本文介紹PLL設計的簡易方法,并提供有效、符合邏輯的方法調試PLL問題。

2019-07-08 08:02:17

筆記本主板各部分關鍵測試電壓筆記本的主板(又稱“基板”)無論在功能上或是在組成結構上,與臺式機有著相當程度的不同。我們可以在網絡上下載到使用Inter南北橋芯片的主板原理圖。我大概的瀏覽了一下,那些

2011-02-22 23:44:55

設計并調試鎖相環(PLL)電路可能會很復雜,除非工程師深入了解PLL 理論以及邏輯開發過程。本文介紹PLL設計的簡易 方法,并提供有效、符合邏輯的方法調試PLL 問題。 仿真如果不在特定條件下進行

2018-10-22 09:45:08

圖解實用電子技術叢書,介紹鎖相環(PLL)電路設計與應用,供大家參考

2016-06-21 22:51:39

概述:TLC2932是德州儀器公司出品的一款鎖相環電路(PLL)芯片,它由壓控振蕩器和以沿觸發方式工作的鑒相器(PFD:phflse frequency deteclor)組成。

2021-04-08 07:48:53

硬件鎖相環和軟件鎖相環,這個很好理解,很多東西原來都是直接用硬件電路搞出來,現在有可編程器件了,再利用軟件來實現。傳統的硬件鎖相環在如諧波、頻率突變、相位突變等電壓畸變以及三相電壓不平衡情況下,很難

2015-01-04 22:57:15

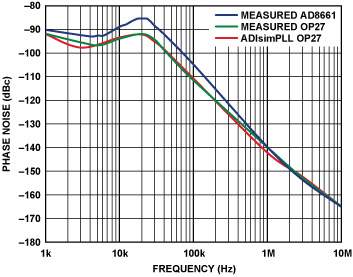

ADI是高性能模擬器件供應商,在鎖相環領域已有十多的的設計經驗。到目前為止,ADI的ADF系列鎖相環產品所能綜合的頻率可達8GHz,幾乎能夠涵蓋目前所有無線通信系統的頻段。ADF系列PLL頻率合成器

2018-10-31 15:08:45

本帖最后由 gk320830 于 2015-3-7 20:18 編輯

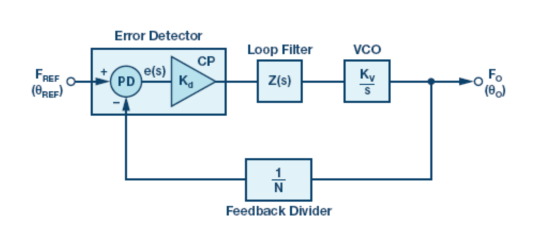

鎖相環的原理,特性與分析所謂鎖相環路,實際是指自動相位控制電路(APC),它是利用兩個電信號的相位誤差,通過環路自身調整作用,實現頻率準確跟蹤的系統,稱該系統為鎖相環路,簡稱環路,通常用PLL 表示。

2008-08-15 13:18:46

第十七章IP核之PLL實驗PLL的英文全稱是Phase Locked Loop,即鎖相環,是一種反饋控制電路。PLL對時鐘網絡進行系統級的時鐘管理和偏移控制,具有時鐘倍頻、分頻、相位偏移和可編程

2022-01-18 09:23:55

本帖最后由 zhihuizhou 于 2011-12-21 17:43 編輯

鎖相環PLL原理與應用 第一部分:鎖相環基本原理 一、鎖相環基本組成 二、鑒相器(PD) 三

2011-12-21 17:35:00

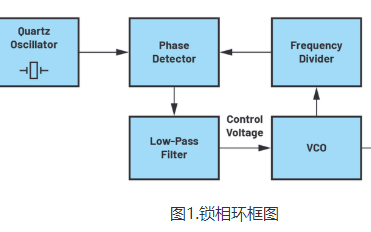

鎖相環路是一種反饋控制電路,簡稱鎖相環(PLL,Phase-Locked Loop)。鎖相環的特點是:利用外部輸入的參考信號控制環路內部振蕩信號的頻率和相位。因鎖相環可以實現輸出信號頻率對輸入信號

2022-01-11 06:34:28

最近在使用AD9510這款芯片配置時鐘,目前程序已經能夠將輸入頻率直接分頻輸出,但是PLL鎖相環這部分始終沒能夠配置成功。請問想要PLL鎖相環控制VCO輸入一個固定的頻率到AD9510里面,寄存器該怎么配置?或者配置順序是怎樣的?電路如下:

2019-03-23 15:04:29

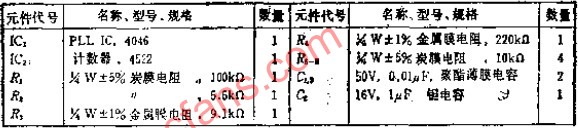

如題,AD9957的鎖相環一直失鎖,不用鎖相環輸出點頻信號時正常的,用了鎖相環后,PLL_LOCK信號一直為低,sync_clk輸出信號也不是穩定的周期信號,環路濾波器的值有點誤差,因為現有的器件沒有那么精確的電容電阻值,問下鎖相環的控制除了控制CFR3之外還有別的要注意的么?

2018-12-10 09:30:24

Actel FPGA PLL鎖相環的最大能達到幾倍頻幾分頻?我在網上查了一下有人說是20倍頻,10分頻,但是我沒有在芯片手冊里面找到資料,想要確認一下。

2014-12-04 11:25:15

pll_dut(20.clk(clk),21.rst_n(rst_n),23.clk_200M(clk_200M),24.locked(locked)25);26 endmodule仿真圖: 在仿真中我們看一看到我們生成的時鐘是200M,然后我們可以用鎖相環生成的標志位給用200M時鐘的電路當復位,如下:

2019-06-17 08:30:00

LabVIEW鎖相環(PLL) 鎖相環是一種反饋電路,其作用是使得電路上的時鐘和某一外部時鐘的相位同步。PLL通過比較外部信號的相位和由壓控晶振(VCXO)的相位來實現同步的,在比較的過程中,鎖相環

2022-05-31 19:58:27

在使用K60的過程中發現自己pllinit()不清楚,才發覺自己鎖相環的概念還不懂,so,趕緊補補……鎖相環(PLL: Phase-locked loops)是一種利用反饋(Feedback)控制

2021-11-04 08:57:18

`可編程鎖相環(PLL)解決方案有多種尺寸和類型可供選擇。 PLL以整數N或小數N形式提供同時根據帶寬利用無源或有源環路濾波器。 可以通過3線串行接口對其進行快速編程同時提供非常低的雜散抑制和較小

2021-04-03 17:00:58

概述:SC9256是SILAN半導體公司生產的一款鎖相環(PLL),大規模集成電路數字調諧系統(DTS),內置2個預分頻系數。所有功能都通過3根串行總線控制。這些大規模集成電路,用于配置高性能的數字調諧系統。它采用貼片16腳封裝和雙列16腳封裝。

2021-05-18 06:51:23

概述:SC9257是杭州士蘭微電子生產的一款數字調諧系統鎖相環(PLL FOR DTS)。該SC9257是鎖相環(PLL)的LSI數字調諧系統(DTS)與內置的2模數預分頻器。所有功能都通過3根串行

2021-05-18 07:27:48

信號源的任何應用的理想選擇,并且利用微帶或陶瓷諧振器拓撲結構可提供出色的相位噪聲性能。測試儀器雷達系統SFS10500H-LF鎖相環SFS10625H-LF鎖相環SFS10640H-LF鎖相環

2021-04-03 17:05:46

實驗原理:1.PLL概念 PLL的完整英文拼寫為Phase-Locked Loop。即相位鎖定的環路,也就是常說的鎖相環。鎖相環在模擬電路和數字電路系統中均有廣泛的使用,很多的MCU芯片如STM32

2017-01-05 00:00:52

`編輯推薦《鎖相環(PLL)電路設計與應用》內容豐富、實用性強,便于讀者自學與閱讀理解,可供電子、通信等領域技術人員以及大學相關專業的本科生、研究生參考,也可供廣大的電子愛好者學習參考。作者簡介作者

2017-09-18 17:56:02

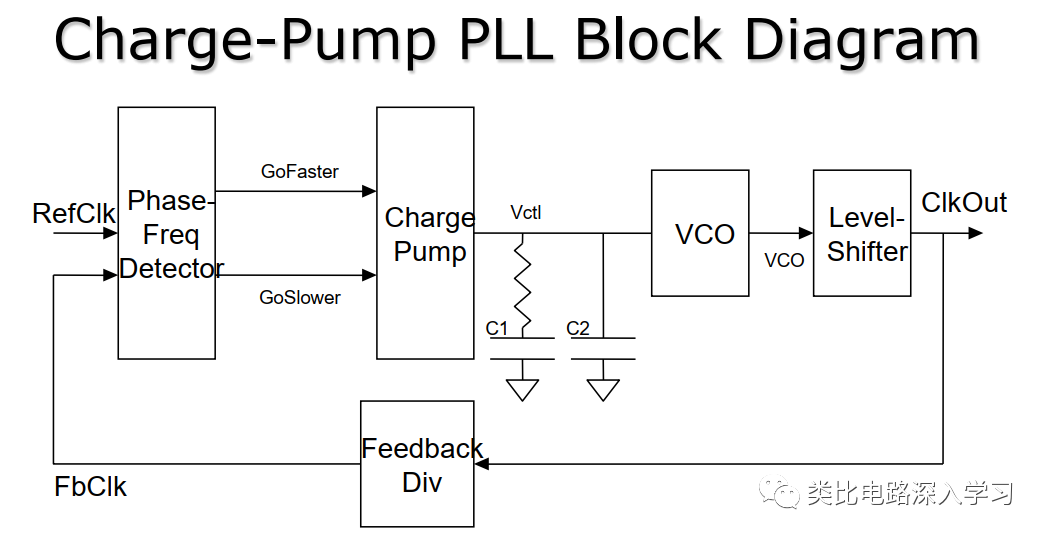

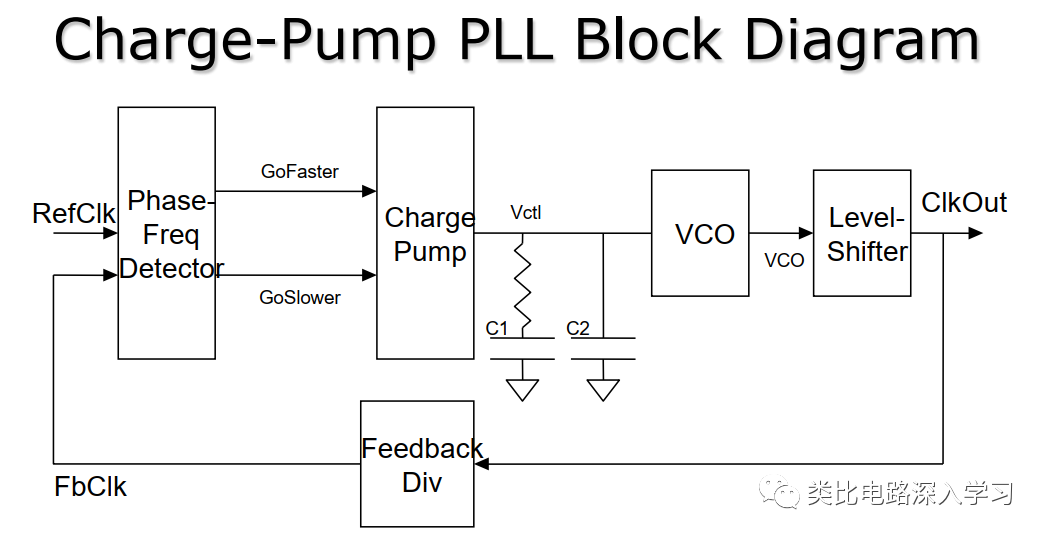

介紹了頻率捕獲、電荷泵鎖相環等熱點應用問題。目錄:第1章 簡介1.1 PLL的性質1.1.1 帶寬1.1.2 線性1.2 本書結構1.3 文獻及注釋1.3.1 推薦書目1.3.2 技術文集1.3.3

2017-08-10 17:44:31

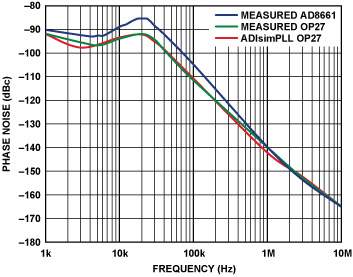

摘要:鎖相環(PLL)電路存在于各種高頻應用中,從簡單的時鐘凈化電路到用于高性能無線電通信鏈路的本振(LO),以及矢量網絡分析儀(VNA)中的超快開關頻率合成器。本文將參考上述各種應用來介紹PLL

2019-10-02 08:30:00

什么是鎖相環 (PLL)?一個鎖相環PLL電路通常由哪些模塊組成?

2022-01-17 06:01:54

鎖相環(PLL)電路存在于各種高頻應用中,從簡單的時鐘凈化電路到用于高性能無線電通信鏈路的本振(LO),以及矢量網絡分析儀(VNA)中的超快開關頻率合成器。今天斑竹帶來干貨好文,參考上述各種應用來

2019-01-28 16:02:54

本文設計了一種寬頻率范圍的CMOS鎖相環(PLL)電路,通過提高電荷泵電路的電流鏡鏡像精度和增加開關噪聲抵消電路,有效地改善了傳統電路中由于電流失配、電荷共享、時鐘饋通等導致的相位偏差問題。設計了

2019-07-08 07:37:37

說明。所提供的組成部分是,沒有負債。它可以自由使用和修改。YouTube視頻顯示組件在行動:自定義鎖相環(PLL)演示使用PSOC5微控制器-YouTube當做,奧迪賽1拉鏈3.4兆字節郵編2.1兆

2018-11-07 17:06:05

設計并調試鎖相環(PLL)電路可能會很復雜,除非工程師深入了解PLL 理論以及邏輯開發過程。本文介紹PLL設計的簡易方法,并提供有效、符合邏輯的方法調試PLL 問題。

2021-04-07 06:28:03

轉載一篇實用好文,源自ADI中文技術支持論壇:http://ezchina.analog.com/message/18945設計并調試鎖相環(PLL)電路可能會很復雜,除非工程師深入了解PLL 理論

2014-08-15 14:08:33

簡介設計并調試鎖相環(PLL)電路可能會很復雜,除非工程師深入了解PLL理論以及邏輯開發過程。本文介紹PLL設計的簡易方法,并提供有效、符合邏輯的方法調試PLL問題。仿真如果不在特定條件下進行仿真

2017-03-17 16:25:46

如果沒有深入了解 PLL 理論以及邏輯開發過程,可能你在設計并調試鎖相環(PLL)電路時會感到非常棘手。那有沒有比較容易理解或學習妙招呢?小A今日就為大家送上一份妙計錦囊,并提供有效、符合邏輯的方法助你調試PLL問題。請往下看~

2021-01-27 06:52:20

控制用微處理器的主要性能有哪些?處理器在調頻(FM)調諧器中的應用是什么?數字調諧系統有哪些性質?怎樣去設計一種基于PLL(鎖相環)合成器的數字調諧系統?

2021-08-17 07:03:36

戴爾筆記本主板LA-9104P的電路原理圖

2020-07-26 08:30:00

數字鎖相環設計源程序PLL是數字鎖相環設計源程序, 其中, Fi是輸入頻率(接收數據), Fo(Q5)是本地輸出頻率.目的是從輸入數據中提取時鐘信號(Q5), 其頻率與數據速率一致, 時鐘上升沿鎖定在數據的上升和下降沿上;頂層文件是PLL.GDF

2009-12-18 10:37:37

最全面最權威的鎖相環PLL原理與應用資料非常經典的資料

2022-12-02 22:39:56

有沒有人用過頻率能達到300M以上的集成鎖相環PLL,急求推薦!!

2015-07-30 17:09:19

求助PLL 鎖相環器件選型指導:1) output: Single End clock2) Work Clock: 1Ghz

2018-09-03 11:49:29

求助:鎖相環(PLL)電路設計與應用; 日本人寫的. [此貼子已經被作者于2010-1-15 18:23:54編輯過]

2009-11-19 15:47:54

。本文就將為大家介紹在DSP系統中如何有效避免噪聲和EMI產生,對其中的電源隔離和鎖相環進行介紹。 電源隔離和鎖相環 如何實現最佳供電是控制噪聲和輻射的最大挑戰。動態負載開關環境很復雜,包括的因素

2018-11-30 17:14:11

本文介紹了電荷泵鎖相環電路鎖定檢測的基本原理,通過分析影響鎖相環數字鎖定電路的關鍵因子,推導出相位誤差的計算公式。并以CDCE72010 為例子,通過實驗驗證了不合理的電路設計或外圍電路參數是如何影響電荷泵鎖相環芯片數字鎖定指示的準確性。

2021-04-20 06:00:37

如題,S3C2440是不是默認不開啟鎖相環PLL的。另外S3C2440與S3C2440A是同一款芯片嗎?為什么這兩款芯片我看到的關于時鐘分頻器設置的參數有些是不一樣的

2019-05-09 04:05:32

Skyworks Solutions 的 SKY72302-21 是一款鎖相環,頻率為 400-6100 MHz,相位噪聲 -80

2023-06-12 17:22:25

acer390筆記本主板電路圖,原理圖資料。

2010-08-22 09:12:51 1398

1398 鎖相環原理

鎖相環路是一種反饋電路,鎖相環的英文全稱是Phase-Locked Loop,簡稱PLL。其作用是使得電路上的時鐘和某一外部時鐘的相位同步。因鎖相環可以

2007-08-21 14:46:04 4879

4879 筆記本主板芯片組

&nbs

2009-12-18 10:41:40 1168

1168 MAX9382在鎖相環中的應用

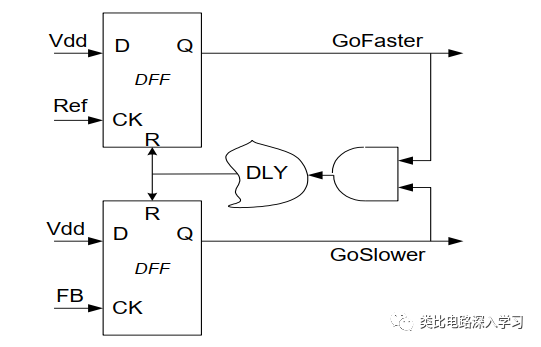

該應用筆記討論了鑒頻鑒相器的指標對鎖相環(PLL)死區及抖動性能的影響。在使用電荷泵環路濾波的PLL設計中,通過產生具有最小脈寬的鑒相輸

2010-01-11 17:54:06 1009

1009

鎖相環(PLL),鎖相環(PLL)是什么意思

PLL的概念

我們所說的PLL。其

2010-03-23 10:47:48 6005

6005 數字PLL,什么是數字PLL

數字PLL

PLL的概念

我們所說的PLL,其實就是鎖相環路,簡稱為鎖相環。許多電子設備要正常工作,通常

2010-03-23 10:50:06 4281

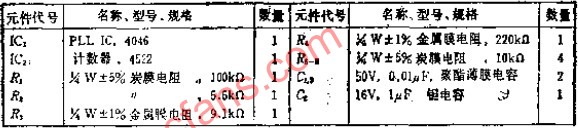

4281 采用PLL(鎖相環)IC的頻率N(1~10)倍增電路

電路的功能

很多電路

2010-05-12 10:51:53 1560

1560

簡介“鎖相環”(PLL)是現代通信系統的基本構建模塊。PLL通常用在無線電接收機或發射機中,主要提供“

2010-10-29 09:59:10 7984

7984

本書是圖解電子工程師實用技術叢書之一,本書主要介紹鎖相環(PLL)電路的設計與應用,內容包括PLL工作原理與電路構成、PLL電路的傳輸特性、PLL電路中環路濾波器的設計方法、PLL電路

2011-09-14 17:55:24 0

0 鎖相環英文為PLL,即PLL鎖相環。可以分為模擬鎖相環和數字鎖相環。兩種分類的鎖相環原理有較大區別,通過不同的鎖相環電路實現不同的功能。

2011-10-26 12:40:28

圖解實用電子技術叢書 鎖相環(PLL)電路設計與應用(日)遠坂俊昭

2015-12-03 16:37:15 125

125 如何設計并調試鎖相環(PLL)電路 pdf

2016-01-07 16:20:08 0

0 ADI官方的關于鎖相環的應用筆記,非常好,我看了很多遍,都有收獲

2016-02-17 11:02:13 0

0 PLL(Phase Locked Loop): 為鎖相回路或鎖相環,用來統一整合時脈訊號,使高頻器件正常工作,如內存的存取資料等。PLL用于振蕩器中的反饋技術。 許多電子設備要正常工作,通常需要外部的輸入信號與內部的振蕩信號同步。

2017-05-22 09:16:18 50850

50850

PLL(Phase Locked Loop),也稱為鎖相環路(PLL)或鎖相環,它能使受控振蕩器的頻率和相位均與輸入參考信號保持同步,稱為相位鎖定,簡稱鎖相。

2017-05-22 10:11:40 8673

8673

鎖相環路是一種反饋控制電路,簡稱鎖相環(PLL,Phase-Locked Loop)。鎖相環的特點是:利用外部輸入的參考信號控制環路內部振蕩信號的頻率和相位。因鎖相環可以實現輸出信號頻率對輸入信號頻率的自動跟蹤,所以鎖相環通常用于閉環跟蹤電路。

2019-09-20 07:05:00 3503

3503

本文檔的主要內容詳細介紹的是鎖相環PLL的原理與應用的詳細資料說明包括了:第一部分:鎖相環基本原理,一、鎖相環基本組成,二、鑒相器(PD)phase discriminator ,三、壓控振蕩器

2020-04-29 08:00:00 13

13 設計并調試鎖相環(PLL)電路可能會很復雜,除非工程師深入了解PLL理論以及邏輯開發過程。本文介紹PLL設計的簡易方法,并提供有效、符合邏輯的方法調試PLL問題。

2020-10-13 10:43:00 12

12 鎖相環(PLL)電路是由壓控振蕩器(VCO)和鑒相器組成的反饋系統,振蕩器信號跟蹤施加的頻率或相位調制信號是否具有正確的頻率和相位。需要從固定低頻率信號生成穩定的高輸出頻率時,或者需要頻率快速變化時,都可以使用PLL。典型應用包括采用高頻率、電信和測量技術實現濾波、調制和解調,以及實現頻率合成。

2020-10-06 14:43:00 4472

4472

鎖相環(PLL)電路存在于各種高頻應用中,從簡單的時鐘凈化電路到用于高性能無線電通信鏈路的本振(LO),以及矢量網絡分析儀(VNA)中的超快開關頻率合成器。

今天斑竹帶來干貨好文,參考上述各種應用來

2021-01-31 08:30:24 19

19 MT-086: 鎖相環(PLL)基本原理

2021-03-21 01:00:51 28

28 鎖相環路是一種反饋控制電路,簡稱鎖相環(PLL,Phase-Locked Loop)。鎖相環的特點是:利用外部輸入的參考信號控制環路內部振蕩信號的頻率和相位。

2022-03-29 09:54:55 11472

11472 聯想筆記本主板電路圖免費下載。

2022-08-02 09:53:13 165

165 鎖相環 (PLL) 電路存在于各種高頻應用中,從簡單的時鐘清理電路到用于高性能無線電通信鏈路的本振 (LO),再到矢量網絡分析儀 (VNA) 中的超快速開關頻率合成器。本文解釋了鎖相環電路的一些構建模塊,并參考了每種應用,以幫助指導新手和鎖相環專家導航器件選擇以及每種不同應用固有的權衡取舍。

2022-12-23 14:03:54 3612

3612

PLL鎖相環版圖設計時應注意以下幾點:1)確定PLL的頻率范圍;2)確定PLL的控制電路;3)確定PLL的調節電路;4)確定PLL的輸出電路;5)確定PLL的濾波電路;6)確定PLL的控制參數;7)確定PLL的輸出參數。

2023-02-14 15:42:59 2085

2085 PLL鎖相環倍頻是一種用于改變輸入信號頻率的技術,它可以將輸入信號的頻率放大或縮小,以達到某種特定的目的。

2023-02-14 15:56:35 1939

1939 PLL是指鎖相環,是一種用于控制頻率和相位的電路,它可以將一個輸入信號的頻率和相位轉換成另一個輸出信號的頻率和相位,從而實現頻率和相位的控制。

2023-02-14 17:19:51 6955

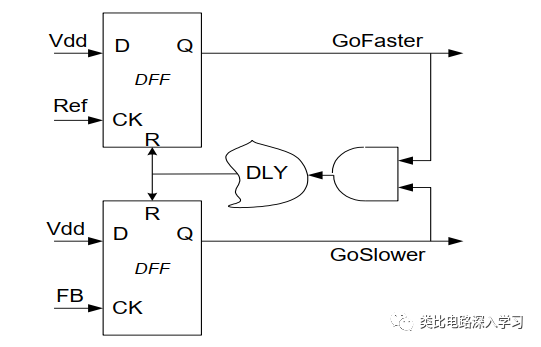

6955 本應用筆記討論了影響鎖相環(PLL)死區和抖動性能的鑒頻鑒相器特性。在采用電荷泵環路濾波器設計的PLL中,提供最短持續時間的鑒相器輸出脈沖幾乎消除了PLL死區行為和相關鎖相環抖動。

2023-02-23 17:52:07 657

657

鎖相環(PLL),作為Analog基礎IP、混合信號IP、數字系統必備IP,廣泛存在于各類電子產品中。

2023-06-02 15:25:14 3557

3557

本文以SoC中的PLL為例,對PLL電路進行設計和仿真。

2023-06-02 15:25:44 4441

4441

以及各種時鐘信號,下面將從這些方面逐一介紹。 一、鎖相環 鎖相環(Phase-Locked Loop, PLL)是一種基于反饋控制的電路,由比較器、低通濾波器、振蕩器和除法器等組成。輸入信號和振蕩器產生的參考信號經過比較器比較,將誤差信號通過低通濾波器進

2023-09-02 14:59:24 1508

1508 PLL和DLL都是鎖相環,區別在哪里?? PLL和DLL都是常用的鎖相環(Phase Locked Loop)結構,在電路設計中具有廣泛的應用。它們的共同作用是將輸入信號和參考信號的相位差控制在一定

2023-09-02 15:06:31 1532

1532 鎖相環PLL和鎖頻環FLL的區別 鎖相環(PLL,Phase Locked Loop)和鎖頻環(FLL,Frequency Locked Loop)是兩種常用于信號調節和數據傳輸的控制回路。雖然它們

2023-09-02 15:06:39 4156

4156 用FPGA的鎖相環PLL給外圍芯片提供時鐘 FPGA鎖相環PLL(Phase-Locked Loop)是一種廣泛使用的時鐘管理電路,可以對輸入時鐘信號進行精確控制和提高穩定性,以滿足各種應用場

2023-09-02 15:12:34 1319

1319 pll鎖相環的作用 pll鎖相環的三種配置模式? PLL鎖相環是現代電子技術中廣泛應用的一種電路,它的作用是將一個特定頻率的輸入信號轉換為固定頻率的輸出信號。PLL鎖相環的三種配置模式分別為

2023-10-13 17:39:48 1102

1102 siumlink中三相鎖相環PLL的輸入怎么實現? siumlink中三相鎖相環PLL的輸入是通過輸入三相交流電壓來實現的。在交流電力系統中,多數情況下使用的是三相電壓,因此三相鎖相環(PLL

2023-10-13 17:39:56 482

482 鎖相環(PLL)基本原理 當鎖相環無法鎖定時該怎么處理的呢? 鎖相環(Phase Locked Loop, PLL)是一種電路系統,它可以將輸入信號的相位鎖定到參考信號的相位。在鎖相環中,反饋回路

2023-10-23 10:10:15 1354

1354 了解鎖相環(PLL)瞬態響應 如何優化鎖相環(PLL)的瞬態響應? 鎖相環(PLL)是一種廣泛應用于數字通信、計算機網絡、無線傳輸等領域的重要電路。PLL主要用于時鐘恢復、頻率合成、時鐘同步等領域

2023-10-23 10:10:20 869

869 頻繁地開關鎖相環芯片的電源會對鎖相環有何影響? 鎖相環(PLL)是一種被廣泛應用在現代電子技術中的集成電路,它是一種反饋控制系統,可以將輸入信號和本地參考信號同步。鎖相環可用于電子時鐘、數字信號處理

2023-10-30 10:16:40 267

267 V CO 輸出本地參考頻率。由于V CO 采用模擬電路, 這將帶來元件 飽和、直流漂移、非線性等問題。因此, 全數字鎖相環得到了越來越廣泛的應用。

本文介紹一種 DD S(D irect D igital Syn thesizer) 與 PLL (Phase L ocked L oop ) 技術

2023-11-09 08:31:40 1

1 今天想來聊一下芯片設計中的一個重要macro——PLL,全稱Phase lock loop,鎖相環。我主要就介紹一下它是什么以及它是如何工作的。

2023-12-06 15:21:13 387

387

電子發燒友App

電子發燒友App

評論