鎖相環(huán) (phase locked loop),顧名思義,就是鎖定相位的環(huán)路。學(xué)過(guò)自動(dòng)控制原理的人都知道,這是一種典型的反饋控制電路,利用外部輸入的參考信號(hào)控制環(huán)路內(nèi)部振蕩信號(hào)的頻率和相位,實(shí)現(xiàn)輸出信號(hào)頻率對(duì)輸入信號(hào)頻率的自動(dòng)跟蹤,一般用于閉環(huán)跟蹤電路。是無(wú)線電發(fā)射中使頻率較為穩(wěn)定的一種方法,主要有VCO(壓控振蕩器)和PLL IC (鎖相環(huán)集成電路),壓控振蕩器給出一個(gè)信號(hào),一部分作為輸出,另一部分通過(guò)分頻與PLL IC所產(chǎn)生的本振信號(hào)作相位比較,為了保持頻率不變,就要求相位差不發(fā)生改變,如果有相位差的變化,則PLL IC的電壓輸出端的電壓發(fā)生變化,去控制VCO,直到相位差恢復(fù),達(dá)到鎖相的目的。能使受控振蕩器的頻率和相位均與輸入信號(hào)保持確定關(guān)系的閉環(huán)電子電路。

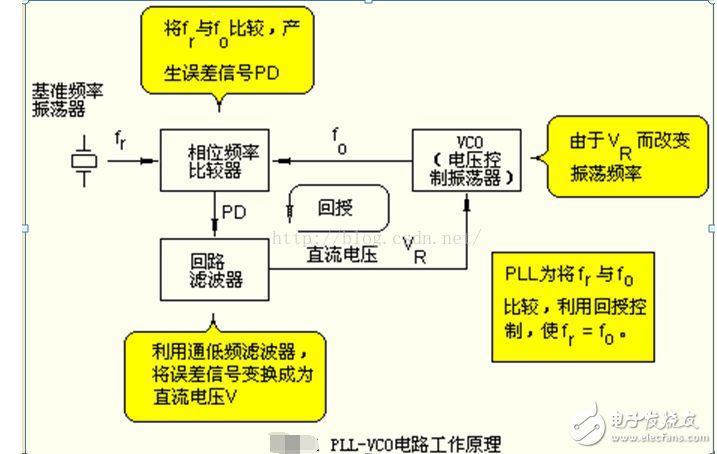

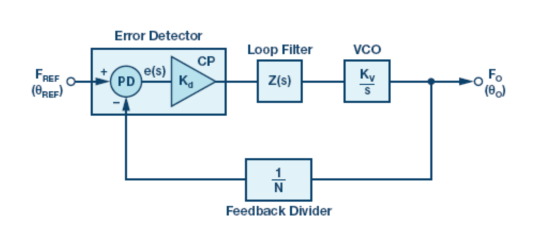

PLL(鎖相環(huán))電路原理

在通信機(jī)等所使用的振蕩電路,其所要求的頻率范圍要廣,且頻率的穩(wěn)定度要高。無(wú)論多好的LC振蕩電路,其頻率的穩(wěn)定度,都無(wú)法與晶體振蕩電路比較。但是,晶體振蕩器除了可以使用數(shù)字電路分頻以外,其頻率幾乎無(wú)法改變。如果采用PLL(鎖相環(huán))(相位鎖栓回路,PhaseLockedLoop)技術(shù),除了可以得到較廣的振蕩頻率范圍以外,其頻率的穩(wěn)定度也很高。此一技術(shù)常使用于收音機(jī),電視機(jī)的調(diào)諧電路上,以及CD唱盤上的電路。

PLL(鎖相環(huán))電路的基本構(gòu)成

PLL(鎖相環(huán))電路的概要

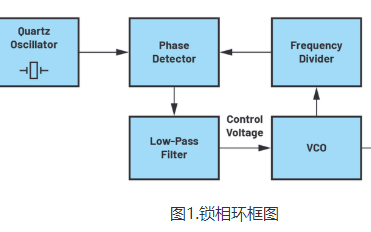

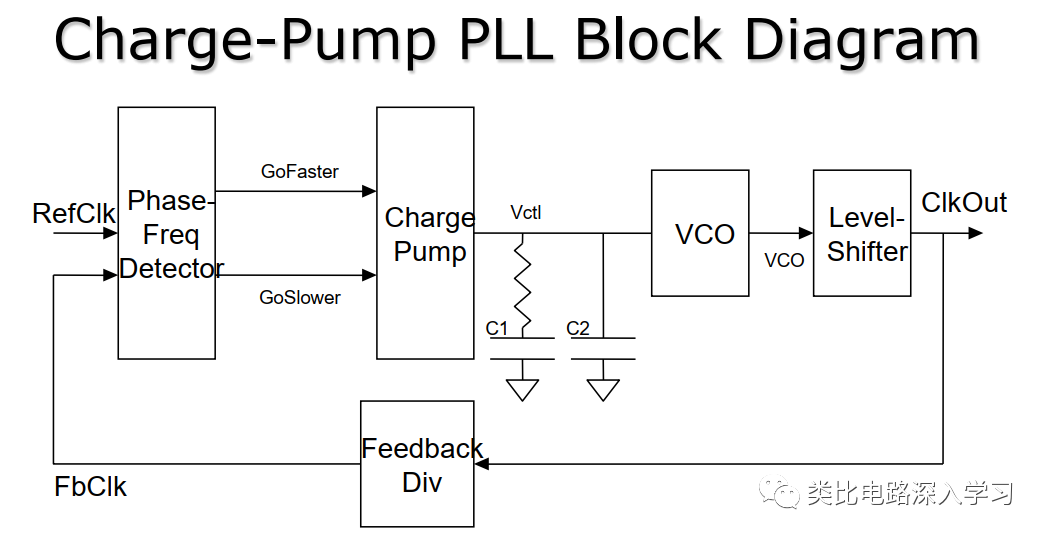

圖1所示的為PLL(鎖相環(huán))電路的基本方塊圖。此所使用的基準(zhǔn)信號(hào)為穩(wěn)定度很高的晶體振蕩電路信號(hào)。

此一電路的中心為相位此較器。相位比較器可以將基準(zhǔn)信號(hào)與VCO (Voltage Controlled Oscillator……電壓控制振蕩器)的相位比較。如果此兩個(gè)信號(hào)之間有相位差存在時(shí),便會(huì)產(chǎn)生相位誤差信號(hào)輸出。

(將VCO的振蕩頻率與基準(zhǔn)頻率比較,利用反饋電路的控制,使兩者的頻率為一致。)

利用此一誤差信號(hào),可以控制VCO的振蕩頻率,使VCO的相位與基準(zhǔn)信號(hào)的相位(也即是頻率)成為一致。

PLL(鎖相環(huán))可以使高頻率振蕩器的頻率與基準(zhǔn)頻率的整數(shù)倍的頻率相一致。由于,基準(zhǔn)振蕩器大多為使用晶體振蕩器,因此,高頻率振蕩器的頻率穩(wěn)定度可以與晶體振蕩器相比美。

只要是基準(zhǔn)頻率的整數(shù)倍,便可以得到各種頻率的輸出。

從圖1的PLL(鎖相環(huán))基本構(gòu)成中,可以知道其是由VCO,相位比較器,基準(zhǔn)頻率振蕩器,回路濾波器所構(gòu)成。在此,假設(shè)基準(zhǔn)振蕩器的頻率為fr,VCO的頻率為fo。

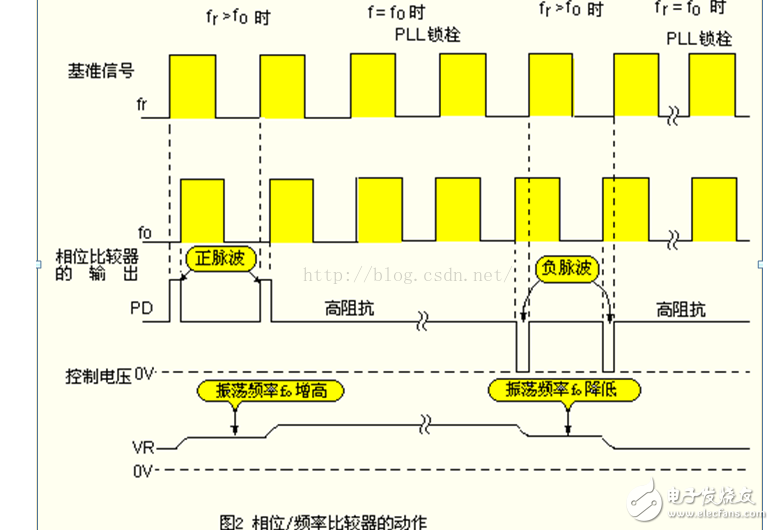

在此一電路中,假設(shè)fr》fo時(shí),也即是VC0的振蕩頻率fo比f(wàn)r低時(shí)。此時(shí)的相位比較器的輸出PD會(huì)如圖2所示,產(chǎn)生正脈波信號(hào),使VCO的振蕩器頻率提高。相反地,如果fr《fo時(shí),會(huì)產(chǎn)生負(fù)脈波信號(hào)。

(此為利用脈波的邊緣做二個(gè)信號(hào)的比較。如果有相位差存在時(shí),便會(huì)產(chǎn)生正或負(fù)的脈波輸出。)

此一PD脈波信號(hào)經(jīng)過(guò)回路濾波器(LoopFilter)的積分,便可以得到直流電壓VR,可以控制VCO電路。

由于控制電壓vr的變化,VCO振蕩頻率會(huì)提高。結(jié)果使得fr=f。在f與f的相位成為一致時(shí),PD端子會(huì)成為高阻抗?fàn)顟B(tài),使PLL(鎖相環(huán))被鎖栓(Lock)。

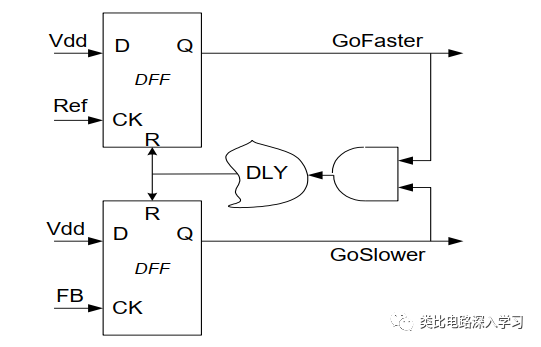

相位比較器的工作原理

此所說(shuō)明的相位比較器為相位.頻率比較器(PFC:Phase-Frequency Comparator)之型式,后述之LSIMC145163P便內(nèi)藏有此一電路。

此一型式的相位此較器并非只做相位的比較,也即是,并非只做之比較,在頻率f不同的場(chǎng)合,也可以做為頻率比較器工作原理。

所謂相位差利時(shí)△與時(shí)間t的關(guān)系為

在只做相位檢出的場(chǎng)合,例如,可能分辨不出是延遲300°或前進(jìn)60°。可是,在相位-頻率比較器中,如果fr》fo則被視為是相位延遲。

回路濾波器的選擇方法

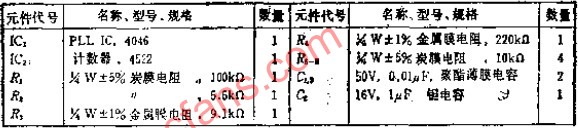

回路濾波器的時(shí)間常數(shù)與PLL(鎖相環(huán))控制的良否有很大的關(guān)系。其詳細(xì)的計(jì)算方法雖然不在此說(shuō)明,但是,基準(zhǔn)頻率fr為l0kHz時(shí),輸往回路濾波器的脈波周期為0.1mS。

為了保持電壓值VR而增大回路濾波器的時(shí)間常數(shù)時(shí),便無(wú)法追蹤VCO的振蕩頻率的變化。如果時(shí)間常數(shù)太小時(shí),會(huì)在VR上出現(xiàn)漣波,使PLL(鎖相環(huán))的穩(wěn)定度惡化。

因此,根據(jù)經(jīng)驗(yàn),回路濾波器的時(shí)間常數(shù),選擇大約為基準(zhǔn)頻率的周期(1/fr)的數(shù)百倍。在此選擇約為數(shù)十mS。

鎖相環(huán)是一種控制晶振使其相對(duì)于參考信號(hào)保持恒定相位的電路,在數(shù)字通信系統(tǒng)中使用比較廣泛。目前微處理器或DSP集成的片上鎖相環(huán),主要作用則是通過(guò)軟件實(shí)時(shí)地配置片上外設(shè)時(shí)鐘,提高系統(tǒng)的靈活性和可靠性。此外,由于采用軟件可編程鎖相環(huán),所設(shè)計(jì)的系統(tǒng)處理器外部允許較低的工作頻率,而片內(nèi)經(jīng)過(guò)鎖相環(huán)微處理器提供較高的系統(tǒng)時(shí)鐘。這種設(shè)計(jì)可以有效地降低系統(tǒng)對(duì)外部時(shí)鐘的依賴和電磁干擾,提高系統(tǒng)啟動(dòng)和運(yùn)行的可靠性,降低系統(tǒng)對(duì)硬件的設(shè)計(jì)要求。

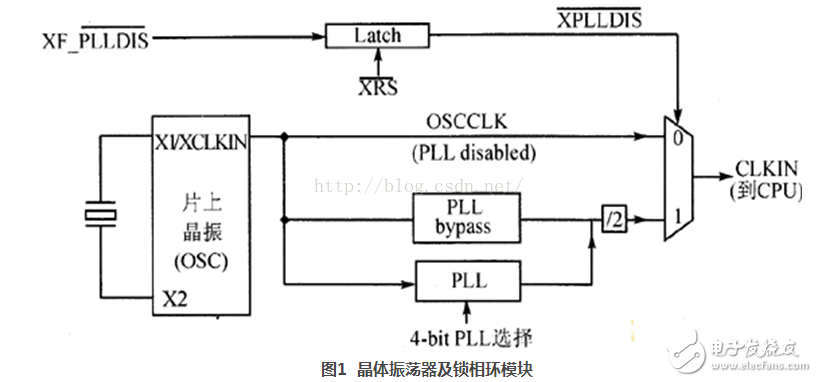

TMS320F28l2處理器的片上晶振和鎖相環(huán)模塊為內(nèi)核及外設(shè)提供時(shí)鐘信號(hào),并且控制器件的低功耗工作模式。片上晶振模塊允許使用2種方式為器件提供時(shí)鐘,即采用內(nèi)部振蕩器或外部時(shí)鐘源。如果使用內(nèi)部振蕩器,必須在XI/XCLKIN和X2這兩個(gè)引腳之間連接一個(gè)石英晶體,一般選用30MHz。如果采用外部時(shí)鐘,可以將輸人的時(shí)鐘信號(hào)直接接到XI/XCLKIN引腳上,而X2懸空,不使用內(nèi)部振蕩器。晶體振蕩器及鎖相環(huán)模塊結(jié)構(gòu)如圖1 所示。

外部XPLLDIS引腳可以選擇系統(tǒng)的時(shí)鐘源。當(dāng)XPLLDIS為低電平時(shí),系統(tǒng)直接采用外部時(shí)鐘或外部晶振作為系統(tǒng)時(shí)鐘;當(dāng)XPLLDIS為高電平時(shí),外部時(shí)鐘經(jīng)過(guò)PLL倍頻后為系統(tǒng)提供時(shí)鐘。系統(tǒng)可以通過(guò)鎖相環(huán)控制寄存器來(lái)選擇鎖相環(huán)的工作模式和倍頻的系數(shù)。表1列出了鎖相環(huán)配置模式。

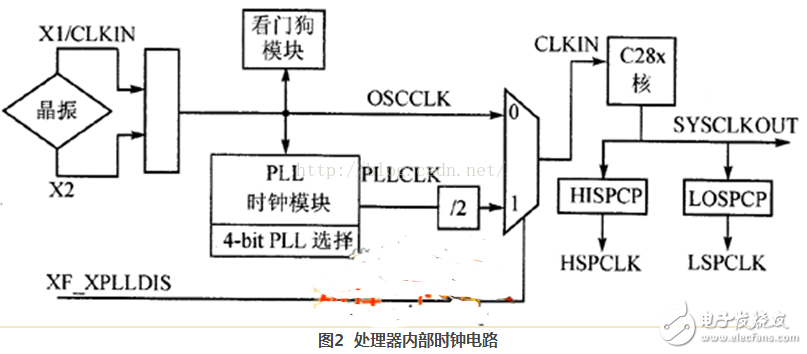

鎖相環(huán)模塊除了為C28x內(nèi)核提供時(shí)鐘外,還通過(guò)系統(tǒng)時(shí)鐘輸出提供快速和慢速2種外設(shè)時(shí)鐘,如圖2所示。而系統(tǒng)時(shí)鐘主要通過(guò)外部引腳XPLLDIS及鎖相環(huán)控制寄存器進(jìn)行控制。因此,在系統(tǒng)采用外部時(shí)鐘并使能PLL(XPLLDIS=1)的情況下,可以通過(guò)軟件設(shè)置C28x內(nèi)核的時(shí)鐘輸人。

如果XPLLDIS為高電平,使能芯片內(nèi)部鎖相環(huán)電路,則可以通過(guò)控制寄存器PLLCR軟件設(shè)置系統(tǒng)的工作頻率。但要注意,在通過(guò)軟件改變系統(tǒng)的工作頻率時(shí),必須等待系統(tǒng)時(shí)鐘穩(wěn)定后才可以繼續(xù)完成其他操作。此外,還可以通過(guò)外設(shè)時(shí)鐘控制寄存器使能外設(shè)時(shí)鐘。在具體的應(yīng)用中,為降低系統(tǒng)功耗,不使用的外設(shè)最好將其時(shí)鐘禁止。外設(shè)時(shí)鐘包括快速外設(shè)和慢速外設(shè)兩種,分別通過(guò)HISPCP和LOSPCP寄存器進(jìn)行設(shè)置。下面給出改變鎖相環(huán)倍頻系數(shù)和外設(shè)時(shí)鐘的具體應(yīng)用程序。

筆記本主板PLL(鎖相環(huán)芯片)型號(hào)

聯(lián)想Y450A-----ICS 9LPRS365BGLF

索尼SONY C22-----ICS954227CGLF

神舟HP500-----RTM875T

三星R18plus---ics932s421bglf

ACER 6530G------RTM876-660

惠普NC6000----ICS950810

聯(lián)想旭日C466M---ICS9LPRS365BGLF 或者 SLG8SP510V

宏碁AZ4720---SLG8SP512V

神舟HP8x0 (TW8)-----SLG8SP513V或者RTM 875T-606

七喜V95/V98(MSI-1435)-----ICS 9LPRS113AKLF

ACER 4930G-----SLG8SP556V

MSI Wind U130--- ICS 9LPRS113AKLF

Asus Eee PC 1005PE-MU17-BK ----ICS9LPR427AGLF

華碩N61-----ICS 9LPRS363DGLF

微星GT628-----ICS 9LPRS113AKLF

華碩g51vx-x1a------------ ICS9LR604AGLF

三星R458--------------------SLG8S5P513V

Acer Aspire 5920g--------------ICS9LPRS365BGLF

hp Pavilion dv9700t---------RTM875T-606

HP CQ45-----------------SLG8SP553V

HP 2710P--------------ICS9LPRS355BKL

HP 2510P----------------ICS9LPRS355^2

HP Pavilion DV2000----------ICS954305EKLF^3

HP Pavilion DV6871-------RTM875t-606

Inspiron 1525------------ICS9LPRS365BKL

Toshiba Tecra A9----------ICS9LPR501SGL

Acer 1810T----------ics9lprs365

HP 8530W-------SLG8SP533V

Dell XPS M1730---------CY28547^3

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論