Altera將在8月16號至10月30號中國區(qū)的9個城市舉辦免費的2012 DSP技術研討會。通過以下主題學習面向Altera FPGA的專用數(shù)字信號處理(DSP)設計方法。了解DSP Builder中基于模型的設計流程以及

2012-08-15 11:48:19 842

842 Altera公司今天在2013年安博會上宣布動視元采用Altera基于FPGA的最新視頻分析成功推出首個基于FPGA的智能交通視頻分析解決方案,較之傳統(tǒng)工控機或DSP的解決方案,基于FPGA的視頻分析可極大提高偵測率和節(jié)省成本...

2013-10-29 18:13:44 1140

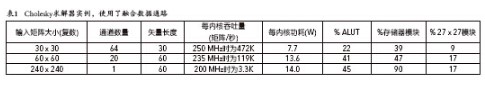

1140 卷積是一種線性運算,其本質(zhì)是滑動平均思想,廣泛應用于圖像濾波。而隨著人工智能及深度學習的發(fā)展,卷積也在神經(jīng)網(wǎng)絡中發(fā)揮重要的作用,如卷積神經(jīng)網(wǎng)絡。本參考設計主要介紹如何基于INTEL 硬浮點的DSP

2018-07-23 09:09:45 7321

7321

及浮點性能,從而使用戶不僅能整合多個 DSP 以縮小板級空間并降低成本,同時還能減少整體的功耗要求。,充分滿足移動網(wǎng)絡領域對通道密度及高質(zhì)量媒體服務日益增長的需求。 2) DSP 部分支持2個

2015-09-17 14:38:59

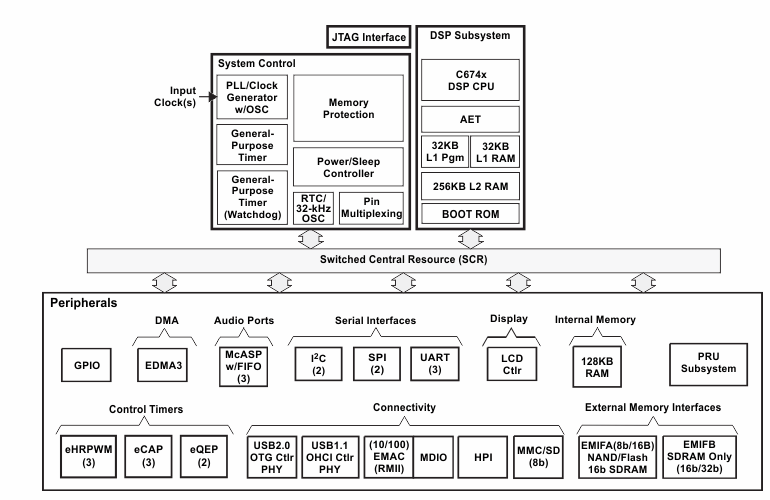

基于TI DSP TMS320C6678、Altera FPGA的CPCI處理卡1、板卡概述 本板卡由我公司自主研發(fā),基于CPCI架構,符合CPCI2.0標準,采用兩片TI DSP

2015-09-11 16:55:46

DSP模塊、高性能浮點DSP功能的FPGA,也是目前發(fā)售的唯一具有硬核PCI Express (PCIe ) Gen3 x8 IP模塊和28-Gbps收發(fā)器的FPGA。 Altera公司產(chǎn)品和企業(yè)

2012-05-14 12:38:53

DSP算法應用及設計

2013-08-14 16:50:36

DSP算法的驗證與模擬一個實際的DSP處理系統(tǒng)必然要使用各種算法,要求DSP系統(tǒng)設計者在選擇某種算法前就精通各種算法的細節(jié)是不現(xiàn)實的。DSP處理系統(tǒng)所選用的算法無非是各種通用算法的組合和改進。革命性

2011-07-16 14:28:11

DSP自動加載過程及程序燒寫的簡化設計

2021-04-02 07:26:05

專業(yè)浮點DSP,其它場合采用定點DSP就足夠了。在實際應用中,采用塊浮點方法能有效提高定點DSP的處理精度。5. 成本要求。在軍事和航天用途中,為了高性能、高可靠性和留有發(fā)展余地,往往盡量采用高性能

2011-07-16 14:27:02

和低成本是其主要的特點。而TMS320C3X/C4X/C67X屬于浮點DSP芯片,運算精度高,用C語言編程方便,開發(fā)周期短,但同時其價格和功耗也相對較高。 DSP應用系統(tǒng)的運算量是確定選用處理能力為

2016-12-16 19:28:54

DSP重要的不是會編程,而是算法的研究(Matlab/Simulnk仿真就不必多說了),光會編程是沒有用處的,也只是個程序員而已,還不如你現(xiàn)在的工作。學FPGA我是從夏宇聞老師編寫的《verilog

2012-03-01 13:55:18

項目的需要時這樣的:每秒輸入dsp 25幀130像素的圖像,需要對圖像進行增強、線性濾波、直方圖處理、圖像分割等簡單的操作,另外還需要進行一些浮點運算想問問各位大神,主頻為300MHZ,運算速度為

2019-01-15 11:25:55

驅動程序,用于與DBM10芯片進行通信。SoC還具有跨平臺工具鏈,該工具鏈支持所有常用的人工智能(AI)和機器學習(ML)框架,以簡化算法部署。工程師可以開發(fā),訓練和測試算法;接下來,他們可以將其保存為標準

2021-03-03 10:46:14

最近出現(xiàn)的 FPGA設計工具和 IP有效減少了計算占用的資源,大大簡化了浮點數(shù)據(jù)通路的實現(xiàn)。而且,與數(shù)字信號處理器不同, FPGA能夠支持浮點和定點混合工作的 DSP數(shù)據(jù)通路,實現(xiàn)的性能超過

2019-08-13 06:42:48

FPGA設計之浮點DSP算法實現(xiàn),DSP算法是很多工程師在設計過程中都會遇到的問題,本文將從FPGA設計的角度來講解浮點DSP算法的實現(xiàn)。FPGA設計之浮點DSP算法實現(xiàn)是賽靈思工程師最新力作,資料不可多得,大家珍惜啊1FPGA設計之浮點DSP算法實現(xiàn)[hide][/hide]

2012-03-01 15:23:56

你好! 按規(guī)格書上說,現(xiàn)在的M4內(nèi)帶有DSP。 我在程序的初始化的時候,利用ROM_FPULazyStackingEnable();使能了浮點運算,那么如果我在做些浮點或是整形的運算,或是一些算法的時候,M4 自己會用DSP做運算,還是需要人為干預?還是有庫可用? 謝謝。

2018-08-16 07:49:39

解sRIO在復雜系統(tǒng)拓撲中的作用是什么?MSGQ模塊包括哪些部分?MSGQ模塊是如何簡化復雜的DSP設計的?

2021-08-06 07:31:43

TI科學家談浮點DSP未來發(fā)展 自十多年前浮點數(shù)字信號處理器(DSP)誕生以來,便為實時信號處理提供了算術上更為先進的備選方案。不過,定點器件至今仍是業(yè)界的主流--當然低成本是主要原因。定點DSP每

2009-11-03 15:18:49

ccs軟件可以在定點dsp平臺開發(fā)浮點運算嗎

2012-10-07 21:54:47

函數(shù)執(zhí)行時間測試 42.3 FIR濾波函數(shù)執(zhí)行時間測試 42.4 復數(shù)FFT函數(shù)執(zhí)行時間測試(單精度浮點) 42.5 復數(shù)FFT函數(shù)執(zhí)行時間測試(基2算法Q31) 42.6 復數(shù)FFT函數(shù)執(zhí)行時間測試(基2

2015-07-17 11:26:02

第7章DSP定點數(shù)和浮點數(shù)(重要) 本期教程主要跟大家講解一下定點數(shù)和浮點數(shù)的基礎知識,了解這些基礎知識對于后面學習ARM官方的DSP庫大有裨益。特別是初學的一定要理解這些基礎知識。 7.1 定點數(shù)和浮點數(shù)概念 7.2 IEEE浮點數(shù) 7.3 定點數(shù)運算 7.4 總結

2015-06-03 11:47:44

今天測試一下EdgeBoard的浮點運算能力(在Linux下),測試的程序比較容易,運行基2 FFT算法,折合成 百萬次浮點運算/每秒 的運算速度來衡量。 運行程序,結果如下: 下面是各類處理器

2021-04-29 12:12:20

恢復積分校正環(huán)節(jié),以便消除系統(tǒng)的穩(wěn)態(tài)誤差,保證伺服電機位置控制的精度。3 實驗結果DSP+ARM雙核控制器硬件電路經(jīng)過測試可用,并在控制器上實現(xiàn)了相關控制算法,驗證了算法的可行性,系統(tǒng)響應速度快,穩(wěn)態(tài)

2021-11-23 07:00:00

日前,Altera發(fā)布新系列Cyclone IV FPGA ,延續(xù)其收發(fā)器技術的領先優(yōu)勢。當前移動視頻、語音和數(shù)據(jù)訪問以及高質(zhì)量3D圖像對低成本帶寬需求與日俱增,與此同時,終端產(chǎn)品市場,如智能電話等

2019-07-31 06:59:45

,因此第(3)步和第(2)步基本是同一步驟了。而采用Host Instrinsics則可以將第一步也簡化,直接調(diào)用對應DSP的c函數(shù),在PC上則生成PC的代碼,在DSP上則生成DSP的代碼。TI提供的c_intrinsics_host_port在PC上模擬C6000的DSP浮點指令,可以自由下載。測試程序的結果均為pass。

2016-12-26 15:07:00

在定點DSP系統(tǒng)中可否實現(xiàn)浮點運算?當然可以,因為DSP都可以用C,只要是可以使用c語言的場合都可以實現(xiàn)浮點運算。

2009-04-07 09:06:17

一.簡介上篇博主已經(jīng)給大家分享了Qualcomm 平臺DSP算法集成的架構和算法原理及其實現(xiàn)的功能,今天我們進一步分享Qualcomm 通用平臺系列的算法集成的實際案例。圖1 DSP簡介二.算法集成

2018-09-25 15:41:21

一.Hexagon DSP簡介DSP( 數(shù)字信號處理器 ):DSP 即數(shù)字信號處理器,是手機芯片里一個專門負責處理數(shù)字信號運算的微處理器。主要應用在實時快速地實現(xiàn)各種數(shù)字信號處理算法。圖1

2018-09-25 15:44:10

簡化DSP48E1片操作

2021-01-27 07:13:57

)。因此,在嘗試PIC32MZ(有點貴的啟動器套件加上用于啟動器套件擴展板的適配器板)之前,我想優(yōu)化代碼,其中許多操作可以在DSP單元中進行,并且我查看了微芯片DSP和浮點庫,但是DSP功能ons被聲明

2019-09-16 10:15:23

在定點DSP系統(tǒng)中可否實現(xiàn)浮點運算?

2019-09-25 05:55:21

在定點DSP系統(tǒng)中可否實現(xiàn)浮點運算?

2019-09-26 05:55:42

開發(fā)平臺:DM8127+ipnc-rdk3.5

現(xiàn)在想建立dsp處理算法,但是ipnc中的demo沒有dsp相關的例程,請問如何建立dsp算法link?

2018-05-28 13:45:50

、改進、替換和維護成本來衡量),您會發(fā)現(xiàn)Altera FPGA 是分立MCU/DSP/ASSP 產(chǎn)品靈活的競爭方案。引言工業(yè)自動化和過程控制生產(chǎn)商一直面臨持續(xù)的全球競爭和經(jīng)濟壓力,商業(yè)模式和利潤不斷受到

2013-11-13 11:17:35

最近在安裝DSP Builder11.0+Matlab2011a+Quratus II 11.0安裝完成后沒有找到Altera DSP Builder Blockset;求大神指教。

2015-06-04 16:01:12

中都能正確的實現(xiàn),為什么在CCS3.3硬件仿真過程中實現(xiàn)不了?本人用的DSP5509,是定點DSP,但是函數(shù)中用到了浮點數(shù),不知道是不是這個原因。但如果是這個原因,為什么在下面的測試函數(shù)里可以得到正確

2013-10-03 13:13:47

為什么很多嵌入式算法 都將浮點數(shù)轉化為無符號整形,再進行運算,有些DSP自帶浮點運算庫的,但還是這樣轉換,本人初到,接觸了一部分歷程,有TI提供的,有大牛自己寫的,感覺對IQmath不熟悉,但知道

2017-04-26 20:07:55

最新做高精度的控制算法,需要做比較高階的數(shù)字濾波器,用的是2812,計算浮點數(shù)乘法非常的慢,關鍵是只能計算32位的浮點數(shù)乘法,造成數(shù)字濾波器的特性都和原來的設計有偏差。大家推薦一款可計算64位浮點數(shù)(double)的DSP吧。

2015-12-15 21:04:41

近來,Altera公司推出業(yè)界首款浮點FPGA,它集成了硬核IEEE754兼容浮點運算功能,提高了DSP性能、設計人員的效能和邏輯效率。據(jù)悉,硬核浮點DSP模塊集成在

2019-07-03 07:56:05

你好,

我想在dsp里做一個音頻降噪處理的算法,剛查看了一下adau1452的性能是極好的,我想進一步了解一下這款芯片。

請問adau1452支持浮點運算嗎?你們提供的例程有沒有關于降噪的?我自己寫的算法代碼是c語言的就可以了吧?

或者說只做降噪處理的(算法有點復雜)有沒有什么更好的dsp推薦?

謝謝

2023-11-29 07:58:31

你好,我想在dsp里做一個音頻降噪處理的算法,剛查看了一下adau1452的性能是最好的,我想進一步了解一下這款芯片。請問adau1452支持浮點運算嗎?你們提供的例程有沒有關于降噪的?我自己寫的算法代碼是c語言的就可以了吧?或者說只做降噪處理的(算法有點復雜)有沒有什么更好的dsp推薦?謝謝

2018-09-25 11:23:38

現(xiàn)想將controlsuite里面的28035的工程,移植到自己的28069板子上,請問怎樣從定點DSP工程移植到浮點DSP,應該怎樣轉換,怎樣處理定點DSP里的Q value,像下面這樣的語句,應該怎么移植呢,謝謝_IQ(0.004)_IQtoIQ15(0.5)

2020-05-08 09:12:32

由于我后面的課題需要涉及較多的浮點運算,只熟悉f103,它不帶FPU,所以軟件浮點算法就顯得很重要了。這幾天在做些小研究和測試。今天又仔細研讀了譚浩強的C語言書的數(shù)據(jù)類型章節(jié),上面有說到c編譯系統(tǒng)總

2021-08-04 06:17:25

浮點是最優(yōu)選的數(shù)據(jù)類型,可確保算法建模和仿真的高精度計算。傳統(tǒng)上,當您想要將這種浮點算法部署到FPGA或ASIC硬件時,您唯一的選擇是將算法中的每種數(shù)據(jù)類型轉換為定點,以節(jié)省硬件資源并加快計算速度

2018-09-11 21:59:16

Altera公司用FPGA做DSP算法的工具

2006-03-25 13:46:45 39

39 DSP算法程序

2006-03-26 14:15:06 85

85

DSP的浮點運算方法

2008-01-16 09:25:05 4

4 定點dsp浮點運算的多媒體視頻教程:

2008-01-24 09:14:21 50

50 定點DSP芯片TMS320F2812實現(xiàn)快速算法應用:摘要:論述了以DSP 芯片TMS320F2812 為核心的一種測量儀器的組成原理、設計思想以及快速定點算法的實現(xiàn)方法,同時對定點和浮點算法結果進

2008-10-30 16:15:31 19

19 針對傳統(tǒng)網(wǎng)格簡化算法在對邊界頂點和邊界邊、累進網(wǎng)格二義性以及網(wǎng)格拓撲關系有效保持等的處理所存在的不足進行了相應的改進,改進的網(wǎng)格簡化算法能有效保持網(wǎng)格模型的形

2009-04-14 08:41:20 11

11

介紹了用VHDL 語言在硬件芯片上實現(xiàn)浮點加/ 減法、浮點乘法運算的方法,并以Altera

公司的FLEX10K系列產(chǎn)品為硬件平臺,以Maxplus II 為軟件工具,實現(xiàn)了6 點實序列浮點加/ 減法

2009-07-28 14:06:13 85

85 本文提出了基于TMS320C2XX 定點DSP 的浮點開平方算法,給出了實現(xiàn)方法及程序清單。實踐證明該方法具有精度高、運算速度快、程序簡單等特點。以美國 TI 公司的TMS320C2XX 為代

2009-07-31 08:11:43 42

42 新型應用受益于浮點DSP的高精度:自十多年前浮點數(shù)字信號處理器 (DSP) 推出以來,就為實時信號處理提供了算術上更為先進的備選方案。然而,定點器件至今仍是業(yè)界的支柱,當然成

2009-09-25 10:43:01 4

4 簡化Xilinx和Altera FPGA調(diào)試過程:通過FPGAViewTM 解決方案,如混合信號示波器(MSO)和邏輯分析儀,您可以在Xilinx 和Altera FPGA 內(nèi)部迅速移動探點,而無需重新編譯設計方案。能夠把內(nèi)部FPGA

2009-11-20 17:46:26 26

26 在基于浮點DSP 的實時運算中,求平方根算法占用了大量的運算時間,成為運算中的瓶頸之一。本文提出一種基于二進制浮點數(shù)結構和查表法結合的快速求浮點數(shù)平方根方法。理論

2009-12-18 16:43:15 34

34 基于浮點編碼遺傳算法的H二控制器設計:本文研究了利用浮點編碼的遺傳算法的H-控制器的設計方法。文中對于利用遺傳算法尋優(yōu)的幾個難點:如容許空間的確定、適應值函數(shù)的選取

2010-01-12 16:59:43 9

9 針對如何靈活應用高性能32/64位浮點DSP TMS320C672x提供的性能優(yōu)良的外部存儲器接口(EMIF),分析了EMIF的特點和使用技巧,以TMS320C6722B型 DSP為例,設計了EMIF與外部HY57V281620A型SDR

2010-12-11 15:36:52 20

20 助力航空和軍事應用,Altera與Mentor Graphics在DO-254上展開合作

越來越多的航空和軍事應用需要通過DO-254認證的組件,對此,Altera公司和Mentor Graphics公司日前宣布,雙方展開合

2008-08-23 15:14:45 399

399 TMS320VC33 高性能浮點DSP芯片

TMS320VC33是美國TI公司新推出的TMS320C3X系列新一代浮點式數(shù)字信號處理器。它以高速、低功耗、低成本、易于開發(fā)為顯著特

2009-12-08 14:33:27 6467

6467

浮點DSP,浮點DSP是什么意思

浮點DSP可以完成整數(shù)和實數(shù)運算,它的數(shù)據(jù)格式分為階碼和尾數(shù)(有一位可以設為符號位)。通常浮點DSP的

2010-03-26 14:57:01 2269

2269 Altera公司日前演示了使用FPGA的浮點DSP新設計流程,這是業(yè)界第一款基于模型的浮點設計工具,支持在FPGA中實現(xiàn)復數(shù)浮點DSP算法。伯克萊設計技術公司 (Berkeley Design Technology, Inc, BDTI) 進行

2011-09-15 08:48:58 898

898 Altera公司日前演示了使用FPGA的浮點DSP新設計流程,這是業(yè)界第一款基于模型的浮點設計工具,支持在FPGA中實現(xiàn)復數(shù)浮點DSP算法。

2011-09-15 09:07:10 613

613 WP409利用Xilinx FPGA打造出高端比特精度和周期精度浮點DSP算法實現(xiàn)方案: High-Level Implementation of Bit- and Cycle-Accurate Floating-Point DSP Algorithms with Xilinx FPGAs

2012-01-26 18:03:05 25

25 Altera Stratix25DSP在DSP設計實驗教學中的應用

2012-08-15 16:30:44 28

28 電子發(fā)燒友網(wǎng)核心提示 :Altera公司昨日宣布,在業(yè)界率先在28 nm FPGA器件上成功測試了復數(shù)高性能浮點數(shù)字信號處理(DSP)設計。獨立技術分析公司Berkeley設計技術有限公司(BDTI)驗證

2012-10-31 09:24:47 31

31 STM32F4的浮點 DSP 運算效率不高

2015-12-07 17:55:14 0

0 程序設計、尋址方式、COFF結構和DSP芯片特殊功能的編程;根據(jù)實際應用討論了常用算法,最后介紹了兩種實驗系統(tǒng),即基TMS320VC33、TMS320C6722的浮點實驗系統(tǒng)。

2016-04-26 10:53:09 2

2 程序設計、尋址方式、COFF結構和DSP芯片特殊功能的編程;根據(jù)實際應用討論了常用算法,最后介紹了兩種實驗系統(tǒng),即基TMS320VC33、TMS320C6722的浮點實驗系統(tǒng)。

2016-04-26 10:53:09 2

2 程序設計、尋址方式、COFF結構和DSP芯片特殊功能的編程;根據(jù)實際應用討論了常用算法,最后介紹了兩種實驗系統(tǒng),即基TMS320VC33、TMS320C6722的浮點實驗系統(tǒng)。

2016-04-26 10:53:09 1

1 TI的TMS320系列DSP已經(jīng)有多寬浮點運算

2016-06-21 17:56:39 10

10 前言本文目的是演示如何使用STM32F30x 內(nèi)部的DSP 進行浮點快速傅立葉變換(FFT),為聯(lián)系實際應用

2017-09-18 06:44:00 9050

9050 摘 要: 簡要分析了偽隨機序列中應用廣泛的m序列,Gold序列及平衡Gold碼的概念、原理和應用。提出了一種基于Altera的DSP Builder工具箱的偽隨機序列產(chǎn)生器設計方法,并通過設計實例

2017-10-30 10:37:11 0

0 DSP的比較優(yōu)勢是浮點算法擁躉者們在浮點定點之爭的話題中常提及的,也為大多數(shù)嵌入式設計工程師所熟知。 然而,由于電路復雜性和制造工藝上的原因,浮點處理器與定點處理器相比在成本和功耗上通常具有明顯的劣勢,從而導致浮點處理器的卓越處理能力、大

2017-11-02 11:26:22 0

0 引 言 DSP結構可以分為定點和浮點型兩種。其中,定點型DSP可以實現(xiàn)整數(shù)、小數(shù)和特定的指數(shù)運算,它具有運算速度快、占用資源少、成本低等特點;靈活地使用定點型DSP進行浮點運算能夠提高運算的效率

2017-11-02 11:26:42 2

2 DSP的比較優(yōu)勢是浮點算法擁躉者們在浮點定點之爭的話題中常提及的,也為大多數(shù)嵌入式設計工程師所熟知。 然而,由于電路復雜性和制造工藝上的原因,浮點處理器與定點處理器相比在成本和功耗上通常具有明顯的劣勢,從而導致浮點處理器的卓越處理能力、大

2017-11-02 11:46:27 0

0 定點DSP和浮點DSP的區(qū)別與比較 定點與浮點運算DSP 的比較DSP數(shù)字信號處理器是一種特別適合于進行數(shù)字信號處理的微處理器,主要用于實時快速地實現(xiàn)各種數(shù)字信號處理算法。 定點運算DSP

2017-12-04 15:57:19 11

11 描述了浮點型算法的加、減、乘、除的verilog代碼,編寫了6位指數(shù)位,20位小數(shù)位的功能實現(xiàn)并且通過仿真驗證

2018-01-16 14:15:54 1

1 2014年4月23號,北京Altera公司 (Nasdaq: ALTR) 今天宣布在FPGA浮點DSP性能方面實現(xiàn)了變革。Altera是第一家在FPGA中集成硬核IEEE 754兼容浮點運算功能

2018-02-11 13:34:00 6954

6954 浮點運算是計算機運算的重要方式,較之定點運算有著計數(shù)范圍寬有效精度高的特點。在各種工程計算和科學計算中有著廣泛應用。目前浮點運算大多采用DSP芯片實現(xiàn),具有算法簡單,精度高的優(yōu)點。但同時由于浮點運算

2018-04-10 14:25:53 17

17 此次為期30分鐘的視頻演示介紹了 Xilinx 提供的 DSP 設計工具。我們從帶有浮點 MATLAB? 算法的 AccelDSP? 著手,并且與測試平臺一起生成 VHDL 或 Verilog 模型。

2018-05-24 13:47:00 4141

4141

Altera市場行銷部高級副總裁Danny Biran介紹了該公司28nm的DSP創(chuàng)新,擬2011年1季度面試,開發(fā)軟件DSPB-AB今年5月即可面試。這些Stratix V家族DSP鎖定三大海

2018-06-22 05:28:00 3927

3927 本文檔的主要內(nèi)容詳細介紹的是DSP28335的測試總結資料和程序免費下載包括了:1 DSP的PWM信號,2 DSP的CAN通信,3 DSP的32位浮點運算測試,4 DSP定時器中斷,5 DSP看門狗復位,6 軟件報錯與處理,7 備注與注意事項,8 附錄 C源程序。

2019-08-20 08:00:00 18

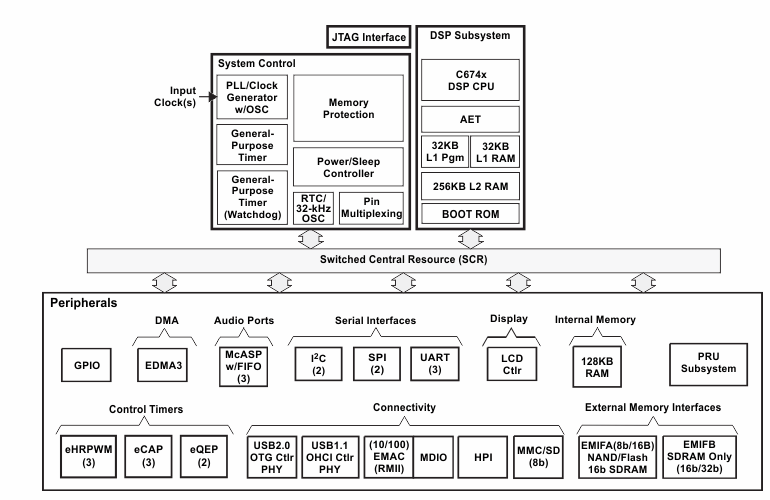

18 TI TMS320C6748定點/浮點DSP C674x處理器提供語音、算法、圖像、視頻等多種類型實驗提供教學實驗指導手冊和完整的實驗代碼。

2019-11-10 10:20:45 2761

2761

的邏輯和布線資源。通常一個單精度浮點加法器需要500個查找表(LUT),單精度浮點要占用30%的LUT,指數(shù)和自然對數(shù)等更復雜的數(shù)學函數(shù)需要大約1000個LUT。因此隨著DSP算法越來越復雜,F(xiàn)PGA

2020-01-14 16:19:55 3213

3213

德州儀器(TI)日前發(fā)布的兩款超低功耗浮點DSP──TMS320C6745、TMS320C6747,以及一款結合ARM應用處理器與浮點DSP的OMAP-L137。三款組件均以TI C674x DSP核心為基礎,具備浮點優(yōu)勢與過去定點裝置獨具的聯(lián)機外圍、低功耗及低成本等特性。

2021-01-06 11:15:00 2691

2691

該問題由某客戶提出,發(fā)生在 STM32F407IGT6 器件上。據(jù)其工程師講述:由于在其產(chǎn)品中,需要使用STM32進行大量的浮點數(shù)以及浮點DSP運算,所以針對STM32的浮點數(shù)運算能力及 DSP

2021-04-28 15:17:02 10

10 先進的數(shù)字處理器IC要求通過單獨的DC參數(shù)和高速數(shù)字自動測試設備(ATE)測試,以達到質(zhì)保要求。這帶來了很大的成本和組織管理挑戰(zhàn)。本文將介紹ADGM1001 SPDT MEMS開關如何助力一次性通過

2022-11-30 09:39:21 530

530 運算的運算步驟遠比定點運算繁瑣,運算速度慢且所需硬件資源大大增加,因此基于浮點運算的LMS算法的硬件實現(xiàn)一直以來是學者們研究的難點和熱點。 本文正是基于這種高效結構的多輸入FPA,在FPGA上成功實現(xiàn)了基于浮點運算的LMS算法。測試

2023-12-21 16:40:01 228

228

電子發(fā)燒友App

電子發(fā)燒友App

評論