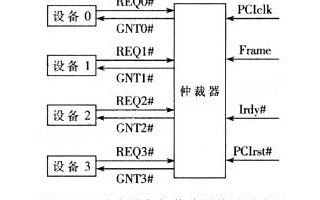

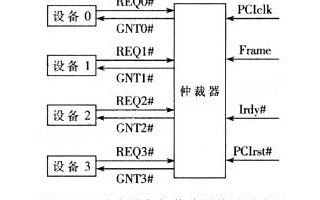

,為了使PCI設(shè)備能夠更方便地應(yīng)用在嵌入式系統(tǒng)中,本文介紹了一種基于CPLD(復(fù)雜可編程邏輯器件)的PCI總線仲裁器的設(shè)計(jì)方法,此方法可以為系統(tǒng)量身定制適合于系統(tǒng)本身的PCI總線仲裁器。而不必局限于特定的芯片要求,在體積、功能、成本等諸多方面都有很好的應(yīng)用前景。

2020-06-26 09:30:00 928

928

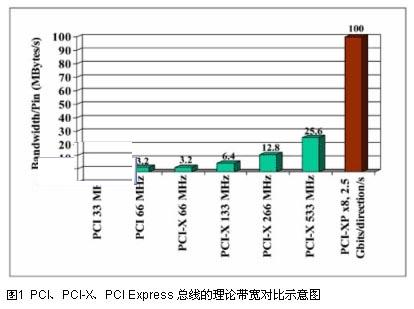

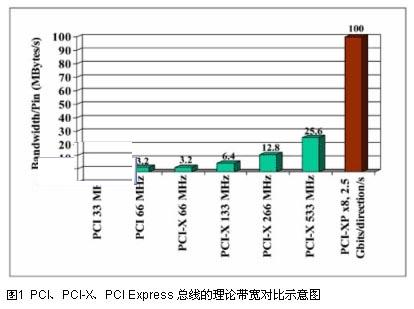

本白皮書主要著眼已經(jīng)得到廣泛采用的PCI 總線的成功優(yōu)勢(shì)所在,同時(shí)詳細(xì)介紹下一代高性能I/O 互連技術(shù)PCI Express 它將作為標(biāo)準(zhǔn)的局域I/O 總線被廣泛應(yīng)用于未來(lái)各種計(jì)算機(jī)平臺(tái)。本白皮書

2019-05-10 07:00:07

以實(shí)現(xiàn)ISA總線到PCI總線的無(wú)縫連接,這為目前仍存在的ISA插件移植到PCI提供了極大的方便。利用PCI9052的ISA模式進(jìn)行PCI的開發(fā)可以簡(jiǎn)化設(shè)備開發(fā)過(guò)程,但難度還是較大。設(shè)計(jì)者不僅要理解掌握

2018-12-17 11:23:00

PCI總線接口的開發(fā)提供了一種簡(jiǎn)潔的方法,設(shè)計(jì)者只需設(shè)計(jì)出本地總線接口控制電路,即可實(shí)現(xiàn)與PCI總線的高速數(shù)據(jù)傳輸。圖3是應(yīng)用PCI9054作為接口芯片,開發(fā)PCI總線擴(kuò)展卡的總體硬件框架圖 下面簡(jiǎn)單

2018-12-05 10:12:42

。PCI總線協(xié)議比較復(fù)雜,用戶可以根據(jù)具體實(shí)際需求選擇相應(yīng)的開發(fā)方式,一般,PCI總線開發(fā)采用兩種方式,一是采用CPLD來(lái)設(shè)計(jì)控制接口。它的最大好處是比較靈活,用戶可以根據(jù)自己的需要開發(fā)出適合于特定

2008-10-09 11:23:38

PCI總線特點(diǎn)是什么?PCI接口開發(fā)現(xiàn)狀如何?如何去設(shè)計(jì)PCI接口?

2021-04-29 07:09:04

與CPLD一方作為主控方,另一方作為PCI從設(shè)備。這樣做的目的是為了簡(jiǎn)化問題,降低系統(tǒng)造價(jià)。 PCI總線上信號(hào)線雖然多,但并不是每個(gè)信號(hào)都要用到。實(shí)際上PCI設(shè)備也并不會(huì)支持所有的信號(hào)線,比如錯(cuò)誤報(bào)告信號(hào)

2019-04-24 07:00:09

pci總線的含義是什么90年代,隨著圖形處理技術(shù)和多媒體技術(shù)的廣泛應(yīng)用,在以Windows為代表的圖形用戶接口(GUI)進(jìn)入PC機(jī)之后,要求有高速的圖形描繪能力和I/O處理能力。這不僅要求圖形適配卡

2008-12-09 13:46:13

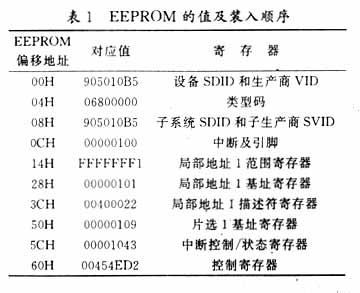

PCI9052是美國(guó)PLX科技有限公司推出的一款PCI總線從屬接口芯片(但不具有DMA功能)。它可以提供高性能的從目標(biāo)PCI接口板卡與PCI總線的連接,支持寬范圍速率的本地總線,最高可達(dá)132 MB

2021-04-15 07:02:21

C語(yǔ)言和匯編語(yǔ)言在開發(fā)單片機(jī)時(shí)各有哪些優(yōu)缺點(diǎn)?C或匯編語(yǔ)言可以用于單片機(jī),C++能嗎?搞單片機(jī)開發(fā),一定要會(huì)C嗎?8088和196芯片單片機(jī)教材,請(qǐng)問哪里可以找到?初學(xué)者到底是應(yīng)該先學(xué)C還是匯編?

2021-10-19 07:51:02

什么是c語(yǔ)言?什么是匯編語(yǔ)言?C語(yǔ)言和匯編語(yǔ)言的優(yōu)缺點(diǎn)是什么?

2021-10-14 08:48:23

一 什么是Compact PCI?Compact PCI是一種基于標(biāo)準(zhǔn)PCI總線的小巧而堅(jiān)固的高性能總線技術(shù)。1994年P(guān)ICMG(PCI Computer Manufacturer’s Group

2009-06-14 16:25:08

IIC總線通訊接口器件的CPLD實(shí)現(xiàn)摘要:介紹了采用ALTERA公司的可編程器件EPF10K10LC84-3實(shí)現(xiàn)IIC總線的通訊接口的基本原理,并給出了部分的VHDL語(yǔ)言描述。該通訊接口與專用的接口芯片相比,具有使用靈活、系統(tǒng)配置方便的特點(diǎn)。 [/hide]

2009-10-30 14:57:35

什么是Compact PCI?Compact PCI是一種基于標(biāo)準(zhǔn)PCI總線的小巧而堅(jiān)固的高性能總線技術(shù)。1994年P(guān)ICMG(PCI Computer Manufacturer’s Group

2009-06-14 16:06:55

CPLD技術(shù)在PCI總線開關(guān)中的應(yīng)用使用CPLD技術(shù)開發(fā)PCI板卡有什么優(yōu)點(diǎn)

2021-04-08 06:47:28

現(xiàn)有PCI+ISA全長(zhǎng)卡主板,插在底板上,然后通過(guò)底板擴(kuò)展PCI板卡,未插板卡時(shí),平臺(tái)可以正常啟動(dòng),但插入PCI話務(wù)員板卡后,平臺(tái)無(wú)法啟動(dòng)(主板不起),且只要有該PCI話務(wù)員板卡,無(wú)論有無(wú)其他PCI

2013-01-29 23:03:09

, 因此如何來(lái)實(shí)現(xiàn)該監(jiān)控系統(tǒng)中大量數(shù)據(jù)的高效、快速、準(zhǔn)確地采集和傳輸成為設(shè)計(jì)該監(jiān)控系統(tǒng)所面臨的一個(gè)主要難題。而本文所研究的基于PCI 總線的高速數(shù)據(jù)通信卡的設(shè)計(jì)正是解決上述難題的關(guān)鍵技術(shù)之一。PCI

2010-09-22 08:51:09

所示。圖7 程序主界面 結(jié)語(yǔ) 本設(shè)計(jì)實(shí)現(xiàn)了基于DSP技術(shù)與PCI總線的數(shù)據(jù)采集處理卡,開發(fā)了虛擬式實(shí)時(shí)多通道FFT頻譜分析儀的應(yīng)用程序以及主機(jī)監(jiān)控界面。通過(guò)在數(shù)據(jù)采集卡上集成DSP,使得該卡不但

2009-04-20 10:51:10

獨(dú)立的配置空間,可實(shí)現(xiàn)即插即用。這些優(yōu)點(diǎn)使得PCI總線在數(shù)據(jù)采集、嵌入式系統(tǒng)和測(cè)控等領(lǐng)域得到廣泛應(yīng)用。實(shí)現(xiàn)PCI總線協(xié)議目前主要有專用接口芯片和CPLD實(shí)現(xiàn)兩種方式。專用接口芯片使用簡(jiǎn)單方便、工作穩(wěn)定

2019-05-29 05:00:02

發(fā)送10~50 Mbit·s-1的任意速率LVDs數(shù)據(jù)。因PCI總線速度高、兼容性好、可靠性高且成本低,使其在各種與主機(jī)通信的總線技術(shù)中優(yōu)勢(shì)明顯。FPGA資源豐富、速度快、開發(fā)方便快捷,因此在高速

2019-07-18 06:35:45

的部分功能,造成了資源的浪費(fèi),同時(shí)接口芯片占用了板卡上的有限空間,給應(yīng)用設(shè)計(jì)帶來(lái)不便。(2)使用可編程邏輯器件實(shí)現(xiàn)PCI總線控制器,使用這種方式開發(fā)難度大,消耗周期長(zhǎng),系統(tǒng)驗(yàn)證困難,且不具備通用性

2018-12-04 10:35:21

及MAXPLUSII NT設(shè)計(jì)平臺(tái)上,針對(duì)目標(biāo)器件FLEX10K 100E,利用VHDL硬件描述語(yǔ)言,設(shè)計(jì)了PCI總線到摩托羅拉CPU的FPGA橋接芯片。該芯片介于PCI總線與摩托羅拉CPU之間,提供兩種總線

2019-04-17 07:00:06

一種可行的方案就是利用CPLD作為溝通單片機(jī)與PCI設(shè)備間的橋梁,充分利用CPLD中I/O資源豐富,用戶可自定制邏輯的優(yōu)勢(shì),來(lái)幫助單片機(jī)完成與PCI設(shè)備間的通信任務(wù)。

2021-04-29 06:28:43

如何去采用PCI9030芯片實(shí)現(xiàn)從ISA總線到PCI總線的轉(zhuǎn)接卡的設(shè)計(jì)?有哪些方法?其過(guò)程是怎樣的?

2021-07-01 08:00:36

如何找到芯片中寄存器的地址呢?如何用C語(yǔ)言和匯編語(yǔ)言的方式實(shí)現(xiàn)LED流水燈的設(shè)計(jì)呢?

2022-02-25 06:25:23

沁恒工程師您好,公司打算開發(fā)一款CAN總線板卡,我看了貴司的CH368芯片,打算使用CH368外加SJA1000實(shí)現(xiàn),麻煩您幫忙評(píng)估下是否可以實(shí)現(xiàn)?感謝!

2022-10-10 09:00:58

。在軟件設(shè)計(jì)上,軟件以C語(yǔ)言和匯編語(yǔ)言相結(jié)合的方法實(shí)現(xiàn)了系統(tǒng)的控制。最后提出了模糊控制調(diào)節(jié)PID參數(shù)的控制策略。

2021-05-12 06:44:08

怎么實(shí)現(xiàn)基于IP內(nèi)核的PCI總線接口設(shè)計(jì)?

2021-05-27 06:34:05

總線的電氣規(guī)范大部份跟PCI相同,只是增加了一些儀器特性。基于以上考慮,我們決定通過(guò)設(shè)計(jì)一個(gè)PCI接口卡來(lái)系統(tǒng)地了解利用接口芯片PCI 9030開發(fā)PXI模塊的過(guò)程和方法。2、硬件設(shè)計(jì)目前實(shí)現(xiàn) PCI

2019-05-05 09:29:33

PCI總線特點(diǎn)及開發(fā)現(xiàn)狀PCI接口配置空間的實(shí)現(xiàn)求一款在PCI總線上利用FPGA技術(shù)設(shè)計(jì)PCI總線接口的設(shè)計(jì)方案

2021-04-15 06:17:20

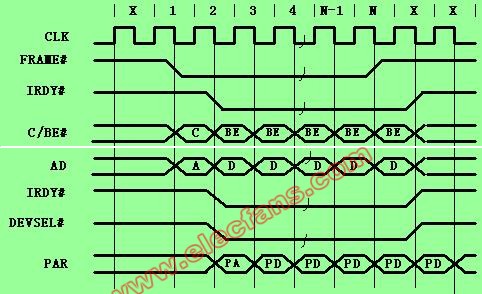

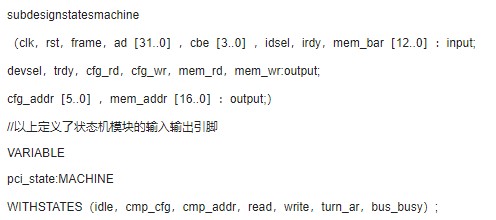

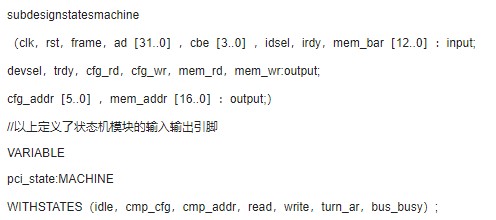

設(shè)計(jì)應(yīng)用中有很大的局限性。因此,使用通用型CPLD器件設(shè)計(jì)簡(jiǎn)易型PCI接口有很大的現(xiàn)實(shí)意義。在Compact接口的CPLD設(shè)計(jì)中,筆者根據(jù)PCI總線傳輸時(shí)序來(lái)進(jìn)行狀態(tài)機(jī)構(gòu)造,并使用VHDL語(yǔ)言進(jìn)行功能

2019-06-17 05:00:11

進(jìn)行測(cè)試和控制。板卡硬件結(jié)構(gòu)如圖1 所示,主要由PCI 協(xié)議接口芯片、1553B 總線控制器、收發(fā)器和變壓器等組成。3 PCI-1553B 接口卡功能實(shí)現(xiàn)3.1 1553B 協(xié)議1553B 總線系統(tǒng)中

2019-05-21 05:00:22

開發(fā)環(huán)境:workbench3.0目標(biāo)機(jī)操作系統(tǒng):vxworks6.6處理器架構(gòu):x86現(xiàn)在想在vxbus架構(gòu)下編寫PCI板卡驅(qū)動(dòng),板卡型號(hào):PCI1612,RS422卡。

2020-11-25 10:59:41

C語(yǔ)言和匯編語(yǔ)言在開發(fā)單片機(jī)時(shí)各有哪些優(yōu)缺點(diǎn)?

2023-10-26 07:47:46

C語(yǔ)言和匯編語(yǔ)言在開發(fā)單片機(jī)時(shí)各有哪些優(yōu)缺點(diǎn)?

2023-10-30 06:32:30

VHDL語(yǔ)言和verilog語(yǔ)言有何區(qū)別

2019-03-28 06:52:52

VHDL語(yǔ)言和verilog語(yǔ)言有何區(qū)別

2019-03-29 07:55:09

ABPLC通訊協(xié)議過(guò)程是怎樣的?通訊C#編程上位機(jī)語(yǔ)言和PLC是如何實(shí)現(xiàn)通訊的?

2021-09-29 06:57:27

的配置空間,可實(shí)現(xiàn)即插即用。這些優(yōu)點(diǎn)使得PCI總線在數(shù)據(jù)采集、嵌入式系統(tǒng)和測(cè)控等領(lǐng)域得到廣泛應(yīng)用。實(shí)現(xiàn)PCI總線協(xié)議目前主要有專用接口芯片和CPLD實(shí)現(xiàn)兩種方式。專用接口芯片使用簡(jiǎn)單方便、工作穩(wěn)定可靠

2019-06-20 05:00:03

采用PCI總線流水式高速數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)摘要:目前基于PCI總線的高速數(shù)據(jù)采集系統(tǒng),大多采用高速A/D,CPLD或FPGA,FIFO或雙端口RAM以及通用PCI接口來(lái)設(shè)計(jì),其通用性、靈活性差,不能

2009-10-30 15:09:49

IP核來(lái)實(shí)現(xiàn)PCI接口,利用基于PCI協(xié)議的IP核來(lái)實(shí)現(xiàn)PCI接口,這種設(shè)計(jì)開發(fā)速度較快,靈活性較好,但是IP核價(jià)格昂貴。采用FPGA實(shí)現(xiàn)PCI總線協(xié)議。采用CPLD/FPGA等可編程邏輯器件實(shí)現(xiàn)PCI

2019-05-30 05:00:02

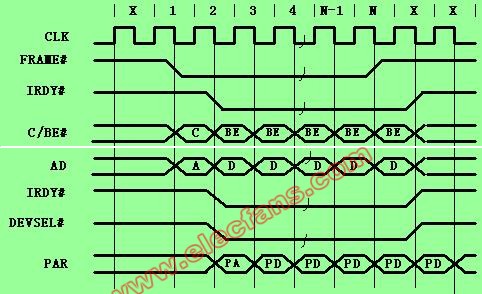

就可使用,大大降低了板卡升級(jí)的時(shí)間周期和開發(fā)難度,具有較高的實(shí)用價(jià)值和推廣價(jià)值。2 PCI總線的特點(diǎn)PCI是先進(jìn)的高性能局部總線,可同時(shí)支持多組外圍設(shè)備。其特點(diǎn)是:總線操作與處理器一存儲(chǔ)器子系統(tǒng)操作

2019-04-29 07:00:09

目前基于PCI總線的高速數(shù)據(jù)采集系統(tǒng),大多采用高速A/D,CPLD或FPGA,FIFO或雙端口RAM以及通用PCI接口來(lái)設(shè)計(jì),其通用性、靈活性差,不能很好地發(fā)揮PCI總線的性能。針對(duì)這些不足,在分析

2009-03-16 18:02:05 10

10 本文主要講述的是CIF50-PB總線板卡與力控組態(tài)軟件的應(yīng)用實(shí)例。

2009-04-09 16:56:57 32

32 用ALTERA 公司MAX7000 系列CPLD 芯片實(shí)現(xiàn)單片機(jī)與PC104 ISA 總線接口之間的并行通信,給出系統(tǒng)設(shè)計(jì)方法及程序源代碼。包括通信軟件和AHDL 設(shè)計(jì)部分。

2009-04-14 17:36:07 29

29 用ALTERA 公司MAX7000 系列CPLD 芯片實(shí)現(xiàn)單片機(jī)與PC104 ISA 總線接口之間的并行通信,給出系統(tǒng)設(shè)計(jì)方法及程序源代碼。包括通信軟件和AHDL 設(shè)計(jì)部分。

2009-05-14 13:24:39 14

14 采用可編程邏輯器件CPLD,分四個(gè)模塊——控制寄存器模塊、PCI控制器狀態(tài)機(jī)模塊、SRAM 控制器模塊和仲裁器模塊,分別完成通信并解析PCI總線、PCI狀態(tài)的控制和翻轉(zhuǎn)、負(fù)責(zé)SRAM接口數(shù)

2009-06-01 14:25:22 16

16 基于FPGA的PCI總線接口設(shè)計(jì)::PCI是一種高性能的局部總線規(guī)范,可實(shí)現(xiàn)各種功能標(biāo)準(zhǔn)的PCI總線卡。本文簡(jiǎn)要介紹了PCI總線的特點(diǎn)、信號(hào)與命令,提出了一種利用高速FPGA實(shí)現(xiàn)PCI總線接

2009-06-25 08:17:18 48

48 介紹了采用CPLD 實(shí)現(xiàn)DSP 芯片TMS320C6713 和背板VME 總線之間高速數(shù)據(jù)傳輸?shù)南到y(tǒng)設(shè)計(jì)方法。設(shè)計(jì)中采用VHDL 語(yǔ)言對(duì)CPLD 進(jìn)行編程。同時(shí)由于CPLD 的現(xiàn)場(chǎng)可編程特性,增強(qiáng)了整個(gè)系統(tǒng)

2009-08-15 08:39:23 51

51 本文簡(jiǎn)要介紹了PCI 總線的仲裁機(jī)制, 完成了PCI 總線仲裁器核心的設(shè)計(jì)、實(shí)現(xiàn)。通過(guò)ModelSim 進(jìn)行了軟件仿真,最后在XILINX 公司的FPGA 上加以了驗(yàn)證。

2009-09-03 08:18:29 27

27 PCI,PCI-E,CPCI,PC104 板卡說(shuō)明書:CPCI:全稱:CompactPCI,1997 年8月,PICMG發(fā)布了第一個(gè)CompactPCI技術(shù)標(biāo)準(zhǔn)PICMG 2.0 Rev. 1.0

2009-09-29 10:43:48 189

189 由高速圖像采集子系統(tǒng)和GPS 精密授時(shí)子系統(tǒng)構(gòu)成,為圖像采集提供精確的時(shí)間基準(zhǔn)。設(shè)計(jì)并實(shí)現(xiàn)了基于PCI 總線的GPS 時(shí)間獲取板卡,并完成了一系列軟件的設(shè)計(jì)開發(fā)。首先通過(guò)CPLD

2009-12-19 14:01:07 21

21 本文重點(diǎn)分析了PCI 總線設(shè)備控制器的設(shè)計(jì)方案。以PCI 總線協(xié)議的分析和理解為基礎(chǔ),對(duì)PCI 總線設(shè)備控制器進(jìn)行了功能分析和結(jié)構(gòu)劃分,對(duì)PCI 總線從設(shè)備控制器的設(shè)計(jì)思路和各個(gè)

2010-01-13 16:57:37 49

49 PCI總線協(xié)議的FPGA實(shí)現(xiàn)及驅(qū)動(dòng)設(shè)計(jì)

摘要! 采用FPGA技術(shù)! 在公司的flex6000系列芯片上實(shí)現(xiàn)了從設(shè)備模式pci總線的簡(jiǎn)化協(xié)議!并給出了WIndowsx 系統(tǒng)下的虛擬設(shè)備驅(qū)動(dòng)程序

2010-03-12 14:30:27 36

36 摘 要: 本文采用Altera的CPLD實(shí)現(xiàn)了PCI總線至UTOPIA接口的邏輯轉(zhuǎn)換控制,為低成本實(shí)現(xiàn)ATM終端奠定了基礎(chǔ)。

2006-03-11 13:16:50 864

864

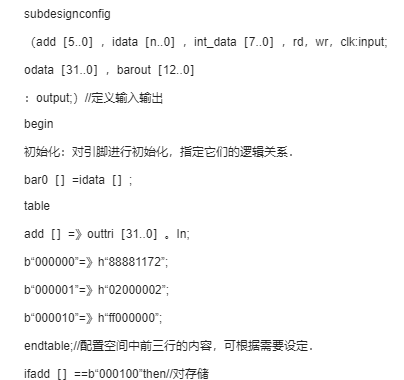

摘要:用ALTERA公司MAX7000系列CPLD芯片實(shí)現(xiàn)單片機(jī)與PC104 ISA總線接口之間的并行通信,給出系統(tǒng)設(shè)計(jì)方法及程序源代碼。包括通信軟件和AHDL設(shè)計(jì)部分。CPLD(Complex Programmable Logi

2006-05-26 21:52:11 872

872

PCI總線原理

PCI總線的特點(diǎn):數(shù)據(jù)總線32位,可擴(kuò)充到64位。可進(jìn)行突發(fā)(burst)式傳輸。總線操作與處

2008-12-09 11:30:05 13510

13510

一種基于PCI總線和DSP技術(shù)的虛擬儀器設(shè)計(jì)

傳統(tǒng)的虛擬儀器由一塊基于PCI總線的直接利用A/D和D/A芯片構(gòu)成的數(shù)據(jù)采集板卡和相應(yīng)的軟件組成,但隨著計(jì)算機(jī)網(wǎng)

2009-04-22 17:44:37 651

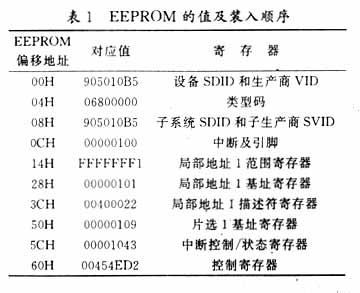

651 PCI9052總線接口芯片及其ISA模式應(yīng)用

PCI9052是PLX公司開發(fā)的服從PCI協(xié)議的從模式接口芯片,它能夠實(shí)現(xiàn)ISA總線到PCI總線的平滑轉(zhuǎn)換。主要闡述了PCI9052

2009-05-04 21:48:45 1563

1563

【摘 要】 通過(guò)設(shè)計(jì)實(shí)例詳細(xì)介紹了用VHDL(VHSIC Hardware DescriptionLanguage)語(yǔ)言開發(fā)FPGA/CPLD的方法,以及與電路圖輸入和其它HDL語(yǔ)言相比,使用VHDL語(yǔ)言的優(yōu)越性。

2009-05-10 19:47:30 1111

1111

AMCCS5933 在PCI板卡設(shè)計(jì)中的應(yīng)用

PCI總線是計(jì)算機(jī)主機(jī)中最常見的總線。它是一種高性能的32/64位地址數(shù)據(jù)復(fù)用總線,支持猝發(fā)傳輸,傳輸峰值速率可達(dá)528MB/s,而且還支持

2009-05-14 12:46:37 2231

2231

摘 要:通過(guò)設(shè)計(jì)實(shí)例詳細(xì)介紹了用Verilog HDL語(yǔ)言開發(fā)FPGA/CPLD的方法,并通過(guò)與其他各種輸入方式的比較,顯示出使用Verilog HDL語(yǔ)言的優(yōu)越性。

2009-06-20 11:51:28 1857

1857

摘 要 :PCI是一種高性能的局部總線規(guī)范,可實(shí)現(xiàn)各種功能標(biāo)準(zhǔn)的PCI總線卡。本文簡(jiǎn)要介紹了PCI總線的特點(diǎn)、信號(hào)與命令,提出了一種利用高速FPGA實(shí)現(xiàn)PCI總線接口的

2009-06-20 13:13:28 936

936

摘要:詳細(xì)闡述一種利用CPLD實(shí)現(xiàn)的8位單片機(jī)與PCI設(shè)備間的通信接口方案,給出用ABEL HDL編寫的主要源程序。該方案在實(shí)踐中檢驗(yàn)通過(guò)。

關(guān)鍵詞:?jiǎn)纹瑱C(jī) CPLD PCI

8位單片

2009-06-20 13:31:29 869

869

摘 要: 以自行研制開發(fā)的PCI高速總線背板為背景,系統(tǒng)地論述了PCI總線的仲裁機(jī)制、總線的缺省占用、仲裁信號(hào)協(xié)定及優(yōu)先級(jí)仲裁算法,給出了采用EPLD實(shí)現(xiàn)仲裁器功能的編程設(shè)計(jì)

2009-06-20 13:32:20 961

961

摘要:用ALTERA公司MAX7000系列CPLD芯片實(shí)現(xiàn)單片機(jī)與PC104 ISA總線接口之間的并行通信,給出系統(tǒng)設(shè)計(jì)方法及程序源代碼。包括通信軟件和AHDL設(shè)計(jì)部分。

關(guān)鍵詞:CPLD

2009-06-20 13:34:28 1116

1116

基于CPLD的單片機(jī)與PCI接口設(shè)計(jì)解決方案

8位單片機(jī)在嵌入式系統(tǒng)中應(yīng)用廣泛,然而讓它直接與PCI總線設(shè)備打交道卻有其固有缺陷。8位單片機(jī)只有16位

2009-09-26 17:41:20 825

825

PCI Express總線技術(shù)白皮書

1.1 PCI Express總線的起源和現(xiàn)狀 2001年春季的IDF上Intel正式公布PCI Express,是取代PCI總線的第三代IO技術(shù),也稱為

2009-10-04 09:39:14 1031

1031

基于PCI總線的CAN卡的設(shè)計(jì)與實(shí)現(xiàn)

現(xiàn)場(chǎng)總線CAN(Controller Area Network控制器局域網(wǎng)絡(luò))以其高性能、高可靠性及獨(dú)特的設(shè)計(jì),越來(lái)越受到人們的重視和青睞,

2009-10-25 10:54:58 817

817

PCI總線的熱插拔技術(shù)及實(shí)現(xiàn)

摘要:具有熱插拔PCI槽現(xiàn)已成為許多需要長(zhǎng)時(shí)間不間斷工作和能夠在線維修的計(jì)算機(jī)系統(tǒng)的必備功能。文中介紹了

2010-03-03 19:27:08 1871

1871

提出了一種使用CPLD解決雙端口RAM地址譯碼和PCI接口芯片局部總線仲裁的的硬件設(shè)計(jì)方案,并給出了PCI總線接口芯片

2011-01-07 12:13:03 1891

1891

基于CPLD的PWM控制器電路結(jié)構(gòu)簡(jiǎn)單,設(shè)計(jì)方便,簡(jiǎn)化了外部線路設(shè)計(jì),節(jié)省了PCB板空間,解決了機(jī)電一體化開發(fā)平臺(tái)中MCU模塊與功率模塊基于PCI總線的通信

2011-05-24 10:26:47 869

869

詳細(xì)分析了 PCI 總線 的特點(diǎn),介紹了PCI 接口的一些開發(fā)工具和開發(fā)技巧,包括專用接口芯片、驅(qū)動(dòng)程序開發(fā)軟件包和PCI 板卡設(shè)計(jì)的要點(diǎn),并對(duì)PCI 接口芯片S5933 和驅(qū)動(dòng)程序開發(fā)軟件包WinDri

2011-06-17 17:06:31 19

19 本文首先介紹了多DSP共享總線的通用信號(hào)處理板卡的硬件結(jié)構(gòu),介紹了基于PCI9054的CPCI總線接口設(shè)計(jì)和FPGA控制的通用信號(hào)處理板的板間通信過(guò)程。深入討論了基于Windows2000系統(tǒng)的WDM驅(qū)動(dòng)

2011-09-09 11:51:25 72

72 在高性能的服務(wù)器系統(tǒng)、實(shí)時(shí)的嵌入式系統(tǒng)等RAs特性要求較高的系統(tǒng)中,需要設(shè)計(jì)開發(fā)基于第三代PcIExpre鷂總線背板的高速數(shù)字電路板卡,并且這些板卡需要支持熱插拔功能。基于PcI

2011-09-21 11:40:04 35

35 出了一種PCI總線從設(shè)備的CPLD實(shí)現(xiàn)方法。該方法遵從PCI規(guī)范2.2版,實(shí)現(xiàn)了資源自動(dòng)配置并且支持?jǐn)?shù)據(jù)突發(fā)傳輸。試驗(yàn)證明該方法的有效性,其突發(fā)傳輸速率可達(dá)20 MBs -1 。

2011-11-30 17:06:11 60

60 文中介紹了基于BU-61580設(shè)計(jì)的1553B總線板卡,擴(kuò)展性強(qiáng)、功能強(qiáng)大,可廣泛應(yīng)用于航空、通信等領(lǐng)域。

2011-12-14 14:48:14 120

120 本文將對(duì)PLX公司的PCI9052總線目標(biāo)接口芯片的功能及其在PCI板卡設(shè)計(jì)中的應(yīng)用進(jìn)行介紹,PCI9052是PLX公司繼PCI9050之后新推出的、可用于低成本適配器的總線目標(biāo)接口芯片。

2011-12-29 09:42:51 3083

3083

文中主要介紹了采用CPLD實(shí)現(xiàn)32 bit 33 MHzPCI從設(shè)備接口的設(shè)計(jì)方法,該從設(shè)備接口模塊遵從PCI規(guī)范2.2版,實(shí)現(xiàn)了資源的自動(dòng)配置,支持突發(fā)傳輸,并為用戶提供了一個(gè)簡(jiǎn)單的接口。設(shè)計(jì)完成

2012-08-06 15:18:22 1788

1788

【LabVIEW從入門到精通】6.4.2.1 PCI1710HG板卡安裝

2016-01-08 15:49:49 0

0 NI PCI6023E板卡【labview板卡】

2016-01-11 17:54:44 0

0 AHDL語(yǔ)言在MAXPLUS軟件的使用案例,好東西,喜歡的朋友可以下載來(lái)學(xué)習(xí)。

2016-02-19 17:03:04 0

0 基于CPLD的SGPIO總線實(shí)現(xiàn)及應(yīng)用

2017-01-24 16:00:51 75

75 本文的主要內(nèi)容介紹的是如何使用C語(yǔ)言和定時(shí)器連接MSP430MCU和兼容UNIO總線的串行EEPROM。

2018-04-27 16:23:19 8

8 PLD(可編程邏輯器件)以其操作靈活、使用方便、開發(fā)迅速、投資風(fēng)險(xiǎn)低的特點(diǎn),很快發(fā)展起來(lái),并越來(lái)越受人們的矚目。PLD是可以由用戶在工作現(xiàn)場(chǎng)編程的邏輯器件,它從簡(jiǎn)單的PAL、GAL,已發(fā)展到CPLD、EPLD、FPGA和FLEX系列。他們都具有體系結(jié)構(gòu)和邏輯單元靈活、集成度高以及適用范圍廣等特點(diǎn)。

2019-08-16 08:00:00 2011

2011

本文檔詳細(xì)介紹的是FPGA教程之AHDL硬件描述語(yǔ)言的詳細(xì)資料說(shuō)明主要內(nèi)容包括了:1 硬件描述語(yǔ)言(HDL)概述,2 Altera 的硬件描述語(yǔ)言AHDL,3 AHDL電路設(shè)計(jì)舉例

2019-02-27 17:27:56 16

16 實(shí)現(xiàn)PCI總線協(xié)議目前主要有專用接口芯片和CPLD實(shí)現(xiàn)兩種方式。專用接口芯片使用簡(jiǎn)單方便、工作穩(wěn)定可靠,但往往具體應(yīng)用中只用到部分功能,并且需要可編程邏輯配合使用,這樣不僅浪費(fèi)專用芯片的資源,而且

2020-03-20 09:54:04 1268

1268

系統(tǒng)中ADC板卡,DSP板卡以及其他 功能模塊之間的數(shù)據(jù)傳輸和控制通道,ADC板卡采集到的數(shù)據(jù)通過(guò)PCI總線主控模式高速傳輸?shù)紻SP板卡中進(jìn)行數(shù)字信號(hào)處理,實(shí)現(xiàn)接收機(jī)功能。結(jié)果表明, 該系統(tǒng)具有結(jié)構(gòu)簡(jiǎn)單,精度高等優(yōu)點(diǎn),并充分體現(xiàn)軟件無(wú)線電的靈

2020-11-19 17:48:01 13

13 VB語(yǔ)言和C++語(yǔ)言是兩種不同的編程語(yǔ)言,雖然它們都屬于高級(jí)編程語(yǔ)言,但在設(shè)計(jì)和用途上有很多區(qū)別。下面將詳細(xì)比較VB語(yǔ)言和C++語(yǔ)言的區(qū)別。 設(shè)計(jì)目標(biāo): VB語(yǔ)言(Visual Basic

2024-02-01 10:20:07 382

382

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論