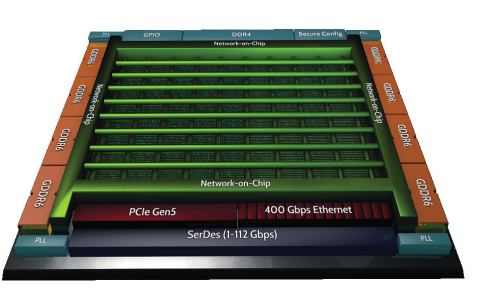

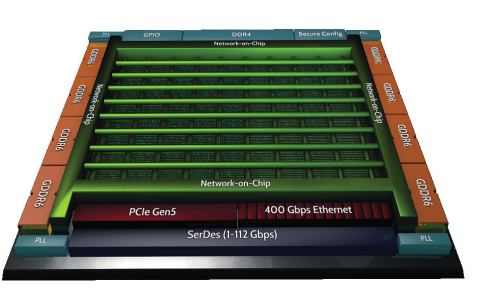

Achronix 最新基于臺積電(TSMC)的7nm FinFET工藝的Speedster7t FPGA器件包含了革命性的新型二維片上網絡(2D NoC)。

2020-02-27 17:08:41 1774

1774 Achronix 在其最新基于臺積電(TSMC)7nm FinFET工藝的Speedster7t FPGA器件中包含了革命性的創(chuàng)新型二維片上網絡(2D NoC)。

2020-08-21 14:44:57 696

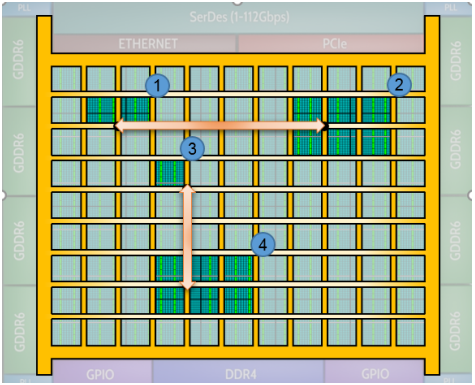

696 Speedster7t架構中的2D NoC提供了從邏輯陣列的可編程邏輯到位于I/O環(huán)中的高速接口子系統(tǒng)的高帶寬連接,用于連接到片外資源。

2021-07-07 16:31:31 1863

1863

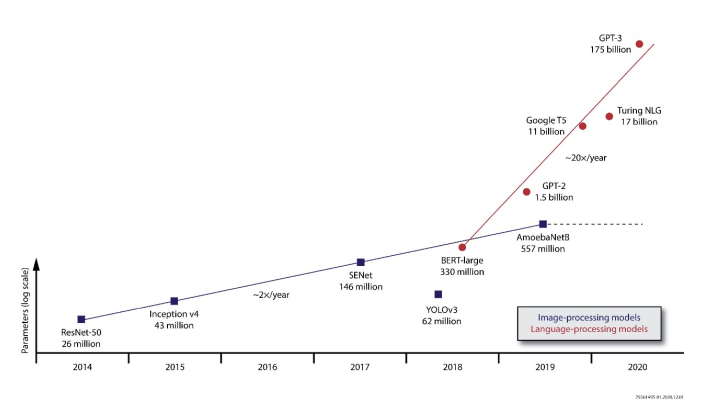

創(chuàng)新的二維片上網絡(2D NoC)來處理這些高帶寬數(shù)據流。Achronix的FPGA中特有的2D NoC實現(xiàn)是一種創(chuàng)新,它與用可編程邏輯資源來實現(xiàn)2D?NoC的傳統(tǒng)方法相比,有哪些創(chuàng)新和價值呢?本白皮書討論了這兩種實現(xiàn)2D NoC的方法,并提供了一個示例設計,以展示與軟2D NoC實現(xiàn)相比,

2022-04-21 18:02:56 5750

5750

只有在腦海中建立了一個個邏輯模型,理解FPGA內部邏輯結構實現(xiàn)的基礎,才能明白為什么寫Verilog和寫C整體思路是不一樣的,才能理解順序執(zhí)行語言和并行執(zhí)行語言的設計方法上的差異。在看到一段簡單程序的時候應該想到是什么樣的功能電路。

2022-08-25 11:12:00 739

739 2D NoC如同在FPGA可編程邏輯結構上運行的高速公路網絡一樣,為FPGA外部高速接口和內部可編程邏輯的數(shù)據傳輸提供了超高帶寬。

2021-11-11 14:20:14 2760

2760

背光區(qū)域調節(jié)技術2D區(qū)域調光的優(yōu)點2D區(qū)域調光面臨的難題及機遇

2021-02-26 08:21:12

FPGA 內部詳細架構FPGA 芯片整體架構1.可編程輸入輸出單元(IOB)(Input Output Block)2.可配置邏輯塊(CLB)(Configurable Logic Block)3.

2021-07-30 08:10:06

可重構設計是指利用可重用的軟、硬件資源,根據不同的應用需求,靈活地改變自身體系結構的設計方法。FPGA器件可多次重復配置邏輯的特性使可重構系統(tǒng)成為可能,使系統(tǒng)兼具靈活、便捷、硬件資源可復用等性能

2011-05-27 10:22:36

FPGA(Field-Programmable Gate Array,現(xiàn)場可編程門陣列)是一種特殊的集成電路,其內部結構由大量的可配置邏輯塊和互連線組成。FPGA可以通過編程來實現(xiàn)各種數(shù)字系統(tǒng)功能

2024-01-26 10:03:55

,它是在PAL、GAL、CPLD等可編程器件的基礎上進一步發(fā)展的產物。內部基本結構為門陣列構成靜態(tài)存儲器(SRAM)。該SRAM可構成函數(shù)發(fā)生器,即查找表(LUT),通過查找表可實現(xiàn)邏輯函數(shù)功能

2020-08-28 15:41:47

的相互連接。實際情況還真不是這么簡單,FPGA/CPLD里面其實也找不著多少個與門、或門、非門。那么FPGA/CPLD器件內部到底以怎樣的方式來實現(xiàn)我們需要的邏輯電路呢?下面我們就通過剖析MAX II

2015-01-27 11:43:10

。(特權同學版權所有)我們都知道,硬件有著與生俱來的并行特點,它不同于軟件編程的順序特性。在FPGA器件內部,所有的硬件邏輯都可以同時工作運行,正是這樣,很多需要多條軟件程序指令實現(xiàn)的功能,用硬件邏輯

2015-03-26 11:00:19

NoC是什么?NoC有哪些技術優(yōu)勢?NoC有哪些關鍵技術難點?

2021-06-04 06:34:33

NoC在高端FPGA的應用是什么?NoC給Speedster 7t FPGA帶來的優(yōu)勢有哪些?

2021-06-17 11:12:26

fpga通過什么實現(xiàn)邏輯功能,以超級馬里奧為例子講述FPGA有些制作。1、FPGA游戲目標沒有CPU,單純用 FPGA 的verilog硬件語言來實現(xiàn)一個游戲,而這個游戲還得符合老師要求,由于沒有

2021-07-22 07:07:25

在超高速數(shù)據采集方面,FPGA(現(xiàn)場可編程門陣列)有著單片機和DSP所無法比擬的優(yōu)勢。FPGA時鐘頻率高,內部時延小,目前器件的最高工作頻率可達300MHz;硬件資源豐富,單片集成的可用門數(shù)達1000萬門;全部控制邏輯由硬件資源完成,速度快,效率高;組成形式靈活,可以集成外圍控制、譯碼和接口電路。

2019-08-02 06:51:33

Ansoft Maxwell 2D瞬態(tài)場在電機性能參數(shù)計算的應用通過使用Ansoft Maxwell 2D瞬態(tài)電磁場計算軟件,對正弦波永磁伺服電機的空載感應電動勢和轉矩常數(shù)做了仿真計算。通過和實測值比較,軟件的計算是準確的,空載感應電動勢波形和數(shù)值準確計算也為永磁伺服電機的優(yōu)化設計提供了依據。.

2016-01-27 16:55:23

Ansys Maxwell 3D 2D RMxprt v16.0 Win32-U\RMxprt 軟件可提高旋轉電機的設計和優(yōu)化速度。用戶通過軟件可以很簡單地利用電機參數(shù)及模板驅動型用戶界面對電機建模

2014-06-13 17:09:22

用戶根據需要生成特定的電路結構,完成一定的功能。由于 CPLD內部采用固定長度的金屬線進行各邏輯塊的互連,所以設計的邏輯電路具有時間可預測性,避免了分段式互連結構時序不完全預測的缺點。到90年代

2009-09-29 09:38:32

根本無法打開它們。錯誤消息是我的顯卡不支持webgl。問題:由于這是一張舊卡,有沒有更新的顯卡我可以替換它?我確實將我和我的女朋友進行了比較,并注意到我的不支持2D和3D,而她的確如此,她對游戲沒有

2018-11-21 11:47:16

最新教程下載:本章教程為大家講解LTDC應用中最基本的漢字顯示和2D圖形顯示功能實現(xiàn)。 初學者重要提示 LCD相關的基礎支持 LCD硬件設計 LCD驅動設計 LCD板級支持包(和) LCD的驅動移植

2021-12-13 07:29:15

第41章 STM32F429的LTDC應用之LCD漢字顯示和2D圖形顯示本章教程為大家講解LTDC應用中最基本的漢字顯示和2D圖形顯示功能實現(xiàn)。目錄第41章 STM32F429的LTDC應用之LCD

2021-08-10 07:24:07

PADS 2D網格這個怎么做急!!!

2016-10-06 20:03:34

大家好!我想將Pandaboard與FPGA互連。在互聯(lián)網上搜索我發(fā)現(xiàn)可以使用GPMC互連它們,但遺憾的是我沒有找到任何關于USB的信息。我的問題是:是否可以通過USB互連兩塊板?如果是的話,必須執(zhí)行哪些操作才能連接這兩個板,以便它們能夠彼此“交談”?預先感謝。利瑪竇。

2019-09-04 09:39:40

第51章 STM32H7的LTDC應用之LCD漢字顯示和2D圖形顯示本章教程為大家講解LTDC應用中最基本的漢字顯示和2D圖形顯示功能實現(xiàn)。51.1 初學者重要提示51.2 LCD相關的基礎支持51.3 LCD硬件設計51.4 ...

2021-08-03 06:40:36

`上個月拿到了STM32+LT768的開發(fā)板+LCD顯示屏,學會了用stm32驅動lt768實現(xiàn)2d圖形加速和硬件圖形加速,用來顯示圖形或者圖片很方便,推薦給大家。下面放上LT768的一些特色功能

2018-04-02 00:09:17

,可以改變上、下拉電阻。目前,I/O 口的頻率也越來越高,一些高端的FPGA 通過DDR 寄存器技術可以支持高達2Gbps 的數(shù)據速率。外部輸入信號可以通過 IOB 模塊的存儲單元輸入到FPGA 的內部

2012-03-08 11:03:49

連接到I/O模塊。FPGA的邏輯是通過向內部靜態(tài)存儲單元加載編程數(shù)據來實現(xiàn)的,存儲在存儲器單元中的值決定了邏輯單元的邏輯功能以及各模塊之間或模塊與I/O間的聯(lián)接方式,并最終決定了FPGA所能實現(xiàn)的功能

2019-08-11 04:30:00

AD17.1.5軟件,3D與2D模型不能相互轉換,按3可以進入3D模型,按2不可以進入2D模型,這個是怎么回事啊?

2019-09-20 05:35:16

互連 等。1)自由空間光互連技術通過在自由空間中傳播的光束進行數(shù)據傳輸,適用于芯片之間或電路板之間這個層次上的連接,可以使互連密度接近光的衍射極限,不存在信道對帶寬的限制,易于實現(xiàn)重構互連。該項技術

2016-01-29 09:17:10

器件中的重要創(chuàng)新之一,2D NoC?為 FPGA 設計提供了幾項重要優(yōu)勢,包括:· 提高設計的性能,讓 FPGA 內部的數(shù)據傳輸不再成為瓶頸。· 節(jié)省 FPGA 可編程邏輯資源,簡化邏輯設計,由

2020-09-07 15:25:33

事件被捕獲使用硬件UART克服軟件實現(xiàn)的性能限制LCMXO2-640HC-4TG100C可編程邏輯器件FPGA芯片通過硬件性能加速提升系統(tǒng)性能基于邏輯的信號過濾降低了處理器負荷以最小的處理器開銷實現(xiàn)

2019-09-20 15:13:30

你好,我正在使用帶有AD6676-EBZ高速adc的定制FPGA平臺。該邏輯包含JESD24B IP。我想將VIO范圍用于眼圖。但我真的不明白它是如何運作的。我發(fā)現(xiàn)2D眼睛掃描邏輯提供了通過axi4

2020-07-30 10:24:35

摘要:RS 232接口是現(xiàn)在最常用的一種通信接口。隨著FPGA技術的高速發(fā)展,一些常見的接口電路的時序電路可以通過FPGA實現(xiàn),通過這種設計可減少電路系統(tǒng)元件的數(shù)量,提高系統(tǒng)集成度和可靠性。詳細闡述

2019-06-19 07:42:37

是處理數(shù)字信號如圖形、語音及圖像等領域的重要變換工具。快速傅里葉變換(FFT)是DFT的快速算法。FFT算法的硬件實現(xiàn)一般有3種形式:1)使用通用DSP來實現(xiàn);2)用專用DSP來實現(xiàn);3)通過FPGA來

2009-06-14 00:19:55

機載視頻圖形顯示系統(tǒng)主要實現(xiàn)2D圖形的繪制,構成各種飛行參數(shù)畫面,同時疊加實時的外景視頻。由于FPGA具有強大邏輯資源、豐富IP核等優(yōu)點,基于FPGA的嵌入式系統(tǒng)架構是機載視頻圖形顯示系統(tǒng)理想的架構

2019-06-24 06:07:53

vrfSubject:[vrf] Array2D二維數(shù)組問題:1。如何在聲明后使用設置變量初始化它?.2。如何將2D數(shù)組饋送到記錄?3。如何從Record和DataSet中提取相同的2D數(shù)組?提前謝謝

2019-10-29 12:41:09

邏輯結構之上運行的高速公路網絡一樣,為FPGA外部高速接口和內部可編程邏輯的數(shù)據傳輸提供了大約高達27Tbps的超高帶寬。作為Speedster7t FPGA器件中的重要創(chuàng)新之一,2D NoC為FPGA

2020-10-20 09:54:00

NoC為FPGA設計提供了哪些優(yōu)勢?NoC在FPGA內部邏輯互連中發(fā)揮的作用是什么?如何利用片上高速網絡創(chuàng)新地實現(xiàn)FPGA內部超高帶寬邏輯互連?

2021-06-17 11:35:28

前言FPGA 可以實現(xiàn)高速硬件電路,如各種時鐘,PWM,高速接口,DSP計算等硬件功能。這是Cortex-M 處理器軟件無法比擬的。要實現(xiàn)FPGA 的邏輯設計,對于嵌入式系統(tǒng)工程師又是比較復雜和具有

2021-12-21 06:13:49

如何同時獲取2d圖像序列和相應的3d點云?以上來自于谷歌翻譯以下為原文How to obtain the sequence of 2d image and corresponding 3d point cloud at the same time?

2018-11-13 11:25:01

請問PCB 中2D 庫中怎么導出3D

2019-09-11 22:17:15

如何在MA35D1上使用硬件 2D 加速功能?

2023-09-06 08:26:00

推動FPGA調試技術改變的原因是什么外部邏輯分析儀受到的限制是什么如何用內部邏輯分析儀調試FPGA

2021-04-30 06:44:08

本文檔的主要內容詳細介紹的是小米的2D激光雷達拆解圖和講解。

2023-09-22 08:07:45

本文提出的通過微處理器加FPGA結合串行菊花鏈實現(xiàn)可重構的方式,實現(xiàn)了動態(tài)可重構FPGA結構設計的一種應用。

2021-05-10 06:22:19

ucgui中怎么跟新對話框里面2D圖形的啊 我用2D圖形畫了一個溫度計,怎么更新呢?

2019-08-21 03:18:09

并運行良好,直到調用。這個函數(shù)在主函數(shù)中遇到。在我的項目中,有必要使用2D數(shù)組,在需要時通過&返回它們,并且我有幾個函數(shù),如上面執(zhí)行不同任務的函數(shù),那么有沒有有效的方法可以傳遞2D數(shù)組并返回它們?謝謝你的回復。

2019-09-06 17:07:48

并運行良好,直到調用。這個函數(shù)在主函數(shù)中遇到。在我的項目中,有必要使用2D數(shù)組,在需要時通過&返回它們,并且我有幾個函數(shù),如上面執(zhí)行不同任務的函數(shù),那么有沒有有效的方法可以傳遞2D數(shù)組并返回它們?謝謝你的回復。

2019-10-09 14:17:30

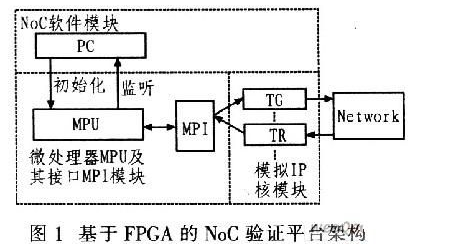

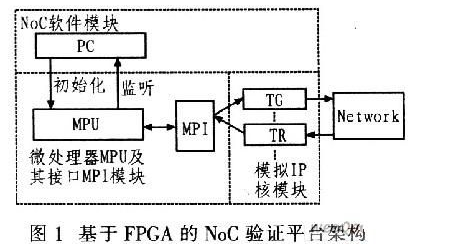

本文提出了一種基于FPGA的NoC驗證平臺。詳細討論了該驗證平臺中FPGA硬件平臺和NoC軟件的基本功能,并闡述了TG/R,MPU,MPI以及NoC軟件的可重用性等特點。通過一個實例仿真驗證的結果說明了該驗證平臺的基本功能和優(yōu)越性。

2021-05-06 07:20:48

個宏單元。一個單獨的宏單元由幾個 AND 門、一個 d 觸發(fā)器、一個多路復用器和一個 EX-OR 門組成。它們通過一個叫做可編程互連的塊連接起來。FPGA 的主要元素是查找表(LUT)。在

2022-04-03 11:20:18

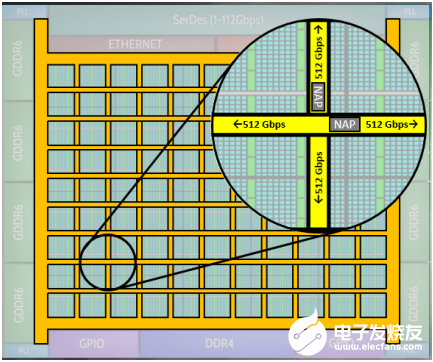

288bit的原始數(shù)據模式(Raw data mode)。 用戶可以通過這288bit的信號進行邏輯直連或者自定義協(xié)議互連。圖3利用2D NoC進行內部邏輯互連在NoC的每個交叉點上都有兩個網絡接入點

2020-05-12 08:00:00

的讀寫效率最后,我們測試一下7t1500上GDDR6控制器的讀寫效率,所有的測試結果基于仿真數(shù)據。因為7t1500包含了片上網絡(NoC),并且NoC已經實現(xiàn)了仲裁,時鐘域轉換的邏輯,我們用三個用戶邏輯

2021-12-22 08:00:00

請問這樣的2D數(shù)組怎么創(chuàng)建代表什么意思

2019-09-02 15:51:55

,如果大家想在對話框上面繪制2D圖形的話,可以將STemWin的2D繪制函數(shù)放在對話框回調函數(shù)中的WM_PAINT消息中實現(xiàn)。 這里跟大家講一下如何利用uCGUIBulder4.0在對話框上面繪制簡單的橫線和豎線。60.1.1 第一步:建立如下界面

2016-10-18 11:33:49

我理解的比較簡單。將代碼燒寫進FPGA,芯片內部的各個邏輯門通過邏輯連線實現(xiàn)邏輯功能,這些邏輯門的輸入是通過查找表獲得的。比如我用到兩個與門和一個或門,對于4輸入的LUT來講,則至少需要兩個LUT。

不知道這樣理解對不對。

還有具體LUT內部是如何實現(xiàn)查找的,請知明人能夠提點提點。

謝謝

2023-04-23 14:12:58

請問怎么將AD中的3D封裝庫轉換為2D的封裝庫

2019-06-05 00:35:07

調試FPGA時,TD軟件是否支持內部邏輯分析(抓波形)功能?

2023-08-11 10:32:27

使用、“開箱即用”而無需進行代碼開發(fā)的體驗。用戶可通過Aurea 2.0這款免費下載的圖形用戶界面(GUI)軟件完成參數(shù)化、診斷和可選設置。 2D/3D觸摸與手勢開發(fā)工具包配備了Microchip

2018-11-07 10:45:56

《Fundamentals of Computer Graphics》翻譯(三):隱式2D直線

2019-09-03 12:19:29

Xilinx?7系列FPGA由四個FPGA系列組成,可滿足各種系統(tǒng)要求,從低成本、小尺寸、成本敏感的高容量應用到超高端連接帶寬、邏輯容量和信號處理能力,以滿足最苛刻的高性能應用

2022-08-30 17:04:09

介紹了頻域抽取基二快速傅里葉運算的基本原理;討論了基于FPGA達4 096點的大點數(shù)超高速FFT硬件系統(tǒng)設計與實現(xiàn)方法,當多組大點數(shù)進行FFT運算時,利用FPGA內部大容量存儲資源,采

2009-04-26 18:33:08 26

26 技術相結合,可以實現(xiàn)2.5D和3D的復合測量。 CHT/CHS/CHX系列2d光學影像測量儀功能強大,可實現(xiàn)各種復雜零件的表面尺寸、輪廓、角

2022-09-08 11:27:18

Xilinx?7系列FPGA包括四個FPGA系列,可滿足整個系統(tǒng)要求,包括低成本,小尺寸,成本敏感的大批量應用程序,可滿足最苛刻的超高端連接帶寬,邏輯容量和信號處理能力高性能的應用程序。7系列

2022-11-10 15:11:11

片上網絡(Network-on-Chip, NoC)以網絡互連結構代替?zhèn)鹘y(tǒng)總線結構,很好地解決了片上高性能計算資源之間的通信瓶頸問題。路由器是實現(xiàn)NoC 的重要基礎部件,本文在分析國內外相關

2009-12-14 09:37:38 34

34 比較了多種DSP芯片的互連性能,給出了一種簡單高性能DSP網絡結構。針對構成DSP網絡通訊接口的鏈路口,分析其基本特點,并且提出了在FPGA中實現(xiàn)的設計原理。最后給出了設計仿真圖和

2010-07-27 16:46:46 22

22 隨著FPGA設計復雜度的增加,傳統(tǒng)測試方法受到限制。在高速集成FPGA測試中,其內部信號的實時獲取和分析比較困難。介紹了Quartus II中SingalTap II嵌入式邏輯分析器的使用,并給出一個

2010-12-17 15:25:17 16

16 針對基于軟件仿真片上網絡NoC(Network on Chip)效率低的問題,提出基于FPGA的NoC驗證平臺構建方案。該平臺集成可重用的流量產生器TG(Traffic Generation),流量接收器TR(Traffic Receiver)

2011-01-04 16:24:38 12

12 基于漢明碼的糾錯原理.根據對64位數(shù)據進行檢糾錯處理的需要,設計一個利用8位校驗碼,以實現(xiàn)該功能的算法邏輯,并通過FPGA實現(xiàn)。

2011-09-15 15:14:58 1382

1382

為了能夠靈活地驗證和實現(xiàn)自主設計的基于NoC的多核處理器,縮短NoC多核處理器的設計周期,提出了設計集成4片Virtex-6—550T FPGA的NoC多核處理器原型芯片設計/驗證平臺。分析和評估

2017-11-22 09:15:01 4137

4137 。今天,英特爾披露了有關如何通過 EMIB 幫助全新 Stratix 10 MX FPGA(現(xiàn)場可編程邏輯門陣列)家族芯片實現(xiàn)帶寬大漲的部分細節(jié)。

2017-12-20 12:51:10 6378

6378 本文提出的基于FPGA的NoC驗證平臺在仿真速度方面是一般基于HDL的軟件仿真的16 000倍,而基于PC機編寫的NoC軟件更增強了該平臺的靈活性和實用性。

2019-04-13 11:33:47 2053

2053

了革命性的新型二維片上網絡(2D NoC)。2D NoC如同在FPGA可編程邏輯結構上運行的高速公路網絡一樣,為FPGA外部高速接口和內部可編程邏輯的數(shù)據傳輸提供了超高帶寬(~27Tbps

2020-03-04 15:59:39 1517

1517 Achronix 最新基于臺積電(TSMC)的7nm FinFET工藝的Speedster7t FPGA器件包含了革命性的新型二維片上網絡(2D NoC)。

2020-05-04 09:43:00 593

593 可編程邏輯結構上運行的高速公路網絡一樣,為FPGA外部高速接口和內部可編程邏輯的數(shù)據傳輸提供了超高帶寬。 2. 2D NoC給Speedster 7t FPGA帶來的優(yōu)勢 日益增長的數(shù)據加速需求對硬件平臺

2021-11-12 09:21:22 1777

1777

片上網絡(2D NoC)來處理這些高帶寬數(shù)據流。Achronix的FPGA中特有的2D NoC實現(xiàn)是一種創(chuàng)新,它與用可編程邏輯資源來實現(xiàn)2D NoC的傳統(tǒng)方法相比,有哪些創(chuàng)新和價值呢?本白皮書討論

2022-04-21 09:27:35 1044

1044 邏輯單元(Logic Element,LE)在FPGA器件內部,用于完成用戶邏輯的最小單元。一個邏輯陣列包含16個邏輯單元以及一些其他資源, 在一個邏輯陣列內部的16個邏輯單元有更為緊密的聯(lián)系,可以實現(xiàn)特有的功能。

2022-06-15 16:50:21 2604

2604 Achronix Speedster7t FPGA除了在外圍Hard IP上都采用目前業(yè)內領先的大帶寬高速率IP,在內部的可編程邏輯的架構中也做了大量的優(yōu)化去進一步提高內部可編程邏輯的性能,從而適配

2022-07-05 15:37:41 924

924 成本、小尺寸、成本敏感的高容量應用到超高端連接帶寬、邏輯容量和信號處理能力,以滿足最苛刻的高性能應用,以及其它系列運用不同領域。

2022-11-03 14:39:54 1446

1446 NoC是相對于SoC的新一代片上互連技術,從計算機發(fā)展的歷史可以看到NoC 必將是SoC 之后的下一代主流技術,SoC 通常指在單一芯片上實現(xiàn)的數(shù)字計算機系統(tǒng),總線結構是該系統(tǒng)的主要特征,由于其可以

2023-07-13 15:57:08 556

556

NoC是相對于SoC的新一代片上互連技術,從計算機發(fā)展的歷史可以看到NoC 必將是SoC 之后的下一代主流技術

2023-07-13 15:56:43 635

635

可以商用的集成全域硬2D NoC的FPGA器件,以每通道512Gbps的速率和超過2Tbps的總帶寬來與所有系統(tǒng)接口和FPGA邏輯陣列互連。

2023-11-24 16:19:45 185

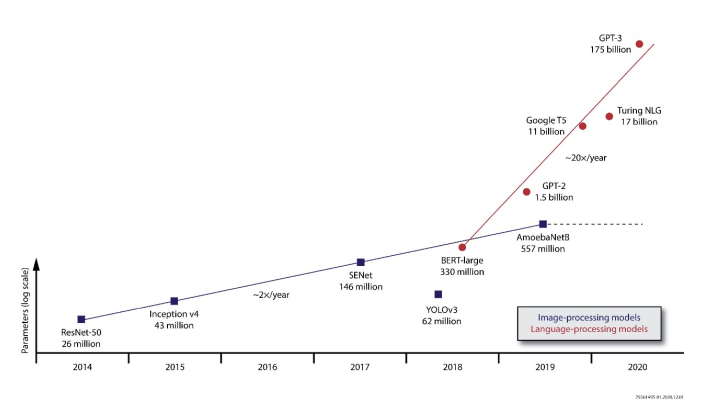

185 的FPGA內部信號引到引腳,然后用外部的邏輯分析儀捕獲數(shù)據。然而當設計的復雜程度增加時,這個方法就不再適合了,其中有幾個原因。第一是由于FPGA的功能增加了,而器件的引腳數(shù)目卻緩慢地增長。因此,可用邏輯對I/O的比率減小了,參見圖1。此外,設計很復雜時

2023-12-20 13:35:01 147

147

電子發(fā)燒友App

電子發(fā)燒友App

評論