半導體工藝技術進入深亞微米時代后,基于總線系統芯片SoC(Svstem on Chip)的體系結構在物理設計、通信帶寬以及功耗等方面無法滿足未來多IP體系發展的需求。片上網絡NoC(Netwotlk on Chip)是一種新的系統芯片體系結構,其核心思想是將計算機網絡技術移植到系統芯片設計中來,從體系結構上徹底解決總線架構帶來的問題。

研究人員從拓撲結構、路由算法、交換策略以及流控機制等多個方面對NoC進行研究,但是如何構建NoC驗證平臺,快速得到NoC的性能也一直是NoC研究的重點。

在過去的幾年里,一些研究機構提出了對于NoC不同抽象層次的驗證方法的研究,一般的NoC驗證是基于軟件的仿真和建模,如:用C、C++、SvstemC進行系統級建模仿真,這樣驗證很靈活,但在仿真時間上卻開銷很大。本文提出的基于FPGA的NoC驗證平臺在仿真速度方面是一般基于HDL的軟件仿真的16 000倍,而基于PC機編寫的NoC軟件更增強了該平臺的靈活性和實用性。

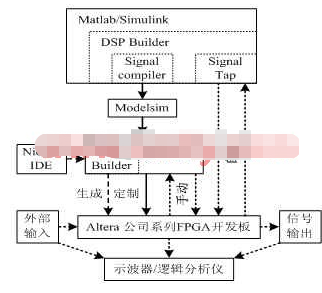

1 驗證平臺架構

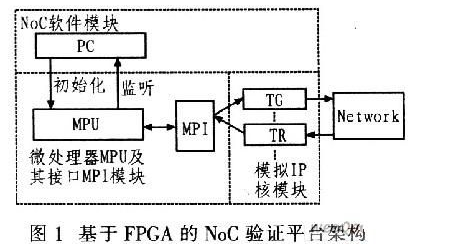

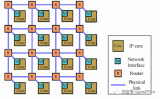

該驗證平臺采用模塊化設計,可以很容易地對不同的NoC進行功能驗證和性能*估。圖1給出了該驗證平臺的基本架構。

它主要包括3個模塊:

1)模擬IP核模塊 該模塊包含有數據流量產生器TG(Traffic Generator)模塊及數據流量接收器TR(Traffic Receiver)模塊。TG模擬產生NoC網絡中各個IP節點可能產生的數據流量,TR用于收集NoC運行過程中的各種信息。TG/R作為一個IP節點和待測NoC中的每個交換節點相連接。

2)微處理器MPU及其接口MPI模塊 PC機通過MPU(FPGA中自帶的NiosⅡ軟核)和MPI實現對NoC各IP核中TG內部各個配置寄存器的配置,并將TR中各個寄存器的內容讀取到PC機中進行處理。本模塊和模擬IP核模塊構成FPGA硬件平臺。

3)NoC軟件模塊 完成對NoC的配置以及NoC系統的性能統計。PC機通過MPU與FPGA進行通信,實現對NoC的配置并從FPGA中得到數據并進行后端處理,以圖形的方式顯示給用戶,供用戶對所設計的NoC進行*估。同時PC機可以監控NoC運行的情況。

FPGA采用Ahera公司Stratix IV系列中的EP4SGX230KF40C2,該器件能夠提供高速的時鐘信號和大量的片內資源,并具有大量外圍接口電路可供使用,這為基于FPGA的驗證提供了強有力的保證。

1.1 流量產生器TG

該平臺中的TG是一個可重用的軟核,用戶可以通過為配置寄存器寫入不同的配置信息使其產生不同的流量并注入NoC中。TR用于接收數據信息,并統計發包數和收包數。

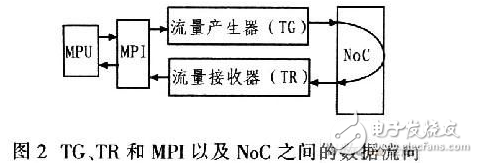

記錄延時信息,統計誤碼個數。圖2給出了TG、TR和MPI以及NoC之間的數據流向。

在片上網絡中,流量的分布由以下2方面決定:1)流量的源/目的節點對的分布,即空間位置上的通信概率分布,稱為空間分布;2)流量注入網絡時,注入網絡的時間間隔在時間上呈現的概率分布,稱為時間分布。為了使該平臺達到*價NoC性能的目的,流量產生器TG將從空間分布和時間分布的不同,模擬出不同的流量。

空間分布主要包括:1)給定目標地址:即配置TG產生發往確定目標地址的數據包;2)均勻分布:即配置TG產生均勻的發往網絡中各個節點的數據包,類似于網絡中的廣播現象;3)熱點分布:即配置TG產生發往網絡中一些特定的數據交換相對頻繁的節點的數據包;4)局部分布:即配置TG產生發往網絡中某一局部的網絡距離較近的節點的數據包;5)矩陣轉換地址分布:即按照矩陣X,Y向量轉置的特點。配置TG產生發往與發送節點地址相對應的節點的數據包。

時間分布主要包括:1)確定時間間隔:即配置TG每過一定數目的時鐘周期發送1個數據包,直到停止發包為止;2)自相似流量模型:即ON-OFF流量模型。即配置TG在一段時間內發送數據包,在一段時間內停止發包。此類流量模型就是模擬現實中在某一段時間突發很大的流量,而在另外的時間段不產生流量;3)隨機分布:即配置TG在發送1個數據包之間的間隔是1個隨機時鐘周期數。

空間分布和時間分布一般會交錯配置使用,那么組合之后可以產生十幾種不同的流量模型。另外,數據包的格式可以是用戶指定的數據,也可以是偽隨機序列PRBS(Pseudo Random Binary Sequences)。數據包的大小亦可由用戶指定,以數據片為單位,最小的數據包包含4片,最大的數據包包含511片。那么將流量模型和數據格式以及數據包的大小組合起來,就會產生種類更為豐富的流量模型。

流量產生器TG內部設有多個配置寄存器,包括:發包使能寄存器,發包間隔寄存器,發包地址和數據寄存器以及發包類型寄存器。這些寄存器統一編址,用戶可以通過配置這些寄存器控制TG工作。

1.2 流量接收器TR

流量接收器TR用于收集收發包數目,收發包的收據片,并且統計誤碼和時延信息。為了達到此目的,TR內部設有多個只讀寄存器,包括:發包個數寄存器.收包個數寄存器,發包數據寄存器,收包數據寄存器,中斷寄存器,誤碼計數器以及延時寄存器,延時寄存器可以保存最近80個包的延時信息。這些寄存器統一編址,可以通過訪問這些寄存器來讀取各種用于功能驗證和性能*估的原始數據。

1.3 微處理器MPU及微處理器接口MPI

微處理器MPU是在QuartusⅡ軟件的SOPC Builder工具中定制的。它包括1個NiosⅡ處理器IP核和外圍的一些并行輸入輸出接口。NiosIⅡ系列嵌入式處理器是一款通用的RISC結構的CPU,使用32位指令集結構(ISA)的二進制代碼兼容。將NiosⅡ處理器嵌入到FPGA硬件平臺中,配合整個系統實現驗證的功能。該平臺在所定制的NiosⅡ處理器的外圍還加入讀信號、寫信號、地址信號、輸入數據信號、輸出數據信號和中斷信號等,來完成PC機和FPGA硬件平臺之間的數據通信。

NiosⅡ處理器外圍還包括一個鎖相環(PLL)軟核,用于提供NoC電路中所需要的各種時鐘頻率。微處理器MPU與TG/R通信時,讀寫控制時鐘作為突發時鐘,頻率一般比較低。而NoC中交換節點之間的數據交換會由于特定電路的不同,工作時鐘頻率會大小不同,那么根據此工作頻率,PLL產生相應的時鐘信號配合其工作。MPU處理器僅占Stratix IVEP4SGX230KF40C2器件2 820個邏輯資源LE (Logic Element)(即1%)。因此使用非常高效。

該平臺還提供一個通用的微處理器接口MPI,用于保障MPU和TG/R之間的數據通信,也為MPU和TG/R的重復使用提供了統一接口。

1.4 NoC軟件

NoC軟件主要完成對FPGA硬件平臺的初始化配置和信息收集及統計處理。根據功能劃分為2部分:

1)NoC測試部分 其基本功能包括對FPGA硬件平臺的各個IP中TG內部配置寄存器的初始化配置,啟動產生數據流并注入到NoC中,同時對NoC的運行情況進行監控,并實時收集與功能驗證和性能*估相關的信息。該軟件是在NiosⅡ的集成開發環境(IDE)下用C語言設計開發的,在GNU的編譯器下編譯之后形成可以下載到MPU上直接運行的二進制文件。

2)NoC性能統計處理部分 該部分的主要功能是借助于第三方繪圖工具按照NoC性能統計規則對收集到的數據進行統計處理,并以圖表的方式直觀顯示NoC的基本功能和統計學性能。

以上兩部分都是在PC機上開發完成的,可應用于對不同NoC的測試與驗證。這為基于FPGA的硬件驗證平臺增強了靈活性和實用性。

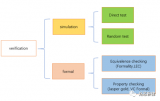

2 仿真驗證流程

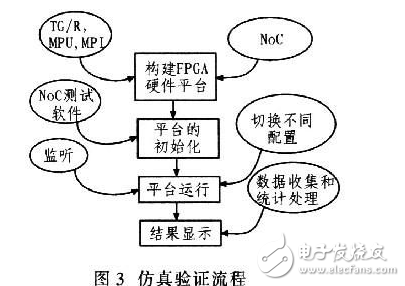

該驗證平臺的驗證流程包括FPGA硬件平臺的構建和對該硬件平臺的初始化配置以及NoC運行之后的信息收集和統計處理。仿真驗證流程如圖3所示。

其流程簡述如下:1)根據硬件架構思想和模塊化設計策略將用HDL語言描述的NoC連接到FPGA硬件平臺;2)初始化配置FPGA硬件平臺,在PC機上編寫NoC測試軟件,并通過Jtag線下載到MPU上運行,配置TG產生指定流量,并注入到NoC中;3)當FPGA平臺運行時,即當數據在NoC各個交換節點之間傳送或停止傳送時,用戶可以隨時改變配置以產生不同的流量,來測試NoC在不同流量下的性能,并隨時*測試平臺的運行情況;4)將TR收集到的數據在NiosⅡIDE的控制臺顯示,并保存數據。然后對收集到的數據進行統計處理,并以圖形的方式直觀顯示待測NoC的性能。

3 NoC性能統計處理

在驗證平臺中,采用PC機對NoC中運行之后相關的數據進行處理,并借助于第三方工具將處理結果以圖形方式顯示,以直觀表示NoC的性能。該平臺對于課題組設計的Mesh結構的NoC進行了功能驗證和性能*估。

主要處理包括平均網絡吞吐量和最近收到的80個數據包從發送端到接收端的網絡平均延時以及誤碼統計,下面簡單介紹性能*估的方法:

1)網絡平均吞吐量 對于TR收集到的收包個數通過PC讀取之后,繪制性能曲線圖。以歸一化仿真時間為基準,以相同時間段中收集的數據包數目作為網絡總吞吐量。

式中,總運行時間xlO%表示取歸一化時延的l/l0。

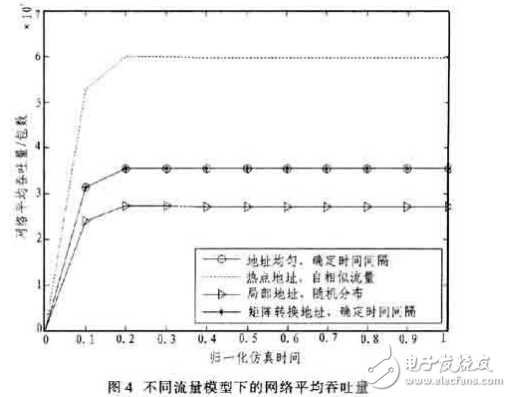

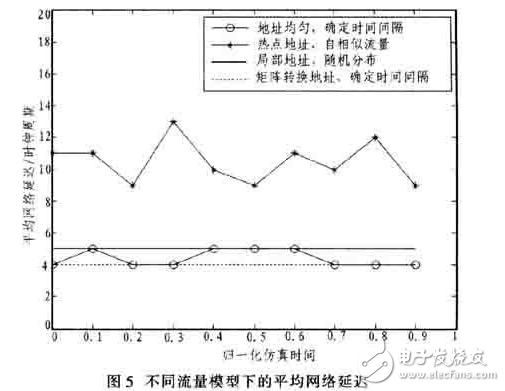

圖4給出了在不同流量模型下,每包4個數據片時,所設計NoC的網絡平均吞吐量。

2)平均網絡延遲 對于TR收集到的最近80個數據包從發送端到接收端的延遲信息,以歸一化仿真時間為基準,計算平均網絡延遲:

式中,P是發包總數,每個包的延遲為Li,那么Latency就是一段時間內的平均網絡延遲。

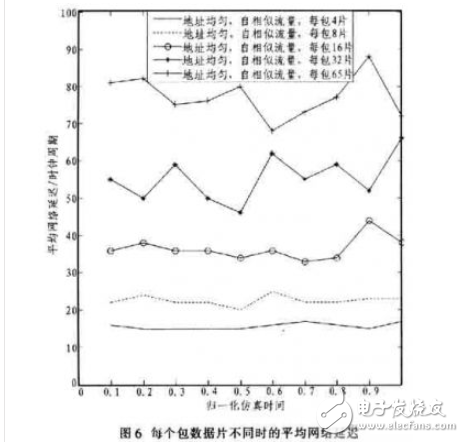

圖5給出了在不同流量模型下,在相同仿真時間段中接收到的數據包的平均網絡延遲。圖6給出了在相同的流量模型-均勻地址,自相似流量模型下,在相同仿真時間段中,對于每包分片不同時的平均網絡延遲。

3)誤碼統計 表l給出了誤碼個數統計表,這里所設計的NoC是有保障服務,因此,在NoC運行過程中并不產生誤碼。驗證結果與實際設計相一致。

4 結束語

本文提出了一種基于FPGA的NoC驗證平臺。詳細討論了該驗證平臺中FPGA硬件平臺和NoC軟件的基本功能,并闡述了TG/R,MPU,MPI以及NoC軟件的可重用性等特點。通過一個實例仿真驗證的結果說明了該驗證平臺的基本功能和優越性。目前正在開發不同參數化的流量模型,以便將該平臺用于對各種不同NoC的驗證。

電子發燒友App

電子發燒友App

評論