業(yè)界領(lǐng)先的全新 1.8V 版 VersaClock? 3S 可編程時(shí)鐘發(fā)生器,為消耗品和計(jì)算系統(tǒng)創(chuàng)造具有競(jìng)爭(zhēng)力的性能、能耗和靈活性。

2017-09-28 10:15:46 8178

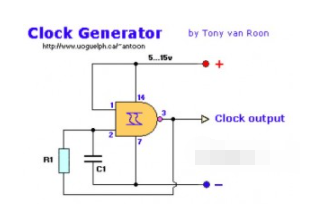

8178 1kHz信號(hào)發(fā)生器電路圖

2020-03-02 09:42:03

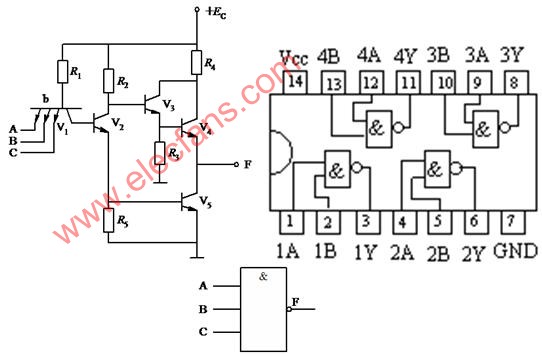

如圖,這是74AHC32的邏輯電路圖。請(qǐng)問(wèn)為何輸出端加了兩個(gè)非門(mén),是要做到延遲嗎?

2019-01-14 11:40:08

概述:AD9577是一款既提供一個(gè)多路輸出時(shí)鐘發(fā)生器功能,又帶有兩個(gè)片上鎖相環(huán)內(nèi)核PLL1和PLL2,專門(mén)針對(duì)網(wǎng)絡(luò)時(shí)鐘應(yīng)用而優(yōu)化。PLL設(shè)計(jì)基于ADI公司成熟的高性能、低抖動(dòng)頻率合成器產(chǎn)品系列,確保實(shí)現(xiàn)最高的網(wǎng)

2021-04-06 06:49:57

(ADC/DAC))和本振(LO)要求采用低抖動(dòng)參考時(shí)鐘以提高性能。其他基帶組件也要求各種頻率的時(shí)鐘源。表1.時(shí)鐘發(fā)生器——典型性能表2.時(shí)鐘分配產(chǎn)品——典型性能圖1.面向采用MIMO架構(gòu)的典型LTE

2018-10-18 11:29:03

系統(tǒng)設(shè)計(jì)師通常側(cè)重于為應(yīng)用選擇最合適的數(shù)據(jù)轉(zhuǎn)換器,在向數(shù)據(jù)轉(zhuǎn)換器提供輸入的時(shí)鐘發(fā)生器件的選擇上往往少有考慮。然而,如果不慎重考慮時(shí)鐘發(fā)生器的相位噪聲和抖動(dòng)性能,數(shù)據(jù)轉(zhuǎn)換器動(dòng)態(tài)范圍和線性度性能可能受到嚴(yán)重的影響。

2019-07-30 07:57:42

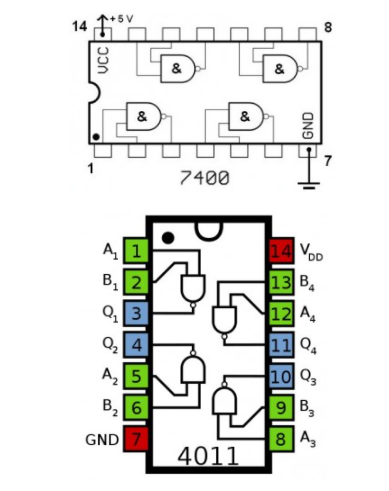

了解半加器、全加器的邏輯功能及三變量表決電路的邏輯功能。實(shí)驗(yàn)儀器設(shè)備1. 數(shù)字集成電路實(shí)驗(yàn)板 1塊2. 直流穩(wěn)壓電源 1A,5V 1臺(tái)3. 函數(shù)信號(hào)發(fā)生器 1臺(tái)4. 示波器 1臺(tái)5. 附加集成器件雙

2008-09-25 17:28:34

`AD9571ACPZPEC時(shí)鐘發(fā)生器產(chǎn)品介紹AD9571ACPZPEC詢價(jià)熱線AD9571ACPZPEC現(xiàn)貨AD9571ACPZPEC代理王先生***深圳市首質(zhì)誠(chéng)科技有限公司, AD9571具有

2019-07-09 10:19:09

AKD8140A Ver.2,AK8140??A可編程多時(shí)鐘發(fā)生器評(píng)估板。評(píng)估抖動(dòng)性能和功能很容易

2020-07-27 15:01:46

本應(yīng)用指南討論了CY2254 PLL時(shí)鐘發(fā)生器的內(nèi)部結(jié)構(gòu),并提出一些使用建議。

2014-09-23 10:00:14

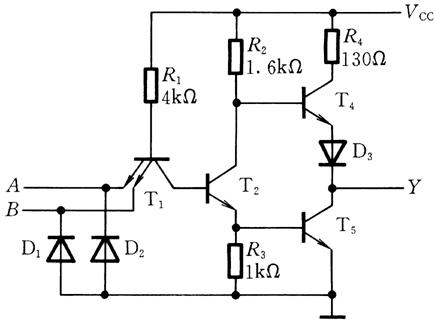

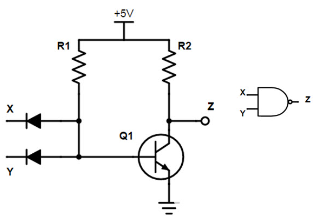

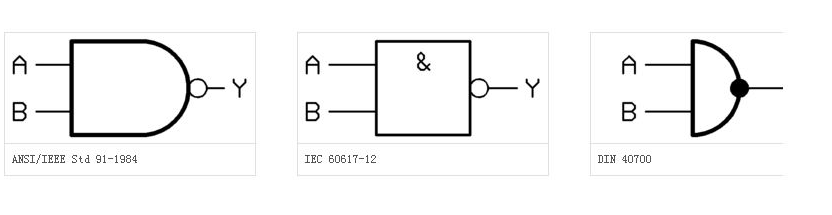

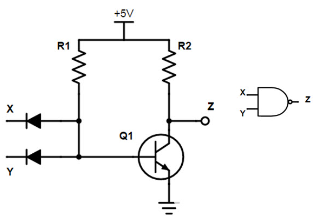

邏輯取反,從而使我們得到布爾值的表達(dá)式:AB= Q。然后,我們可以將2輸入數(shù)字邏輯與非門(mén)的操作定義為:“如果A和B都為真,則Q不為真”晶體管與非門(mén)可以使用如下所示連接在一起的RTL電阻-晶體管開(kāi)關(guān)構(gòu)建

2021-01-22 08:00:00

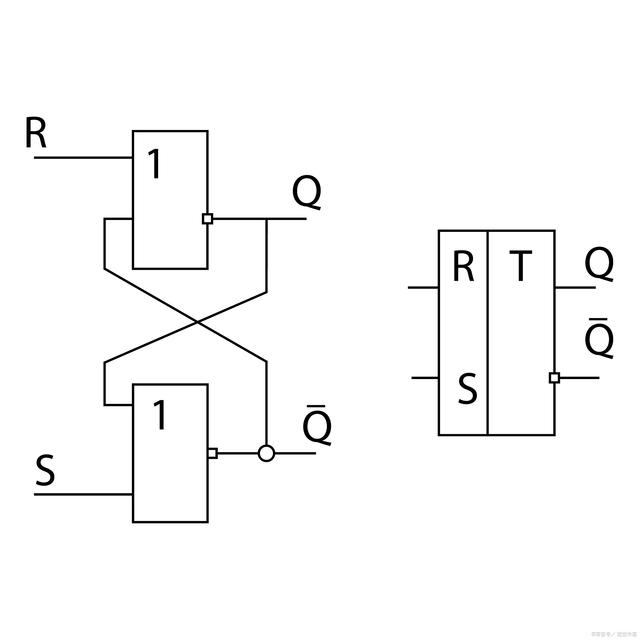

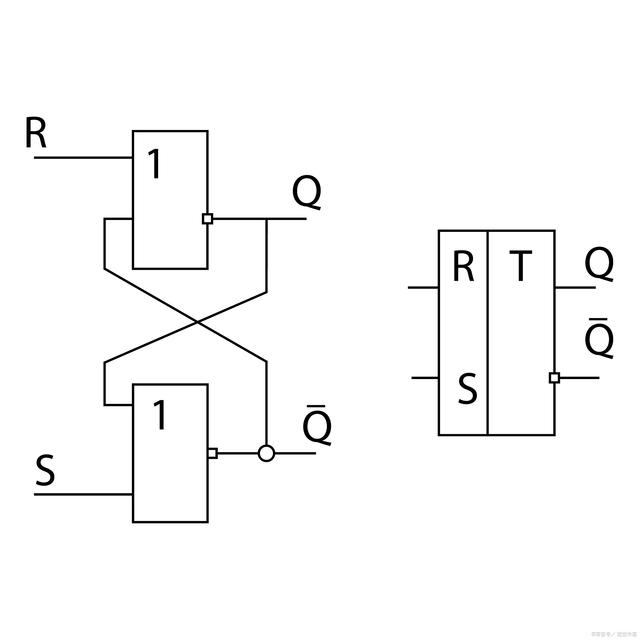

觸發(fā)器,與非門(mén)的輸入為什么是R非S非,而或非門(mén)是RS。我百度到的說(shuō)法是,與非門(mén)是低電平觸發(fā),或非門(mén)是高電平觸發(fā),也就是要使Q=1,與非門(mén)里S非=0,或非門(mén)S=1。那不都是S=1么,那與非門(mén)為什么要非

2020-01-28 20:39:32

為什么我的pwm波信號(hào)一接到與非門(mén)上,幅值就會(huì)降一半(附電路圖)

2018-02-02 21:20:33

概述:MAX3625B是MAXIM公司生產(chǎn)的一款提供三路輸出的低抖動(dòng),高精度時(shí)鐘發(fā)生器。該MAX3625B是為網(wǎng)絡(luò)應(yīng)用而優(yōu)化的低抖動(dòng),高精度時(shí)鐘發(fā)生器。該器件集成一個(gè)晶體振蕩器和鎖相環(huán)(PLL)時(shí)鐘

2021-05-18 07:39:05

供應(yīng) 現(xiàn)貨 CG635 斯坦福 時(shí)鐘發(fā)生器 歐陽(yáng)R:*** QQ:1226365851溫馨提示:如果您找不到聯(lián)系方式,請(qǐng)?jiān)跒g覽器上搜索一下,旺貿(mào)通儀器儀回收工廠或個(gè)人、庫(kù)存閑置、二手儀器及附件。長(zhǎng)期

2020-08-18 09:08:58

利用74LS00二輸入與非門(mén)實(shí)現(xiàn)“與電路”、“或電路”、“或非電路”、“異或電路”、“同或電路”,要寫(xiě)出以上各電路的邏輯表達(dá)式和真值表,畫(huà)出用二輸入與非門(mén)實(shí)現(xiàn)的邏輯圖并在實(shí)驗(yàn)箱上加以驗(yàn)證

2020-11-04 17:04:17

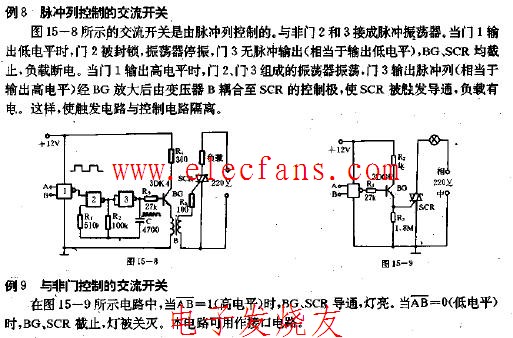

請(qǐng)問(wèn)各位電子大佬,這里IC2與非門(mén)的作用是什么?(坐標(biāo)電路2)為什么要接到555的Trigger引腳?

2020-06-22 11:49:42

可編程音頻時(shí)鐘發(fā)生器MAX9485資料下載內(nèi)容主要介紹了:MAX9485引腳功能MAX9485功能和特性MAX9485應(yīng)用范圍MAX9485內(nèi)部方框圖MAX9485極限參數(shù)MAX9485典型應(yīng)用電路

2021-04-02 06:21:48

我要做畢業(yè)設(shè)計(jì) 叫 基于lmk03806的高性能可編程時(shí)鐘發(fā)生器的設(shè)計(jì)與fpga實(shí)現(xiàn),需要有protel 99se畫(huà) lmk03806的原理圖和fpga的配置電路,用vhdl編程仿真,用fpga來(lái)配置lmk03806,求高手求助{:1:}

2013-05-03 23:06:27

在我們的設(shè)計(jì)中,其中一個(gè)模塊從外部可配置時(shí)鐘發(fā)生器芯片接收其時(shí)鐘信號(hào)。現(xiàn)在在我們的ML507上使用這個(gè)時(shí)鐘發(fā)生器芯片IDT5V9885就在那里任何跳線設(shè)置?我們問(wèn)這個(gè)是因?yàn)樵谖覀兊纳暾?qǐng)中軟件我們

2019-09-02 08:12:30

擴(kuò)頻時(shí)鐘發(fā)生器MAX31C80資料下載內(nèi)容包括:MAX31C80引腳功能MAX31C80功能和特性MAX31C80應(yīng)用范圍MAX31C80內(nèi)部方框圖MAX31C80電壓范圍MAX31C80典型應(yīng)用電路

2021-04-02 06:29:55

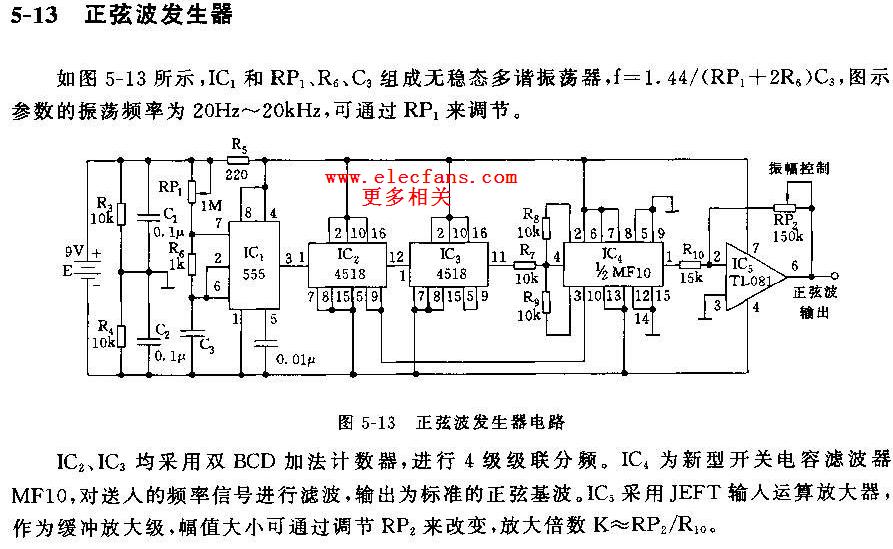

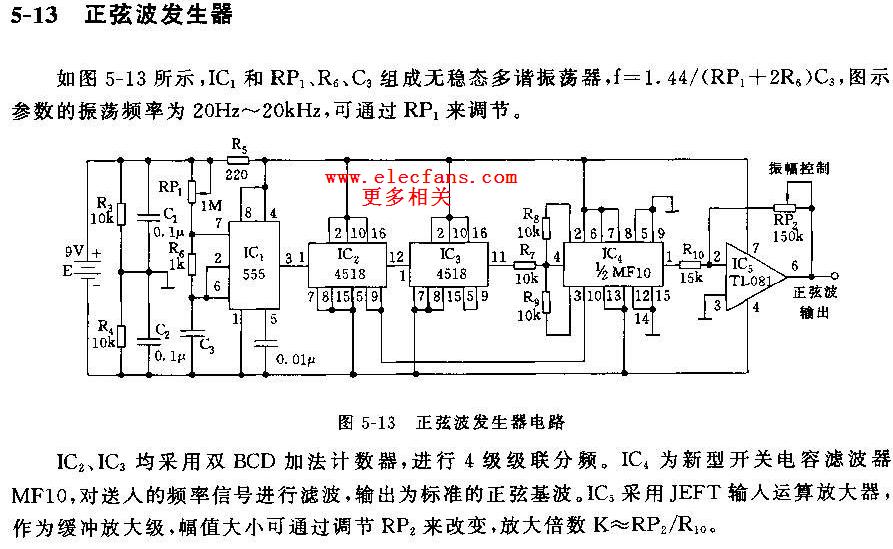

正弦波發(fā)生器電路圖

2009-11-25 10:17:36

SI52147-EVB,用于PoE無(wú)線接入點(diǎn)的時(shí)鐘發(fā)生器評(píng)估板。 Si52147是一款符合PCIe Gen1,Gen2和Gen3標(biāo)準(zhǔn)的9端口PCIe時(shí)鐘發(fā)生器

2020-08-27 14:27:11

555多種信號(hào)發(fā)生器電路圖

2019-10-23 00:50:57

信號(hào)發(fā)生器電路圖

2019-10-09 09:11:01

數(shù)字正弦波發(fā)生器電路圖

2019-09-12 09:10:22

描述TIDA-00597 可為時(shí)鐘發(fā)生器提供噪聲非常低的輸出電源。主要特色低噪聲,適用于時(shí)鐘發(fā)生器輸出電流高達(dá) 800mA低相位噪聲輸出功率啟用和禁用

2018-08-22 07:43:40

AC1571時(shí)鐘發(fā)生器一款基于PLL的、適用于5G基站應(yīng)用的時(shí)鐘發(fā)生器。采用數(shù)字鎖相環(huán)技術(shù),以實(shí)現(xiàn)最佳的高頻低相噪性能,具有低功耗和高PSRR能力。采用ADPLL技術(shù),管腳兼容843N571,可以

2022-08-11 16:26:33

AC1571 是用于 5G 基站應(yīng)用的基于 PLL的時(shí)鐘發(fā)生器,該芯片采用全數(shù)字鎖相環(huán)技術(shù),以實(shí)現(xiàn)最佳的高頻低相噪性能,并具有低功耗和高PSRR能力。典型應(yīng)用場(chǎng)景:· 無(wú)線基站·

2023-12-12 14:25:17

時(shí)鐘發(fā)生器芯片廠家 時(shí)鐘芯片是一種基于PLL的時(shí)鐘發(fā)生器,采用ADPLL(全數(shù)字鎖相環(huán))技術(shù),以實(shí)現(xiàn)的高頻低相噪性能,并具備低功耗和高PSNR能力,可實(shí)現(xiàn)小于0.3ps RMS的相位抖動(dòng)性能

2023-12-29 09:29:50

時(shí)鐘發(fā)生器芯片廠家 時(shí)鐘芯片是一種基于PLL的時(shí)鐘發(fā)生器,采用ADPLL(全數(shù)字鎖相環(huán))技術(shù),以實(shí)現(xiàn)的高頻低相噪性能,并具備低功耗和高PSNR能力,可實(shí)現(xiàn)小于0.3ps RMS的相位抖動(dòng)性能

2024-02-04 11:41:14

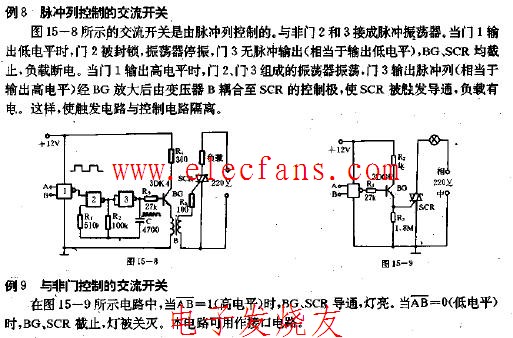

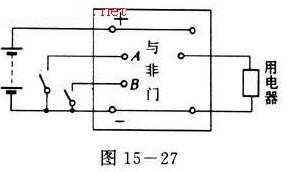

與非門(mén)控制的交流開(kāi)關(guān)電路圖

2007-12-16 01:26:06 1147

1147

正弦波發(fā)生器電路圖,電路由IC,TL082組成。

圖二:正弦波信號(hào)發(fā)生器電路圖

2008-01-02 19:16:06 3396

3396

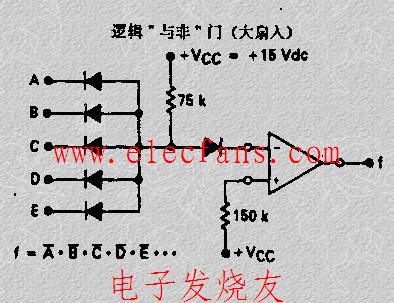

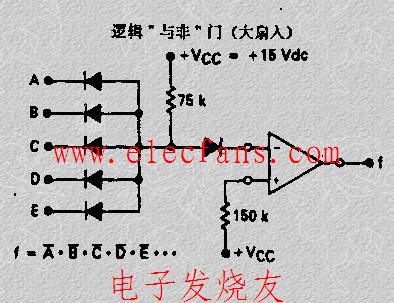

邏輯與非門(mén)

2008-06-12 23:24:21 1675

1675

MAX9489/MAX9471多輸出時(shí)鐘發(fā)生器構(gòu)建集成時(shí)鐘源

摘要:與典型的“本地”時(shí)鐘方案相比,集成的多輸出時(shí)鐘發(fā)生器有許多優(yōu)勢(shì)。本文探討了集中時(shí)鐘發(fā)生器(如

2008-10-04 20:43:25 922

922

Si5338 業(yè)界首個(gè)任意頻率、任意輸出的時(shí)鐘發(fā)生器

高性能模擬與混合信號(hào)領(lǐng)導(dǎo)廠商Silicon Laboratories日前發(fā)表全新的時(shí)鐘發(fā)生器和緩沖器系列,可為業(yè)

2008-11-10 09:39:44 1763

1763

精密時(shí)鐘發(fā)生器電路圖

2009-03-25 09:35:22 1054

1054

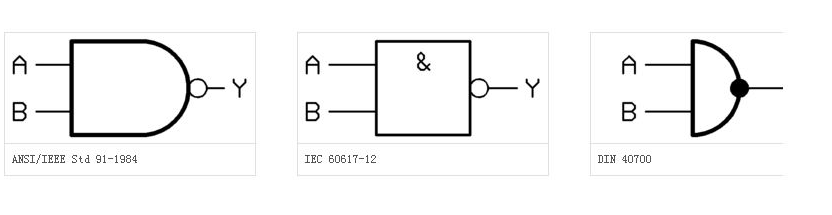

與非門(mén)邏輯符號(hào)

2009-04-06 01:12:18 2477

2477 與非門(mén)電路圖

2009-04-06 23:12:46 9596

9596

與非門(mén)邏輯符號(hào)圖

2009-04-06 23:13:21 42760

42760

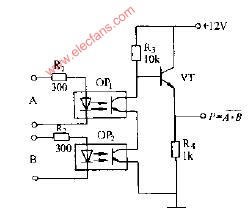

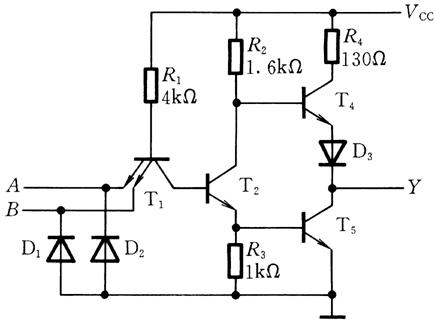

與非門(mén)電路原理

(1)電路結(jié)構(gòu)及工作原理 TTL與非門(mén)是TTL邏輯門(mén)的基本形式,典型的TTL與非門(mén)電路結(jié)構(gòu)如圖8-16所示。該電路由

2009-04-06 23:14:15 16662

16662

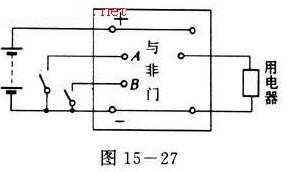

與非門(mén)電路介紹圖15-26甲是我們實(shí)驗(yàn)用的與非門(mén),它也有兩個(gè)輸入瑞A、B,圖乙是它在電路中的接法。

2009-04-06 23:17:48 16256

16256

振蕩器時(shí)鐘發(fā)生器電路圖

2009-04-13 08:54:22 720

720

摘要:與典型的“本地”時(shí)鐘方案相比,集成的多輸出時(shí)鐘發(fā)生器有許多優(yōu)勢(shì)。本文探討了集中時(shí)鐘發(fā)生器(如MAX9489和MAX9471)的優(yōu)點(diǎn),如:降低系統(tǒng)成本、良好的信號(hào)完整性、抑制干

2009-04-22 10:11:53 407

407

摘要:與典型的“本地”時(shí)鐘方案相比,集成的多輸出時(shí)鐘發(fā)生器有許多優(yōu)勢(shì)。本文探討了集中時(shí)鐘發(fā)生器(如MAX9489和MAX9471)的優(yōu)點(diǎn),如:降低系統(tǒng)成本、良好的信號(hào)完整性、抑制干

2009-05-03 11:07:05 653

653

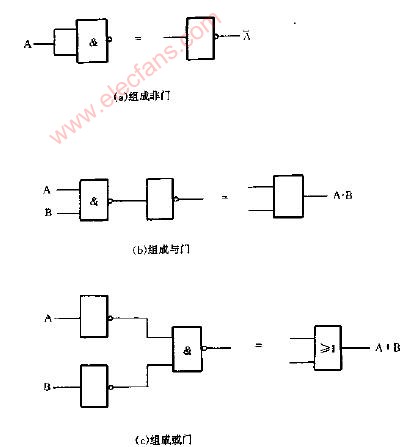

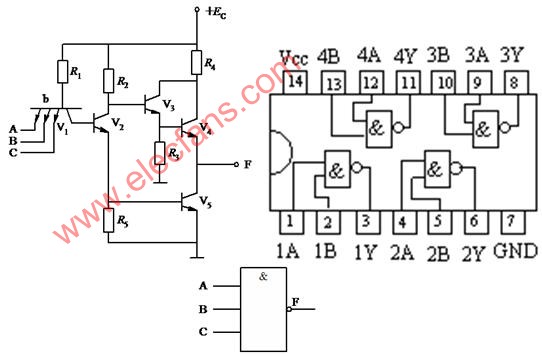

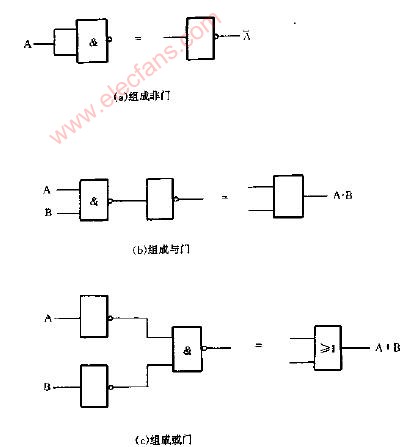

利用與非門(mén)組成的一些門(mén)電路圖

2009-05-08 14:35:10 17458

17458

繼電器與非門(mén)電路圖

2009-05-08 15:35:18 1858

1858

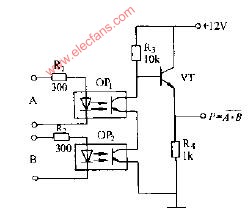

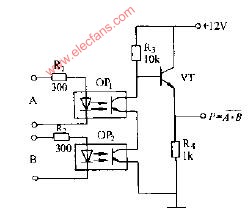

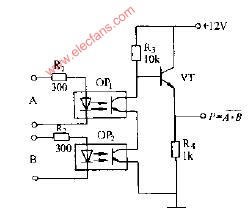

光耦合器構(gòu)成的與非門(mén)電路圖

2009-06-04 16:25:53 4871

4871

光耦合器構(gòu)成的與非門(mén)電路圖

2009-06-06 08:32:44 2754

2754

TTL與非門(mén)電路

2009-07-15 18:55:34 3314

3314

評(píng)估低抖動(dòng)PLL時(shí)鐘發(fā)生器的電源噪聲抑制性能

本文介紹了電源噪聲對(duì)基于PLL的時(shí)鐘發(fā)生器的干擾,并討論了幾種用于評(píng)估確定性抖動(dòng)(DJ)的技術(shù)方案。推導(dǎo)出的關(guān)系式提

2009-09-18 08:46:32 1461

1461

TTL集成與非門(mén)電路

TTL與非門(mén)芯

2009-09-24 10:25:42 2954

2954

MAX3625B 抖動(dòng)僅為0.36ps的PLL時(shí)鐘發(fā)生器

概述

MAX3625B是一款低抖動(dòng)、精密時(shí)鐘發(fā)生器,優(yōu)化用于網(wǎng)絡(luò)設(shè)備。器件內(nèi)置晶體振蕩器和鎖相環(huán)(PLL)

2010-03-01 08:56:18 1345

1345

與非門(mén),與非門(mén)是什么意思

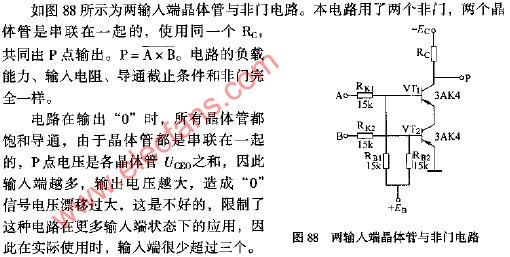

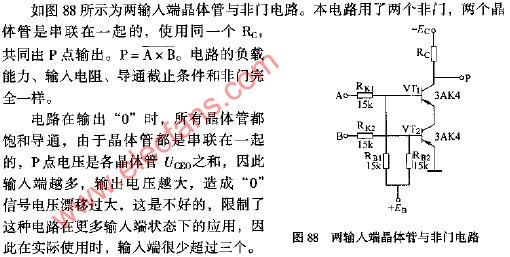

DTL與非門(mén)電路:

常將二極管與門(mén)和或門(mén)與三極管非門(mén)組合起來(lái)組成與非門(mén)和或非門(mén)電路,以消除在串接時(shí)產(chǎn)生的電

2010-03-08 11:41:15 11219

11219 兩輸入端晶體管與非門(mén)電路圖

2010-03-29 17:03:19 4196

4196

MAX3679A高性能四路輸出時(shí)鐘發(fā)生器(Maxim)

Maxim推出用于以太網(wǎng)設(shè)備的高性能、四路輸出時(shí)鐘發(fā)生器MAX3679A。器件采用低噪聲

2010-04-14 16:51:49 778

778 如何利用GPS OEM來(lái)進(jìn)行二次開(kāi)發(fā),產(chǎn)生高精度時(shí)鐘發(fā)生器是一個(gè)研究的熱點(diǎn)問(wèn)題。在電力系統(tǒng)、CDMA2000、DVB、DMB等系統(tǒng)中,高精度的GPS

2010-07-24 15:45:26 780

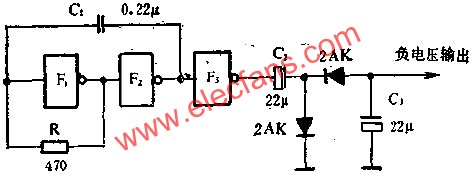

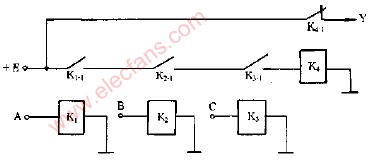

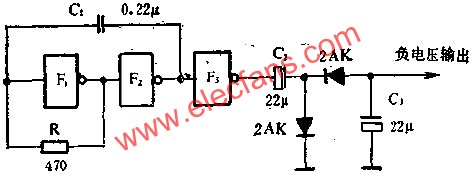

780 有時(shí)在電子設(shè)備中需用一組功率不大的負(fù)電源,這時(shí)可不必另裝電源,只需用三個(gè)與非門(mén)按圖中連接,即可進(jìn)行電

2010-09-15 00:23:35 588

588

在電力系統(tǒng)、CDMA2000、DVB、DMB等系統(tǒng)中,高精度的GPS時(shí)鐘發(fā)生器(GPS同步時(shí)鐘)對(duì)維持系統(tǒng)正常運(yùn)轉(zhuǎn)有至關(guān)重要的意義。

那如何利用GPS OEM來(lái)進(jìn)行二次開(kāi)發(fā),產(chǎn)生高精度時(shí)鐘發(fā)生

2010-09-17 22:02:44 1273

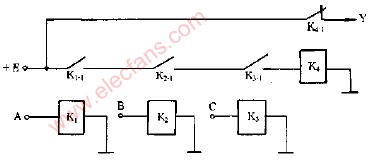

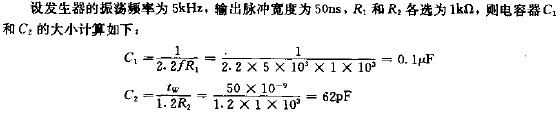

1273 實(shí)際上,自激多諧振蕩器(圖1)和單穩(wěn)電路可以由集成電路來(lái)實(shí)現(xiàn).采用兩片四-2輸入與非門(mén)74LS00的驅(qū)動(dòng)信號(hào)發(fā)生器,

2010-11-14 12:16:07 1124

1124

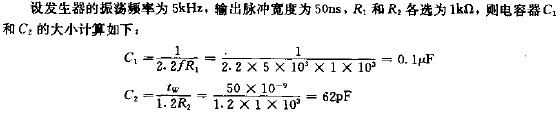

這里設(shè)計(jì)一種基于DP標(biāo)準(zhǔn)采用μ工藝的發(fā)射端擴(kuò)頻時(shí)鐘發(fā)生器。合理設(shè)計(jì)鎖相環(huán)路,采用外加濾波器對(duì)壓控振蕩器的控制電壓進(jìn)行三角波調(diào)制,得到所需的擴(kuò)頻時(shí)鐘。

2011-08-31 10:17:32 1763

1763

MAX3636是一個(gè)高度靈活,高精度鎖相環(huán)(PLL)時(shí)鐘發(fā)生器為下一代網(wǎng)絡(luò)設(shè)備的要求低抖動(dòng)時(shí)鐘發(fā)生器和強(qiáng)大的高速數(shù)據(jù)傳輸?shù)姆植歼M(jìn)行了優(yōu)化。

2011-10-11 11:15:22 1329

1329

10GHz擴(kuò)頻時(shí)鐘發(fā)生器的設(shè)計(jì)_胡帥帥

2017-01-07 21:28:58 1

1 Microchip基于MEMS的時(shí)鐘發(fā)生器

2018-06-07 13:46:00 4534

4534

Microchip基于MEMS的時(shí)鐘發(fā)生器

2018-07-08 01:23:00 3933

3933 與非門(mén)(英語(yǔ):NAND gate)是數(shù)字電路的一種基本邏輯電路。若當(dāng)輸入均為高電平(1),則輸出為低電平(0);若輸入中至少有一個(gè)為低電平(0),則輸出為高電平(1)。與非門(mén)可以看作是與門(mén)和非門(mén)的疊加。

2018-07-25 19:10:18 46674

46674

關(guān)鍵詞:發(fā)生器 , 負(fù)電源 , 與非門(mén) 在電子設(shè)備中有時(shí)需用一組功率不大的負(fù)電源,可用三個(gè)與非門(mén)按圖所示方法連接,即可進(jìn)行電源極性變換。圖示電路中A1、A2組成約4kHz的自激多諧振蕩器,A3

2018-09-16 09:07:01 361

361 據(jù)麥姆斯咨詢報(bào)道,Microchip推出了業(yè)界尺寸最小的MEMS時(shí)鐘發(fā)生器DSC613。這款新器件可在電路板上最多替換掉三個(gè)晶振和振蕩器,從而減少高達(dá)80%的時(shí)鐘元件布板空間。

2018-11-15 16:38:26 3910

3910 本文檔的主要內(nèi)容詳細(xì)介紹的是兩個(gè)與非門(mén)電路的介紹 與非門(mén)(英語(yǔ):NAND gate)是數(shù)字電路的一種基本邏輯電路。若當(dāng)輸入均為高電平(1),則輸出為低電平(0);若輸入中至少有一個(gè)為低電平(0),則輸出為高電平(1)。與非門(mén)可以看作是與門(mén)和非門(mén)的疊加。

2019-01-09 08:00:00 18

18 AD9523:14路LVPECL/LVDS/HSTL輸出 或29路LVCMOS輸出 低抖動(dòng)時(shí)鐘發(fā)生器

2019-07-04 06:18:00 3604

3604 邏輯與非門(mén)是數(shù)字邏輯與門(mén)和非門(mén)串聯(lián)連接在一起的組合,NAND (非與)門(mén)具有當(dāng)輸入的ALL處于邏輯電平“1”時(shí),輸出通常處于邏輯電平“1”并且僅“低”到邏輯電平“0”。邏輯與非門(mén)是我們之前看到的AND門(mén)的反向或“互補(bǔ)”形式。

2019-06-26 14:20:46 8884

8884

本文檔的主要內(nèi)容詳細(xì)介紹的是使用Multisim實(shí)現(xiàn)與非門(mén)測(cè)試的實(shí)驗(yàn)電路圖免費(fèi)下載。

2020-09-04 16:55:00 20

20 本文檔的主要內(nèi)容詳細(xì)介紹的是與非門(mén)邏輯電路功能測(cè)試的原理圖免費(fèi)下載。

2020-10-12 16:18:48 25

25 本文檔的主要內(nèi)容詳細(xì)介紹的是與非門(mén)搭接的邏輯電路原理圖免費(fèi)下載。

2020-10-12 16:18:48 7

7 系統(tǒng)設(shè)計(jì)師通常側(cè)重于為應(yīng)用選擇最合適的數(shù)據(jù)轉(zhuǎn)換器,在向數(shù)據(jù)轉(zhuǎn)換器提供輸入的時(shí)鐘發(fā)生器件的選擇上往往少有考慮。然而,如果不慎重考慮時(shí)鐘發(fā)生器的相位噪聲和抖動(dòng)性能,數(shù)據(jù)轉(zhuǎn)換器動(dòng)態(tài)范圍和線性度性能可能受到嚴(yán)重的影響。

2020-11-22 11:34:38 2666

2666

AD9525: 8路LVPECL輸出低抖動(dòng)時(shí)鐘發(fā)生器

2021-03-21 15:00:20 0

0 AD9571:以太網(wǎng)時(shí)鐘發(fā)生器,10個(gè)時(shí)鐘輸出

2021-04-16 10:21:56 3

3 AD9551:多業(yè)務(wù)時(shí)鐘發(fā)生器數(shù)據(jù)表

2021-04-28 10:30:52 0

0 AN-1576:采用AD9958 500 MSPS DDS或AD9858 1 GSPS DDS和AD9515時(shí)鐘分配IC的高性能ADC的低抖動(dòng)采樣時(shí)鐘發(fā)生器

2021-04-30 09:48:42 13

13 AD9573:PCI-Express時(shí)鐘發(fā)生器IC,PLL內(nèi)核,分頻器,雙輸出數(shù)據(jù)表

2021-05-08 20:05:05 5

5 AD9575:網(wǎng)絡(luò)時(shí)鐘發(fā)生器,雙輸出數(shù)據(jù)表

2021-05-09 11:06:44 1

1 時(shí)鐘發(fā)生器AD9516-0技術(shù)手冊(cè)

2022-01-25 15:59:42 7

7 Cypress時(shí)鐘發(fā)生器應(yīng)用在車輛、工業(yè)生產(chǎn)、消費(fèi)品和網(wǎng)絡(luò)服務(wù)的EMI降低和非EMI降低時(shí)鐘發(fā)生器。 Cypress具有廣泛的時(shí)鐘發(fā)生器組合,兼容700MHz的頻率和不超過(guò)0.7PS的RMS相位抖動(dòng)

2022-04-22 09:02:09 806

806 這是帶有板上芯片(COB)的1Hz時(shí)鐘發(fā)生器電路。通常,為數(shù)字時(shí)鐘和計(jì)數(shù)器電路應(yīng)用產(chǎn)生1Hz時(shí)鐘的電路將IC與晶體和微調(diào)電容器等結(jié)合使用。

2022-06-07 10:43:50 1886

1886

邏輯門(mén)是數(shù)字世界中的基本元素,之前已經(jīng)介紹過(guò)基本的邏輯門(mén)。這些基本的邏輯門(mén)可以由通用門(mén)構(gòu)成。數(shù)字邏輯中有兩個(gè)通用門(mén),即與非門(mén)(NAND Gate)和或非門(mén)(NOR Gate)。

2022-09-12 14:50:00 6891

6891

本文討論電源噪聲干擾對(duì)基于PLL的時(shí)鐘發(fā)生器的影響,并介紹幾種用于評(píng)估由此產(chǎn)生的確定性抖動(dòng)(DJ)的測(cè)量技術(shù)。派生關(guān)系顯示了如何使用頻域雜散測(cè)量來(lái)評(píng)估時(shí)序抖動(dòng)行為。實(shí)驗(yàn)室臺(tái)架測(cè)試結(jié)果用于比較測(cè)量技術(shù),并演示如何可靠地評(píng)估參考時(shí)鐘發(fā)生器的電源噪聲抑制(PSNR)性能。

2023-04-11 11:06:39 811

811

極景微發(fā)布超小封裝PCIe5.0時(shí)鐘發(fā)生器日前,極景微(UltraSilicon)宣布,推出兩款支持PCIe5.0接口標(biāo)準(zhǔn)的1輸出及2輸出時(shí)鐘發(fā)生器,分別為US6D101和US6D102。該芯片具有

2023-02-02 15:25:54 999

999

與非門(mén)(NAND Gate)是數(shù)字電路中的基本邏輯門(mén)之一,它實(shí)現(xiàn)了邏輯AND(與)操作后再進(jìn)行邏輯NOT(非)操作。

2023-09-04 15:31:07 1974

1974

時(shí)鐘發(fā)生器由哪些部分組成?鎖相環(huán)pll的特點(diǎn)是什么?如何用硬件配置pll? 時(shí)鐘發(fā)生器是指通過(guò)特定的電路設(shè)計(jì)產(chǎn)生適合各種電子設(shè)備使用的時(shí)鐘信號(hào)的器件。時(shí)鐘發(fā)生器由多個(gè)部分組成,其中最核心的是鎖相環(huán)

2023-10-13 17:39:50 444

444 時(shí)鐘合成器和時(shí)鐘發(fā)生器是兩種用于產(chǎn)生時(shí)鐘信號(hào)的電子器件,它們?cè)诠δ芎蛻?yīng)用上有一些區(qū)別。

2023-11-09 10:26:56 298

298 的時(shí)鐘發(fā)生器件的選擇上往往少有考慮。目前市場(chǎng)上有性能屬性大相徑庭的眾多時(shí)鐘發(fā)生器。然而,如果不慎重考慮時(shí)鐘發(fā)生器、相位噪聲和抖動(dòng)性能,數(shù)據(jù)轉(zhuǎn)換器、動(dòng)態(tài)范圍和線性度性能可能受到嚴(yán)重的影響。...

2023-11-28 14:33:57 0

0 TTL與非門(mén)的電壓傳輸特性 TTL與非門(mén)的靜態(tài)輸入與輸出特性 TTL與非門(mén)的動(dòng)態(tài)特性? TTL與非門(mén)是一種基本的邏輯門(mén)電路,用于將兩個(gè)輸入信號(hào)進(jìn)行邏輯與運(yùn)算,并輸出結(jié)果。TTL(雙晶體管邏輯)是一種

2024-01-23 13:52:51 410

410

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論