1 數(shù)字信號處理FPGA設(shè)計實現(xiàn)和驗證中存在的問題和解決方法

用FPGA來實現(xiàn)信號處理的算法有可能碰到以下一種或幾種情況:

a. 實現(xiàn)復(fù)雜的數(shù)字處理功能,例如實現(xiàn)DFT、數(shù)字濾波等通信信號處理算法;

b. 模塊多且功能驗證十分繁瑣;

c. 數(shù)字系統(tǒng)尚包含某些不確定因素,例如環(huán)路參數(shù)等;

d. 數(shù)字系統(tǒng)包含范圍較大的反饋環(huán)節(jié)。

實際設(shè)計中碰到的困難主要是以前的設(shè)計流程中系統(tǒng)方案和原理性仿真與硬件設(shè)計仿真脫節(jié),尤其是在高速數(shù)字信號處理FPGA設(shè)計實現(xiàn)中沒有很好的算法仿真驗證手段。

聯(lián)合設(shè)計與仿真的方法針對數(shù)字信號處理FPGA設(shè)計實現(xiàn)中碰到的問題和困難,提出了有效可行的解決方法,大大提高了數(shù)字信號處理算法FPGA設(shè)計實現(xiàn)的效率,有較高的推廣應(yīng)用價值。聯(lián)合設(shè)計與仿真的方法主要包括以下3個方面。

a. 分別創(chuàng)建數(shù)字系統(tǒng)的MATLAB仿真的數(shù)據(jù)源產(chǎn)生程序和實現(xiàn)特定功能的系統(tǒng)算法程序以及VHDL設(shè)計仿真程序模型;根據(jù)硬件性能對MATLAB 中的數(shù)據(jù)源進行量化,由浮點數(shù)轉(zhuǎn)化成定點數(shù)據(jù)源,把系統(tǒng)仿真(浮點)中的某些功能模塊改造成定點模型的MATLAB 模型,比如用定點的Simu-link模塊來建立定點模型。

b. 對VHDL源程序需要仿真的部分分層次建立VHDL Testbench文件,把原文件關(guān)聯(lián)進去;在Testbench文件中運用VHDL語言的TextIO程序包實現(xiàn)對輸入輸出數(shù)據(jù)的讀寫,再結(jié)合ModelSim仿真軟件實現(xiàn)對數(shù)字系統(tǒng)的仿真;仿真后輸出的測試數(shù)據(jù)可以在VHDL Testbench文件指定的輸出文本文件中找到,它的數(shù)據(jù)存儲格式是按列向量存儲的,可以直接被MATLAB讀取,做有關(guān)數(shù)學(xué)運算或者數(shù)字信號處理運算如FFT等的運算并繪圖顯示。

c. 特殊功能模塊的仿真與驗證,如對一些存儲器的初始化和仿真以及一些雙向總線的仿真都是由特定的測試方法來完成的的。

2 VHDL Testbench的概念和高效的Testbench文件編寫

2.1 FPGA測試與驗證的基本概念及方法

(1)測試基準(zhǔn)

一旦設(shè)計者描述了一個設(shè)計,必須對其進行驗證,以檢查是否符合設(shè)計規(guī)范。最常見的驗證方法是在模擬時施加輸入激勵信號,然后“讀”該設(shè)計的輸出信號。ModelSim等波形仿真軟件可以完成這個“讀”的功能,但是輸入激勵信號需要用模擬器來完成。使用模擬器輸入激勵語言的一個主要缺點是它隨著模擬器的不同而不同。

驗證的另一個方法是用VHDL編寫一個測試模型發(fā)生器和要檢查的輸出,稱為測試基準(zhǔn)( Test-bench) ,它既提供輸入信號,又測試設(shè)計的輸出信號。由于測試基準(zhǔn)也可能產(chǎn)生錯誤,所以它必須也能被測試。建議既要有VHDL測試基準(zhǔn),又要用環(huán)境模型來驗證元件,稱為系統(tǒng)模擬。VHDL測試基準(zhǔn)的建立可以用VHDL語言標(biāo)準(zhǔn)程序包中的TextIO來實現(xiàn),具體的TextIO在下一節(jié)介紹。

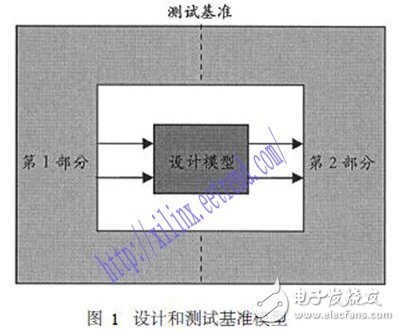

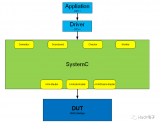

系統(tǒng)模擬的優(yōu)點是元件的激勵由系統(tǒng)仿真的數(shù)據(jù)源產(chǎn)生,近似于表示實際的模型產(chǎn)生。系統(tǒng)模擬的時間由輸入的需要模擬的數(shù)據(jù)量來決定。在通信信號處理的仿真中,往往需要很大的數(shù)據(jù)量來驗證設(shè)計的正確性,所以系統(tǒng)模擬的一個缺點就是所需時間過長。VHDL測試基準(zhǔn)的優(yōu)點是其速度與平臺無關(guān),所以在某些情況下,例如前面提到的用FPGA進行信號處理的幾種情況,可以對這些情況全部或者部分地建立一個測試環(huán)境。圖1示出一個測試基準(zhǔn)邏輯結(jié)構(gòu)。設(shè)計模型接收輸入激勵(輸入信號,第一部分) ,并給出對測試基準(zhǔn)的響應(yīng)(輸出信號,第二部分) 。

(2)VHDL中的TextIO

TextIO例程是在VHDL標(biāo)準(zhǔn)中建立的,用它可以讀/寫文件,這些例程的用法如下:

Read ( ?)

Readline ( ?)

Write ( ?)

Writeline ( ?)

為了能使用這些例程,在設(shè)計程序中應(yīng)引用VHDL 的標(biāo)準(zhǔn)程序包,即在VHDL代碼的開頭應(yīng)當(dāng)包含下面的行:

use std. TextIO. all;

這些標(biāo)準(zhǔn)程序包是在進程中對行變量或列變量進行操作,然后在程序中給這些變量進行賦值或引用。

TextIO的一個很重要的應(yīng)用就是在集成電路設(shè)計或FPGA設(shè)計中的測試基準(zhǔn)中的應(yīng)用,測試基準(zhǔn)是測試方法學(xué)中一個很重要的測試和驗證工具,它提供了設(shè)計模型和外部數(shù)據(jù)的輸入輸出接口。具體來說:模型的輸入信號可以放在外部文件中,輸出信號的期望值可以放在另一個文件中,而且這個文件是以行向量方式存取,所以可以被MATLAB的系統(tǒng)級仿真軟件讀取。

在測試基準(zhǔn)中使用TextIO的方法非常靈活,也相當(dāng)簡單。調(diào)用TextIO的缺點是,與普通的VHDL代碼相比,其模擬速度往往較快。

有必要指出, TextIO的調(diào)用不能被綜合,只能用于模擬。

2.2 高效的Testbench文件編寫

(1)VHDL Testbench文件實現(xiàn)的功能

VHDL Testbench已經(jīng)成為驗證FPGA或ASIC頂層設(shè)計最典型的方法。在VHDL Testbench文件中主要完成以下任務(wù):

·例化被測試的設(shè)計單元(DUT) ;

·在Testbench文件中對測試模塊引入測試向量;

·輸出結(jié)果可以在ModelSim仿真軟件的波形窗口顯示或者作為測試結(jié)果向量保存在文本文件中;

·也可以在ModelSim仿真軟件中比較測試輸出結(jié)果和系統(tǒng)仿真期望結(jié)果,驗證設(shè)計的正確性。

(2)VHDL Testbench文件結(jié)構(gòu)

VHDL Testbench文件結(jié)構(gòu)主要包括4部分:實體和結(jié)構(gòu)體聲明、信號聲明、例化頂層設(shè)計模塊、測試進程程序。

2.3 自檢功能Testbench的程序編寫

自檢功能Testbench的實現(xiàn)是先通過MATLAB 等系統(tǒng)仿真軟件產(chǎn)生一系列期望輸出的測試向量,存放在期望輸出的向量文件中,然后在VHDL Testbench文件中編寫程序,讓程序在運行時對預(yù)設(shè)的不同運行時間間隔的實際輸出和期望輸出進行比較;如果實際輸出結(jié)果和期望輸出結(jié)果匹配,那么這個仿真結(jié)果就是正確的;如果實際輸出結(jié)果和期望輸出結(jié)果不匹配, Testbench就會在預(yù)設(shè)的時刻產(chǎn)生差異或者錯誤報告。這種功能的VHDL Testbench程序是利用VHDL語言的TextIO程序包來實現(xiàn)的。

自檢功能Testbench對同步電路的設(shè)計來說是很簡單的,因為同步電路實際輸出結(jié)果和期望輸出結(jié)果的比較可以在同一個時鐘沿或者滯后幾個時鐘周期進行。比較方式取決于具體的設(shè)計,比如存儲器I/O的Testbench,必須在每次有新數(shù)從某個地址讀出或者給某個地址寫入新數(shù)的時候檢查其結(jié)果;同樣,如果某個設(shè)計使用了很多的組合邏輯,那么期望輸出結(jié)果就要考慮組合邏輯的延時。

自檢功能Testbench是通過在特定時間對實際輸出和期望輸出進行比較而自動對仿真結(jié)果檢查錯誤,這種仿真方式特別適合中、小規(guī)模設(shè)計使用。當(dāng)數(shù)據(jù)量很大時仿真會很慢,尤其當(dāng)數(shù)據(jù)量以指數(shù)增加時,編寫Testbench會很費時和困難,這時可通過TextIO把實際輸出數(shù)據(jù)導(dǎo)出,聯(lián)合MATLAB等系統(tǒng)仿真程序?qū)PGA設(shè)計進行驗證。后面的應(yīng)用舉例就是使用這種方法來綜合驗證FPGA設(shè)計的正確性。

在VHDL Testbench文件中,仿真輸入向量數(shù)據(jù)和期望輸出向量數(shù)據(jù)都各自存放在向量數(shù)據(jù)文本文件中,VHDL語言的TextIO程序包被用作從向量文件中讀入數(shù)據(jù)和顯示錯誤信息。

3 應(yīng)用實例

在某課題數(shù)字解調(diào)部分位定時誤差估計算法設(shè)計實現(xiàn)中使用了VHDL Testbench聯(lián)合MATLAB系統(tǒng)仿真軟件,并對在FPGA中實現(xiàn)的位定時算法進行了驗證,證明該方法切實可行。

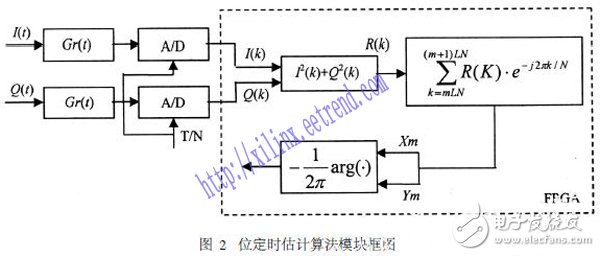

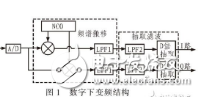

數(shù)字解調(diào)位定時估計算法框圖如圖2所示,其中虛線框內(nèi)部分是要在FPGA中實現(xiàn)和驗證的算法。按照FPGA聯(lián)合設(shè)計仿真的方法步驟,首先利用MATLAB創(chuàng)建了該算法的浮點仿真模型,并且驗證無誤。在此基礎(chǔ)上,按照以下步驟進行系統(tǒng)的設(shè)計與調(diào)試。

第一步,根據(jù)MATLAB浮點仿真模型中的數(shù)據(jù)源產(chǎn)生模塊,編寫可以產(chǎn)生定點數(shù)據(jù)(如8比特或16比特量化的有符號數(shù))的定點數(shù)據(jù)源產(chǎn)生模塊;編寫實現(xiàn)算法的各模塊的MATLAB定點代碼;運行程序,產(chǎn)生設(shè)計模塊輸入數(shù)據(jù)向量和期望輸出數(shù)據(jù)向量,并分別存儲在不同文件中。

第二步,根據(jù)位定時估計算法,用VHDL語言編程在FPGA中實現(xiàn)該算法,并根據(jù)第二節(jié)中講到的VHDL Testbench的寫法編寫對應(yīng)的測試基準(zhǔn)文件,其中包括VHDL語言的TextIO數(shù)據(jù)包和在程序中編寫讀入和寫出的程序代碼。

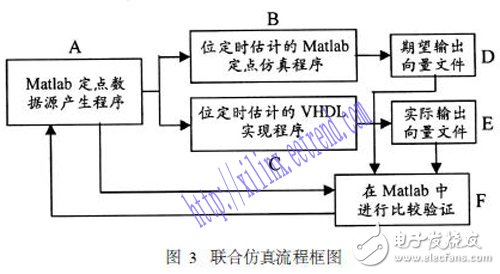

第三步,把定點數(shù)據(jù)源產(chǎn)生模塊產(chǎn)生的定點數(shù)據(jù)源分別輸入MATLAB程序和FPGA程序,如圖3所示。產(chǎn)生的輸出文件分別作為期望輸出向量文件和實際輸出向量文件。

第四步,分別對實際輸出向量文件中的輸出和對應(yīng)期望輸出向量文件中的數(shù)據(jù)進行分析驗證,如果不正確,則重新產(chǎn)生輸入數(shù)據(jù)進行聯(lián)合仿真;當(dāng)程序較大時,反復(fù)進行幾次聯(lián)合仿真,直到該模塊功能和時序仿真都正確為止。

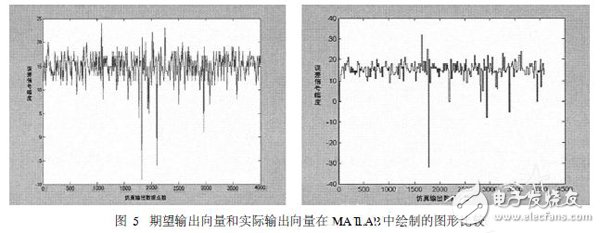

需要指出,在此仿真階段,輸入數(shù)據(jù)量化要盡可能模擬硬件實際輸入數(shù)據(jù)。圖4為MATLAB定點數(shù)據(jù)源模塊A /B產(chǎn)生的一路輸入信號,圖5為期望輸出向量文件模塊D和實際輸出向量文件模塊E在MATLAB中繪制的圖形。

從圖中可以看出, FPGA測試的輸出和MATLAB定點仿真很相似,證明了FPGA設(shè)計的正確性。

4 結(jié)束語

在電子產(chǎn)品設(shè)計領(lǐng)域已經(jīng)涌現(xiàn)出大量先進的設(shè)計技術(shù)與設(shè)計方法學(xué),并且成功地應(yīng)用在設(shè)計實踐中。這些先進的器件技術(shù)、設(shè)計技術(shù)逐步應(yīng)用在現(xiàn)代信號處理電路的研發(fā)中。隨著集成電路工藝水平的提高,現(xiàn)場可編程器件FPGA的規(guī)模和速度快速增長,這給FPGA的設(shè)計實現(xiàn)和仿真驗證帶來很大困難。尤其是在信號處理算法的FPGA實現(xiàn)中,很難把系統(tǒng)仿真和設(shè)計實現(xiàn)仿真有機結(jié)合起來;而采用Xilinx ISE結(jié)合MATLAB對數(shù)字系統(tǒng)進行聯(lián)合設(shè)計與仿真的方法是解決這一問題的有效途徑。

電子發(fā)燒友App

電子發(fā)燒友App

評論