1 前言

隨著集成電路工藝技術(shù)的不斷發(fā)展,集成電路的特征設(shè)計尺寸進入到深亞微米,芯片規(guī)模擴大到百萬門級,從計算量、后端布局布線(placement&routing,P&R)工具、內(nèi)存占用、運行時間、設(shè)計時序收斂性等方面考慮,扁平化的后端實現(xiàn)方式已變得難以承受,近年來,層次化的設(shè)計方式被廣泛采用,以實現(xiàn)大規(guī)模芯片的后端工作。

隨著芯片規(guī)模的擴大,設(shè)計復(fù)雜性的提高,設(shè)計周期成為廣泛關(guān)注的問題。設(shè)計周期主要取決于4個方面

1.設(shè)計步驟

2.各個設(shè)計步驟需要重復(fù)的次數(shù)

3.各個設(shè)計步驟的執(zhí)行時間

4.各步驟之間需要等待的時間

設(shè)計周期的縮短需要從這4個方面努力。此外,還有一個能縮短設(shè)計周期的因素:可參考設(shè)計流程。可參考設(shè)計流程定義了設(shè)計中必須執(zhí)行的設(shè)計步驟,比如,著名的rugged.script是SIS的參考綜合流程。參考設(shè)計流程讓用戶在設(shè)計初期就能夠快速開始設(shè)計,否則設(shè)計人員在設(shè)計初期需要自行作多種嘗試,決定設(shè)計流程。

本文首先介紹IBM的專用集成電路(ASIC)設(shè)計流程,然后詳細(xì)介紹層次化模塊設(shè)計中對子模塊進行快速物理設(shè)計的可重用設(shè)計流程(RLMREDOFLOW),頂層整合時對子模塊的優(yōu)化處理方法,以及該RLM設(shè)計流程的優(yōu)點。

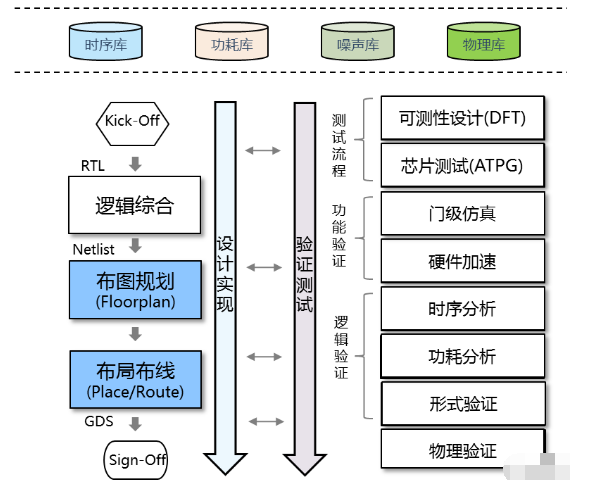

2 IBM ASIC設(shè)計流程簡介

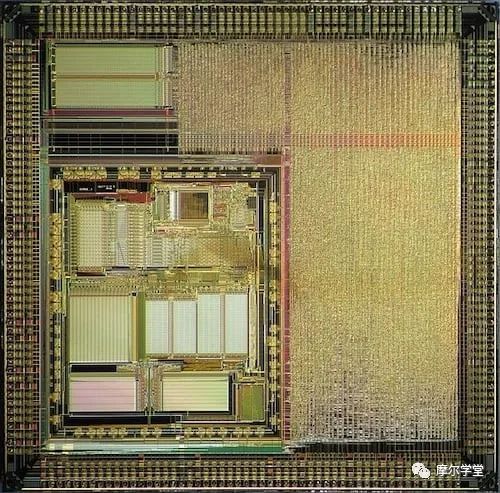

圖1描述了IBM的ASIC設(shè)計流程。在初始設(shè)計階段,系統(tǒng)工程師、前端邏輯設(shè)計工程師和后端物理實現(xiàn)工程師將一起分析設(shè)計,進行設(shè)計規(guī)劃,根據(jù)邏輯設(shè)計和物理特性劃分設(shè)計層次。層次劃分是這一階段重點要考慮的因素,將影響到綜合和布局布線時對子模塊邊界優(yōu)化的力度,子模塊之間連接關(guān)系的復(fù)雜程度等。此外,進行層次劃分時還要考慮邏輯設(shè)計的進度,如果部分子模塊的前端邏輯設(shè)計比其他子模塊早,則可以先完成這部分子模塊的物理設(shè)計。

圖1 IBMASIC設(shè)計流程

3 RLM可重用設(shè)計流程(RLM REDO FLOW)

RLM可重用設(shè)計的自動化流程涵蓋了從可測性設(shè)計(DesignForTest,DFT),物理設(shè)計到時序收斂的后端設(shè)計的各個方面,使得設(shè)計工程師可以通過一個標(biāo)準(zhǔn)化的設(shè)計流程來保證后端設(shè)計的收斂性和較少的迭代周期。我們根據(jù)后端設(shè)計中的主要設(shè)計節(jié)點把整個子模塊的后端設(shè)計分為9個部分來具體實現(xiàn)。

1)100前端處理

2)200確定物理信息

3)300為時序驅(qū)動的布局做準(zhǔn)備

4)400時序驅(qū)動的布局

5)500 時鐘插入&時鐘繞線

6)600時鐘插入后的LateMode時序收斂

7)700時鐘插入后的EarlyMode時序收斂

8)800 詳細(xì)布線

9)900交付驗收

下面具體介紹各個設(shè)計步驟。

100前端處理

主要完成RLM內(nèi)部測試結(jié)構(gòu)的生成,包括插入掃面鏈,以及測試邏輯,如邊界掃描邏輯、存儲器件的內(nèi)建自測試邏輯等。

200確定物理信息

確定RLM的一些主要物理信息,包括RLM的大小、形狀、內(nèi)部的電源網(wǎng)絡(luò)、內(nèi)部硬核的擺放、邊界上端口的位置。

1)首先定義RLM的大小、形狀,以及RLM的繞線資源,這是RLM能夠獨立于頂層設(shè)計往下走的一個起點。往往這些信息的確定是經(jīng)過多個迭代后的結(jié)果,而一旦確定之后在設(shè)計后期再要修改會極大的影響設(shè)計的可重用性。

2)在給定的RLM資源的基礎(chǔ)上進行硬核的預(yù)布局(Floorplan)工作。預(yù)布局工作可以利用工具自動完成或者采用手工擺放的方式,需要考慮到時序收斂和繞線擁塞,在設(shè)計初期會占用很大的設(shè)計時間來達到一個較好的預(yù)布局結(jié)果。

3)根據(jù)已做好的預(yù)布局結(jié)果,對硬核中端口噪聲較高的區(qū)域進行防噪聲處理。

4)分析整個RLM的時鐘結(jié)構(gòu)。

5)進行電源設(shè)計,一個獨立的RLM的電源設(shè)計需要在RLM邊界上有一個電源環(huán)的結(jié)構(gòu),以此來連接RLM內(nèi)部和頂層的電源信號。

6)自頂向下的來完成RLM的端口擺放,在后續(xù)的設(shè)計中可以根據(jù)RLM內(nèi)部設(shè)計的需求來進行一些調(diào)整。

7)在不考慮線延遲的情況下對RLM的時序進行分析,以確定時序約束的合理性,需要注意的是,要做好RLM邊界的時序約束。

300為時序驅(qū)動的布局做準(zhǔn)備

主要完成RLM端口和內(nèi)部硬核的相關(guān)邏輯的預(yù)布局,同時也可以根據(jù)設(shè)計的具體需求進行其他重要邏輯的預(yù)布局。通過前面時鐘結(jié)構(gòu)分析的結(jié)果,把設(shè)計中時鐘相關(guān)的邏輯確定出來,與時鐘相關(guān)的設(shè)計我們會放在布局之后獨立完成。

400時序驅(qū)動的布局

基于上一步的輸出,對剩下未做布局的部分進行時序驅(qū)動的布局。并對完成布局的網(wǎng)表進行時序和物理的檢查。

500時鐘插入&時鐘繞線

根據(jù)前面時鐘結(jié)構(gòu)分析的結(jié)果在做完布局的設(shè)計上進行時鐘樹的插入工作,并進行時鐘的繞線。

600時鐘插入后的LateMode時序收斂

調(diào)用優(yōu)化工具優(yōu)化setup,直到setup滿足要求

700時鐘插入后的EarlyMode時序收斂

調(diào)用優(yōu)化工具優(yōu)化hold,直到hold滿足要求

800詳細(xì)布線

對所有信號進行布線,并完成物理特性的檢查。然后提取寄生參數(shù),以及噪聲、耦合信息,進行時序分析,并調(diào)用優(yōu)化工具優(yōu)化時序。

900交付驗收

檢查RLM的布局布線、時序、功耗、噪聲等,確保RLM的設(shè)計滿足驗收要求,可以交付給頂層進行整合。

從上面的設(shè)計流程可以看出,RLM設(shè)計和頂層設(shè)計的交互主要在200和900這兩步。在RLM設(shè)計流程開始之前,芯片的頂層設(shè)計人員需要確定 RLM的在芯片上的位置、形狀(包括尺寸)、端口的位置和約束,可用于RLM布線的最高金屬層,以及RLM邊界上的時序約束。在RLM設(shè)計人員進行RLM 設(shè)計的同時,頂層的工作可以并行進行,各個RLM的設(shè)計也是可以并行的,并行度的提高大大縮短了設(shè)計周期。

4 HATS

HATS(HierarchicalAbstractTimingSignoff)是IBM層次化設(shè)計方法學(xué)的一部分,僅抽取RLM 的部分信息,用于頂層合成時的時序分析和優(yōu)化。在RLM中,影響芯片頂層時序的僅僅是輸入/輸出端口相關(guān)的路徑。而占絕大部分的時序路徑是從寄存器到寄存器的,這部分已經(jīng)在RLM中已做到時序收斂,整合到頂層時,時序信息不會發(fā)生變化,合成時可以不考慮這部分的時序。

HATS的流程如圖2所示,在完成RLM設(shè)計之后進行時序分析和網(wǎng)表分析,去除RLM內(nèi)部寄存器到寄存器的路徑,以及與此相關(guān)的時序約束,抽取 RLM信息,交給頂層使用。抽取的過程如圖3所示。

圖2HATS處理流程

圖3RLM信息的抽取

隨著芯片規(guī)模的擴大,標(biāo)準(zhǔn)單元和硬核的數(shù)量迅速增加,采用傳統(tǒng)的設(shè)計方法需要占用大量的內(nèi)存和CPU時間。而采用HATS方法,在保證驗收質(zhì)量的同時,去除了冗余的計算,大大降低了芯片合成所需的內(nèi)存和CPU時間。表1中示出了一個90nm芯片的設(shè)計實例,該芯片中包含一個重復(fù)使用了20次的 RLM,采用HATS大量節(jié)省了CPU時間和占用的內(nèi)存。

表1HATS在芯片“P”上的應(yīng)用

5 RLM快速物理設(shè)計方法的優(yōu)點

可重用的設(shè)計流程是縮短設(shè)計周期的關(guān)鍵。本文介紹的RLM快速物理設(shè)計方法,其優(yōu)點歸納起來有以下幾點:

1)IBMRLM層次化設(shè)計方法具備靈活有效的模塊劃分技術(shù);

既可針對客戶的設(shè)計要求進行有針對性的RLM劃分,也可以在頂層針對物理設(shè)計的需求進行易于物理實現(xiàn)的RLM模塊劃分,還可以綜合考慮客戶的設(shè)計要求和物理設(shè)計的需求進行RLM劃分。

2)充分考慮了功耗及噪聲對于物理設(shè)計方面的影響;

在設(shè)計初始階段就進行完備而合理的電源設(shè)計,DECAP插入,確保流片后不會因動態(tài)或靜態(tài)電壓降的問題影響芯片的正常工作。

3)充分考慮信號完整性對于芯片設(shè)計的影響;

對于關(guān)鍵的線做屏蔽,比如時鐘樹,確保在驗收階段盡可能準(zhǔn)確,減少不必要的冗余迭代。

4)完備的時序驗收分析;

在IBMRLM設(shè)計流程中既引入多CORNER,統(tǒng)計分析,同時在設(shè)計開始階段就充分考慮了電壓降對于時序的影響,盡量避免了在驗收階段由于時序問題所產(chǎn)生的迭代,并進一步確保流片后芯片在時序上的功能與設(shè)計階段分析的一致性。

5)充分考慮RLM集成在頂層的邊界問題;

對于接口處進行了合理設(shè)計確保頂層集成時易于實現(xiàn);

6)該設(shè)計方法具有很好的靈活性;

允許不同的工程師針對不同的RLM并行工作,而又可以共享利用統(tǒng)一的設(shè)計腳本,同時不影響頂層的并行評估。

7)設(shè)計方法易于更新和共享;

不同的工程師可以根據(jù)實際設(shè)計需要更新設(shè)計腳本同時共享給其他設(shè)計者。

8)易于集成;

設(shè)計完成的RLM,可以抽取信息便于頂層集成快速進行物理設(shè)計以及時序、信號完整性、功耗等方面的分析,同時在頂層驗收分析時可以繞開RLM內(nèi)部路徑,直接打平RLM,進行扁平化分析。

9)易于迭代;

當(dāng)工程師對一個RLM根據(jù)該方法進行一次評估后,確定設(shè)計需要的腳本,之后可以根據(jù)客戶更新的ECO網(wǎng)表重新調(diào)用以前的預(yù)布局,電源等信息進行快速的再評估,減少了交付市場的時間。

6 總結(jié)

對于大規(guī)模的系統(tǒng)設(shè)計,層次化的設(shè)計策略是業(yè)界的方向,特別是規(guī)模龐大的系統(tǒng)采用層次化的設(shè)計把一個大的系統(tǒng)分成子模塊,對小的子模塊設(shè)計的收斂時間更容易把握,后端工程師可以并行的處理同一個設(shè)計。IBM先進的子模塊快速設(shè)計流程提高了設(shè)計過程的可重用性,縮短了設(shè)計周期。

電子發(fā)燒友App

電子發(fā)燒友App

評論