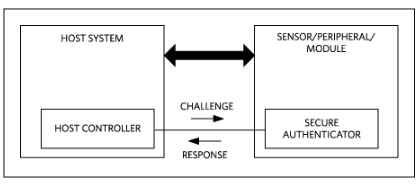

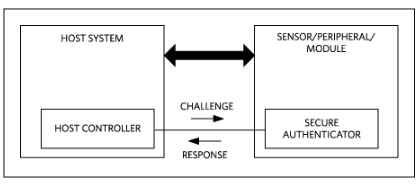

本應用筆記介紹了FPGA (現場可編程門陣列)及其如何保護系統的關鍵功能和知識產權(IP)。本文探討了IP保護的各種途徑。SHA-1質詢-響應認證被認為是最安全的方法。本文提出了一種能夠保護基于SRAM的FPGA設計IP的高性價比認證方案。介紹了DS28E01和DS28CN01器件的特性。

2013-04-07 10:18:16 5017

5017

EDA廠商加速布局IP市場意在何為?此外,FPGA供應商Altera與賽靈思 (Xilinx)也不斷通過收購累積了不少自有IP,特別是在通信領域。再聯想到MIPS最終花落Imagination

2013-04-09 09:09:43 2952

2952 可編程邏輯廠商逐步開始從可編程邏輯芯片供應商向可編程邏輯系統商完成華麗轉身,正對EDA工具供應商提出更高的要求。鑒于日益升溫的FPGA市場,EDA業者加碼布局,加速FPGA設計進程、提高驗證效率,幫助廣大工程師在短時間內進行準確無誤的設計。

2013-04-17 10:38:59 1789

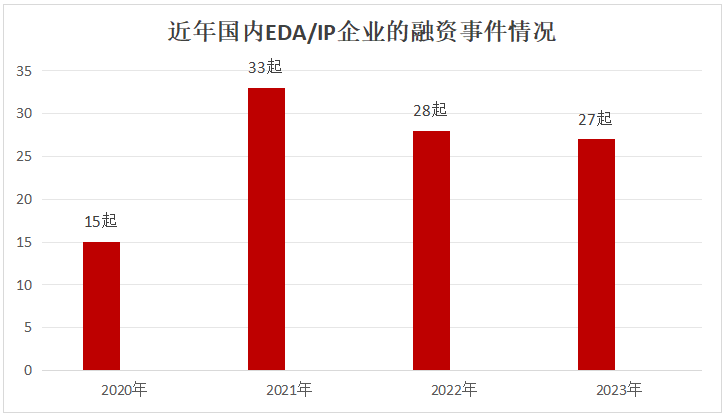

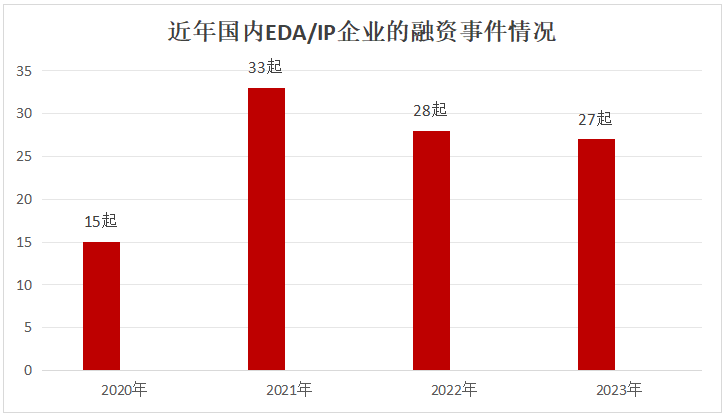

1789 企業的發展路線,無外乎都是“大魚吃小魚”,但國內EDA企業并購事件卻寥寥無幾。 ? 兼并收購少之外,近幾年國內誕生的初創EDA公司數量還反倒飛速上漲。電子發燒友也一直在收集整理國內初創EDA公司以及IP公司的融資信息。 2020年以來,國內EDA/IP行業進

2024-01-27 01:01:00 3141

3141

EDA工具用戶遍布全球,很多世界500強的企業員工很多在用Robei開發FPGA和ASIC。Robei具備可視框圖設計、面向對象的設計、編寫代碼、語法檢查、仿真與波形查看、生成Verilog代碼

2022-02-10 17:37:59

是借助于EDA開發工具,用原理圖、狀態機、布爾表達式、硬件描述語言等方法進行系統功能及算法描述,設計實現并生成編程文件,最后通過編程器或下載電纜用目標器件來實現。 FPGA器件采用邏輯單元陣列(LCA

2008-06-26 16:16:11

陣列邏輯)、gal(通用陣列邏輯)發展而來,其基本設計思想是借助于eda開發工具,用原理圖、狀態機、布爾表達式、硬件描述語言等方法進行系統功能及算法描述,設計實現并生成編程文件,最后通過編程器或下載電纜

2013-09-02 15:19:20

)發展而來,其基本設計思想是借助于EDA開發工具,用原理圖、狀態機、布爾表達式、硬件描述語言等方法進行系統功能及算法描述,設計實現并生成編程文件,最后通過編程器或下載電纜用目標器件來實現。&

2008-06-11 10:26:29

陣列邏輯)、GAL(通用陣列邏輯)發展而來,其基本設計思想是借助于EDA開發工具,用原理圖、狀態機、布爾表達式、硬件描述語言等方法進行系統功能及算法描述,設計實現并生成編程文件,最后通過編程器或下載電纜

2008-06-27 10:26:34

摘 要:EDA技術是現代電子設計技術的核心,它在現代集成電路設計中占據重要地位。隨著深亞微米與超深亞微米技術的迅速發展,FPGA設計越來越多地采用基于VHDL的設計方法及先進的EDA工具。本文詳細

2019-06-18 07:33:04

摘 要:EDA技術是現代電子設計技術的核心,它在現代集成電路設計中占據重要地位。隨著深亞微米與超深亞微米技術的迅速發展,FPGA設計越來越多地采用基于VHDL的設計方法及先進的EDA工具。本文詳細

2019-06-27 08:01:28

請問什么是EDA?那么FPGA是EDA的一種,為什么要有EDA這么一個總的概念?

2014-07-09 18:13:42

EDA說完了,再說說IP,IP對于今天SOC設計的重要性不用贅述了, Synopsys, Cadence的另一個殺手锏級的壟斷產品:接口類IP,這是每一顆SOC必不可少的東西,比如:高速SerDes

2020-06-15 08:03:59

最近出現的 FPGA設計工具和 IP有效減少了計算占用的資源,大大簡化了浮點數據通路的實現。而且,與數字信號處理器不同, FPGA能夠支持浮點和定點混合工作的 DSP數據通路,實現的性能超過

2019-08-13 06:42:48

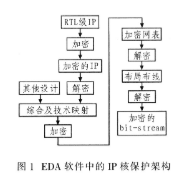

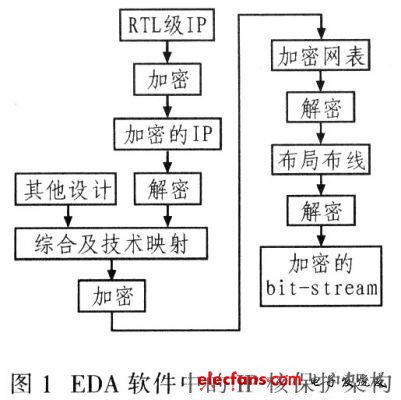

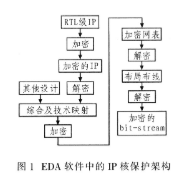

/公司電子郵件地址。 使用 EDA 和 FPGA 保護 IP 核 – 一個建議 這是一個關于使用 EDA 和 FPGA設計保護 IP 的建議。 首先,假設 EDA 軟件是可信的。第三方設計的IP核必須先

2022-02-23 12:27:05

技術已成為業界的重點。由于可重復使用的 IP 核代表了多年的設計、研究和驗證測試,因此一個關鍵問題是如何保護這項投資。眾所周知,原知識產權所有者的權利可能被有意或無意地濫用。 IP 內核一旦被設計人

2022-02-23 11:59:45

FPGA是一種可編程器件,用硬件描述語言進行編程使之擁有你所需要的功能,基本上就是EDA了吧。我這個打個比方,比如一個FPGA是一張白紙,通過EDA,在白紙上寫一個字,那么這個FPGA就只有顯示

2018-08-15 11:35:09

USB_OTG_IP核中AMBA接口的設計與FPGA實現

2012-08-06 11:40:55

附件為使用FPGA實現兩路CAN接口進行回環通信的工程文件。包含詳細的工程使用說明文檔。在小梅哥的Starter FPGA開發板上驗證通過,CAN通信使用開源的OC_CAN IP和VP230收發器實現,上層應用使用NIOS II實現,使用非常方便。

2017-09-22 22:42:14

摘要針對FFT算法基于FPGA實現可配置的IP核。采用基于流水線結構和快速并行算法實現了蝶形運算和4k點FFT的輸入點數、數據位寬、分解基自由配置。使用Verilog語言編寫,利用ModelSim

2019-07-03 07:56:53

的HDL、原理圖或狀態圖形描述,針對給定的硬件系統組件,進行編譯、優化、轉換和綜合,最終獲得我們欲實現功能的描述文件。綜合器在工作前,必須給定所要實現的硬件結構參數,它的功能就是將軟件描述與給定的硬件

2019-07-30 06:20:05

通過編程來改變內部結構的芯片。FPGA 功能實現:需要通過編程即設計硬件描述語言,經過 EDA 工具編譯、

2022-01-25 06:45:52

電機運行速度。利用數字電路或FPGA控制模擬電機電路將使系統成本和功耗大大降低。采用FPGA除了可以節能之外,還能夠將嵌入式數字信號處理(DSP)、微控制器、I/O接口等功能整合到一起,從而實現完整的家電

2021-07-14 08:30:00

你好,先生或女士我是中國學生。我已經研究FPGA一段時間了,我正在嘗試使用FPGA來實現FC協議。經過一番研究,我發現GTH可以達到FC1。但是我發現使用7系列FPGA收發器向導IP存在一些問題。我

2020-08-17 10:28:07

隨著EDA平臺服務趨于網絡化,如何通過對資源和流程的有效管理,為用戶提供更為方便安全的遠程EDA平臺調用服務,已成為關鍵問題。在FPGA開發平臺上集成了EDA工具環境,并部署SGD軟件。在實現遠程

2019-07-16 21:09:34

基于EDA技術的FPGA設計計算機應用,不看肯定后悔

2021-05-06 06:24:27

對傳統電子系統設計方法與現代電子系統設計方法進行了比較,引出了基于EDA技術的現場可編程門陣列(FPGA)電路,提出現場可編程門陣列(FPGA) 是近年來迅速發展的大規模可編程專用集成電路(ASIC

2019-11-01 07:24:42

對傳統電子系統設計方法與現代電子系統設計方法進行了比較,引出了基于EDA技術的現場可編程門陣列(FPGA)電路,提出現場可編程門陣列(FPGA)是近年來迅速發展的大規模可編程專用集成電路(ASIC

2019-09-03 06:17:15

設計。現場可編程門陣列FPGA作為集成度和復雜程度最高的可編程ASIC。是ASIC的一種新型門類,它建立在創新的發明構思和先進的EDA技術之上。

2019-10-08 08:02:17

基于FPGA的IP核8051上實現TCPIP的設計

2012-08-06 12:18:28

此提供了新的解決方案。IP核(IP Core)是具有特定電路功能的硬件描述語言程序,可較方便地進行修改和定制,以提高設計效率[3]。本文研究了基于FPGA的數據采集控制器IP 核的設計方案和實現方法,該IP核既可以應用在獨立IC芯片上,還可作為合成系統的子模塊直接調用,實現IP核的復用。

2019-07-09 07:23:09

基于Altera FPGA的IP碎片重組模塊實現Implementation of an FPGA-Based IP Reassembly Module摘要:為了更好地支持網絡安全,IP碎片重組

2008-10-07 11:00:19

多種EDA工具的FPGA設計方案

2012-08-17 10:36:17

浮點運算作為數字信號處理中最常見的運算之一,各大EDA軟件都帶有免費的浮點運算IP核。通過對IP核的生成和例化來實現浮點運算,把FPGA設計者從繁重的代碼編寫中解脫了出來,同時可以對IP核進行功能

2019-10-12 06:19:54

如何使用FPGA和IP Core實現定制緩沖管理?

2021-04-29 06:01:33

16QAM調制原理是什么?16QAM調制器的FPGA實現如何利用EDA技術來實現16QAM調制器的設計?

2021-04-15 06:00:48

什么是FPGA (現場可編程門陣列)?如何保護系統的關鍵功能和知識產權(IP)?

2019-08-26 08:25:51

嗨,我是Xilinx FPGA的新手。我該如何在FPGA中實現實時時鐘或時間和日期計數器?Xilinx是否為Artix 7提供任何RTC核心或IP?非常感謝您的建議。

2020-05-22 12:41:35

的端口號呢?我最后想實現的目標是:WIFI模塊分別分配給FPGA和手機IP地址,然后手機通過無線局域***縱FPGA.

2014-10-29 16:03:59

(IntellectualProperty)核。IP核由相應領域的專業人員設計,并經反復驗證。IP核的擁有者可通過出售IP獲取利潤。利用IP核,設計者只需做很少設計就可實現所需系統。基于IP核的模塊化設計可縮短設計周期,提高設計質量。現場

2019-09-03 07:44:22

運算作為數字信號處理中最常見的運算之一,各大EDA軟件都帶有免費的浮點運算IP核。通過對IP核的生成和例化來實現浮點運算,把FPGA設計者從繁重的代碼編寫中解脫了出來,同時可以對IP核進行功能剪裁

2019-08-29 06:50:37

怎么才能在嵌入FPGA的IP核8051上實現TCP/IP的設計?

2021-04-29 06:51:27

在EDA軟件中如何實現IP保護?在FPGA中如何實現IP保護?

2021-04-29 06:06:18

什么是IP保護?什么是IP泄露?為何會發生IP泄露?如何防止IP泄露?

2021-06-23 13:08:43

(Intellectual Property)核。IP核由相應領域的專業人員設計,并經反復驗證。IP核的擁有者可通過出售IP獲取利潤。利用IP核,設計者只需做很少設計就可實現所需系統。基于IP核的模塊化設計可縮短

2019-07-29 08:33:45

北京革新創展科技有限公司研制的B-ICE-EDA/SOPC FPGA平臺集多功能于一體,充分滿足EDA、SOPC、ARM、DSP、單片機相互結合的實驗教學,是電子系統設計創新實驗室、嵌入式系統實驗室

2022-03-09 11:18:52

EDA Tools in FPGA用于開發FPGA的EDA工具:隨著集成電路和計算機技術的發展,越來越多的公司不斷的開發出更加好用的EDA工具給廣大的技瑯人員。現在無論是軟件的開發

2009-12-05 16:10:24 0

0 基于FPGA 視頻α 混合IP 的設計(合肥工業大學微電子設計研究所 485 信箱 郵編:230009)摘要:本文闡述了視頻α 混合IP 的設計和實現方法。為了改善電路的性能, 在設計中不僅

2009-12-14 11:16:23 13

13 用硬件實現數據加密已成為信息安全的主流方向。本文提出了一種基于FPGA 的低成本的AES IP核的實現方案。該方案輪內部系統資源共用,減少了系統資源的占用。輸入密鑰與輸入數據

2010-01-06 15:11:03 10

10 本文介紹了利用EDA技術設計出與MCS-51系列微處理器指令集完全兼容的8位嵌入式微處理器芯片的IP核,并經過驗證獲得了滿意的效果。

2010-07-17 16:57:59 26

26 隨著電路復雜性的增加,越來越多的設計者開始采用擁有知識產權的、設計良好的功能模塊來加快系統開發。因此,需要相應的技術手段保護這些功能模塊不被非法復制、篡

2010-12-24 15:49:08 26

26 EDA(CPLD/FPGA)技術概述

主要術語摘要:* EDA(電子設計自動化):Electronic Design Automation* ISP(在系統可編程):In System Programmabl

2008-09-24 10:10:34 2418

2418 基于多種EDA工具的FPGA設計

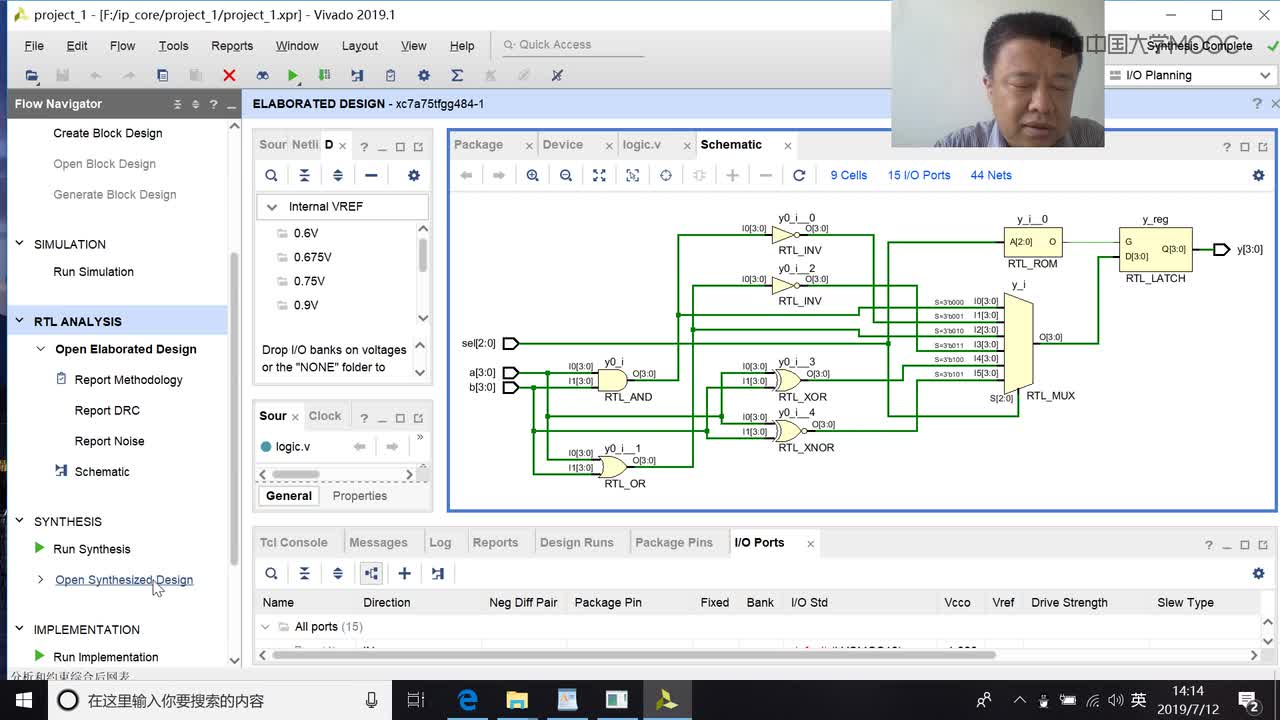

介紹了利用多種EDA工具進行FPGA設計的實現原理及方法,其中包括設計輸入、綜合、功能仿真、實現、時序仿真、配置下載等具體內容。并以實

2009-05-14 18:38:38 854

854

摘 要:在FPGA開發的各個階段,市場為我們提供了很多優秀的EDA工具。面對眼花繚亂的EDA工具,如何充分利用各種工具的特點,并規劃好各種工具的協同使用,對FPGA

2009-06-20 10:51:14 692

692 摘要:介紹了利用多種EDA工具進行FPGA設計的實現原理及方法,其中包括設計輸入、綜合、功能仿真、實現、時序仿真、配置下載等具體內容。并以實際操作介紹了

2009-06-20 11:42:45 522

522

基于NCO IP core的Chirp函數實現設計

0 引 言

IP就是知識產權核或者知識產權模塊的意思。在EDA技術和開發領域具有十分重要的作用,在半導體產業中IP定義為

2009-12-02 11:41:40 1212

1212

多種EDA工具的FPGA設計方案

概述:介紹了利用多種EDA工具進行FPGA設計的實現原理及方法,其中包括設計輸入、綜合、功能仿真、實現、時序仿真、配

2010-05-25 17:56:59 670

670

摘要:同步接口是光纖縱差保護裝置的重要組成部分,本文介紹了Cyclone II FPGA 在光纖縱差保護同步接口中的應 用,詳細地闡述了FPGA 實現光纖縱差保護同步通信接口的原理。大規模可編

2011-04-06 16:42:11 40

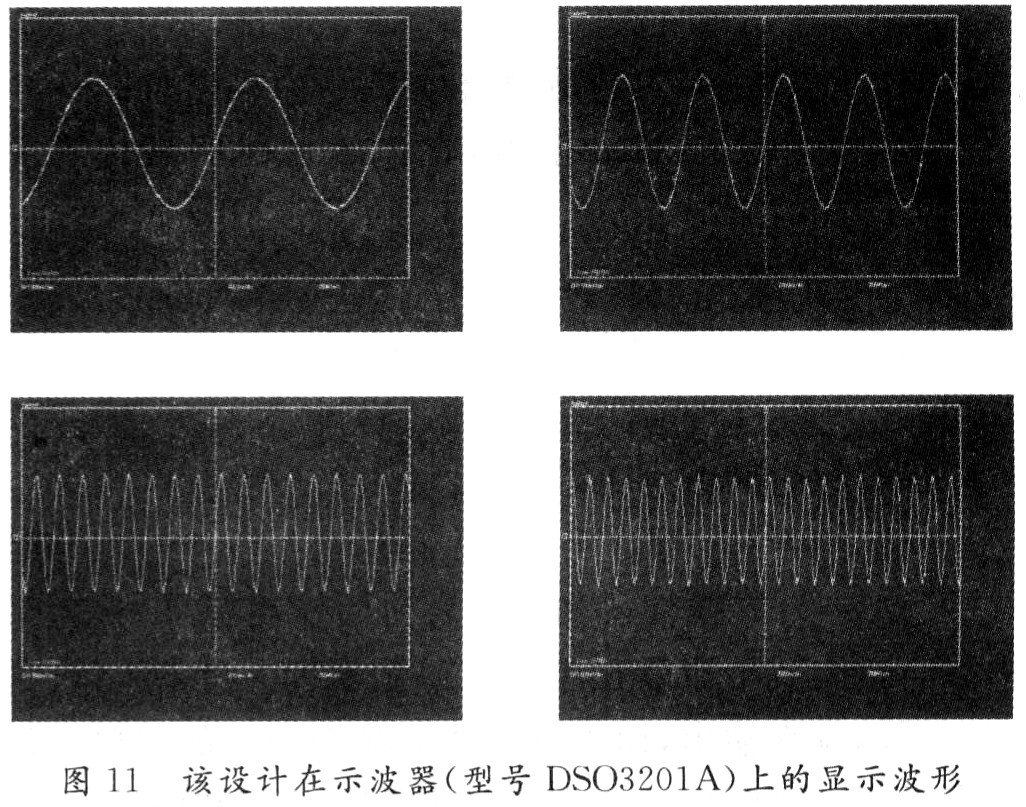

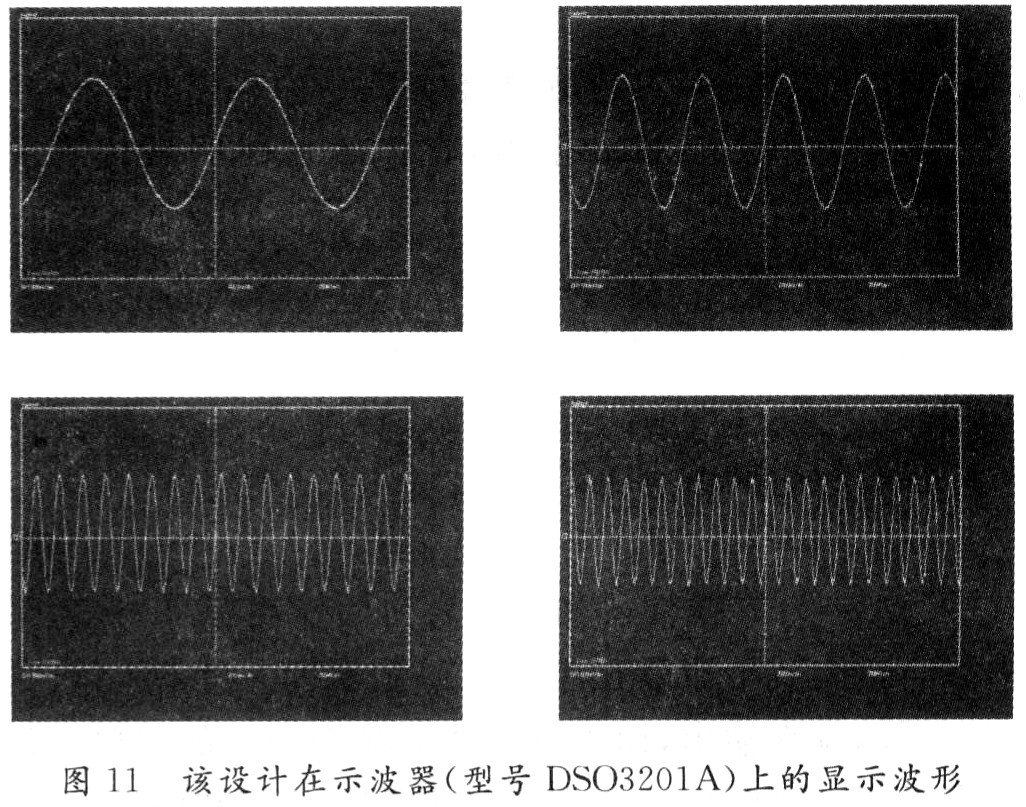

40 FPGA實現智能函數發生器設計介紹了一種基于 FPGA 的智能函數發生器的設計.采用EDA技術對此設計進行功能仿真和時序仿真,在EDA/SOPC系統開發平臺上實現程序下載,同時在示波器上觀察波形

2011-07-25 11:00:53 55

55 FPGA中IP核的生成,簡單介紹Quartus II生成IP核的基本操作,簡單實用挺不錯的資料

2015-11-30 17:36:15 11

11 利用FPGA的IP核設計和實現FFT算法

2016-05-24 14:14:47 36

36 隨著盜版和IP 剽竊的增多,人們越來越關心設計和IP 安全。對于FPGA,這需要保護比特流和器件的配置。Cyclone III LS FPGA 在低功耗平臺上實現了安全特性,幫助設計人員滿足了約束要求,確信發售IP 得到了保護的產品。

2016-09-01 17:24:53 21

21 基于FPGA的EDA綜合實驗系統設計_趙剛

2017-03-19 11:38:26 2

2 研究了TCP/IP通信協議棧在Xilinx 公司現場可編程門陣列FPGA上的實現,介紹了其軟硬件的系統組成

和原理,提出一種不需操作系統的TCP/IP協議棧的高效工作模式,并在

2017-09-04 09:24:59 9

9 研究了嵌入式TCP/IP通信協議棧在Xilinx FPGA上的實現,介紹了其軟硬件的系統組成和原理,提出一種實時操作系統上TCP/IP協議棧的高效工作模式,并在Virtex5 FPGA上移植成功。通過建立測試平臺進行數據傳輸測試,證明其具有穩定、高效的通信性能,為嵌入式設備開發提供了新的思路。

2017-11-17 17:05:01 7250

7250

本應用筆記介紹了FPGA (現場可編程門陣列)及其如何保護系統的關鍵功能和知識產權(IP)。本文探討了IP保護的各種途徑。SHA-1質詢-響應認證被認為是最安全的方法。本文提出了一種能夠保護

2017-11-22 08:20:49 2328

2328

資源。為簡化設計,降低硬件資源開銷,可以在FPGA中利用IP核實現的嵌入式微處理器來對串口數據進行處理。

2019-08-02 08:08:00 3816

3816 大部分來自對 TCP/IP 協議數據的處理,因此 CPU 的運算性能逐漸地成為高性能網絡通信發展的瓶頸。在這一形勢下,為將 CPU 從繁重的 TCP/IP 協議處理負擔中解放出來,本論文提出了一種實現 TCP/IP 協議處理的硬件解決方案,即利用 FPGA 本身所具有的密度高、速度快、小

2019-08-16 08:00:00 29

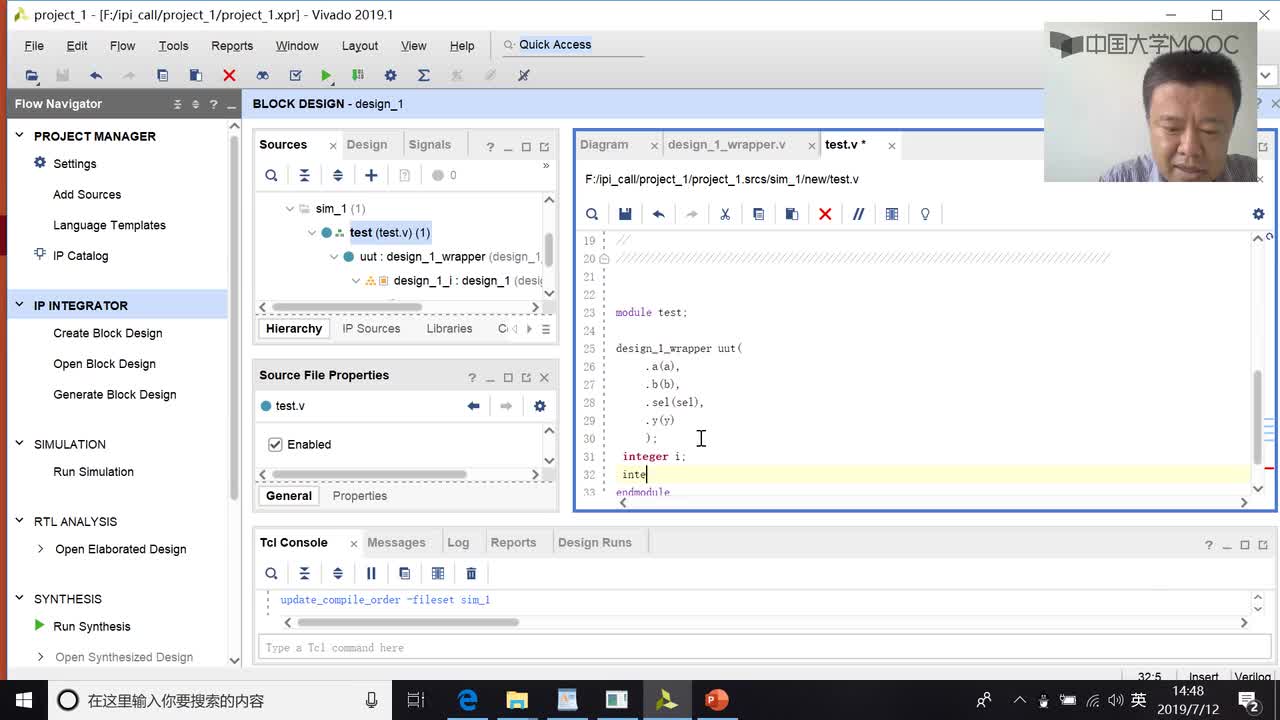

29 在EDA軟件的處理流程中,EDA軟件必須能夠正確解析設計,才能完成處理,因此設計本身對于EDA軟件是公開的。這里假定EDA軟件是可信的。具有IP核保護機制的EDA流程如圖l所示。第三方設計的IP

2020-08-10 09:51:57 763

763

? Xilinx公司的FPGA中有著很多的有用且對整個工程很有益處的IP核,比如數學類的IP核,數字信號處理使用的IP核,以及存儲類的IP核,本篇文章主要介紹BRAM ?IP

2020-12-29 15:59:39 9496

9496 的設計來例系統地介紹了利用多種EDA工具進行 FPGA協同設計的實現原理及方法近年來,隨著微電子學的迅速發展以及SoC(System on Chip ,片上系統) 技術在設計領域引起的深刻變革,EDA(Electornic Design Automatic ,電子設計自動化) 工具在系統設計中的地位愈發重要

2020-11-27 17:57:34 29

29 目前,基于IP的EDA設計流程面臨著兩大挑戰。首先,必須提供方法技術,用于測試包含IP組件設計的可靠性和質量;另一方面,必須保護IP供應商和設計者的知識產權。第三方IP核的使用確實可以提高芯片

2020-12-23 13:12:00 439

439 本文接續上一篇《FPGA雜記基礎篇》,繼續為大家分享IP例化和幾個基于FPGA芯片實現的Demo工程。IP例化IP即是一個封裝好的模塊,集成在相應的開發環境里面,以安路的TD軟件為例,不同系列的芯片集成了不同的IP模塊,可以通過軟件例化調用

2020-12-24 12:58:51 1048

1048 基于FPGA的TCP/IP協議的實現說明。

2021-04-28 11:19:47 49

49 本應用筆記介紹了設計人員如何保護其 Xilinx FPGA 實現、保護 IP 并防止附加外設偽造。設計人員可以使用本應用筆記中描述的參考設計之一來實現這種安全性。這些設計在FPGA和DeepCover安全身份驗證器之間實現了SHA-256或ECDSA質詢和響應安全認證。

2023-02-20 11:07:35 603

603

在數字電路設計中,IP 是通過EDA工具創建的,通常包括 IP 核的設計、測試、驗證、封裝、文檔管理等過程。EDA技術可以提供一系列工具和軟件,幫助設計人員在IP的設計上實現快速開發、高效驗證和重用。

2023-04-10 17:30:47 4106

4106 FPGA IP核(Intellectual Property core)是指在可編程邏輯器件(Field-Programmable Gate Array,FPGA)中使用的可復用的設計模塊或功能片段。它們是預先編寫好的硬件設計代碼,可以在FPGA芯片上實現特定的功能。

2023-07-03 17:13:28 4100

4100 電子發燒友網站提供《如何在STM32H5上通過Secure manager實現軟件IP保護.pdf》資料免費下載

2023-07-29 11:41:30 0

0 Xilinx公司的FPGA中有著很多的有用且對整個工程很有益處的IP核,比如數學類的IP核,數字信號處理使用的IP核,以及存儲類的IP核,本篇文章主要介紹BRAM IP核的使用。 BRAM是FPGA

2023-12-05 15:05:02 317

317

電子發燒友App

電子發燒友App

評論