簡介

本文介紹一種新的方法,這種方法可以從RTL設(shè)計(jì)環(huán)境中,自動(dòng)生成一個(gè)芯片設(shè)計(jì)的門級波形,而不需要事先建立門級的環(huán)境。這種新的波形生成使用降低門級功耗的方法,通過使用Springsoft 和Cambridge Silicon Radio公司已建立電力評估流程與工具的相關(guān)EDA技術(shù),完成評估與建立時(shí)間,可以從原先耗費(fèi)的幾個(gè)星期,縮減至幾個(gè)小時(shí)之內(nèi)。這項(xiàng)重大的功耗降低與設(shè)計(jì)生產(chǎn)力的增加,使得CSR分析電源功耗的特性,相比實(shí)際上可能使用的傳統(tǒng)、高效率的門級分析,在設(shè)計(jì)流程方面會(huì)顯得更早一些。此外,新方法產(chǎn)生的波形,跟那些門級仿真的波形相同(或幾乎相同)。因此,該設(shè)計(jì)可以分析并優(yōu)化迭代整個(gè)綜合設(shè)計(jì)流程,使得許多早期的檢測與電力解決問題變得更加的容易。本文主要論述:

1 功率分析與挑戰(zhàn)

2 新的自動(dòng)門級波形生成方法

3 Springsoft公司的Siloti?可視自動(dòng)化系統(tǒng)

4 分析結(jié)果

?

功率分析與挑戰(zhàn)

一個(gè)減少功耗分析成本的方法,是使用寄存器傳輸級(RTL)設(shè)計(jì)。盡管相比起門級分析,實(shí)現(xiàn)起來會(huì)更加的快捷與容易,但是受到器件合成、地點(diǎn),綜合線路等許多變數(shù)的影響,

RTL設(shè)計(jì)的準(zhǔn)確性僅僅只是有限的20%~25%。這些變量包括合成器的各種會(huì)話時(shí)間限制,以及RTL設(shè)計(jì)的實(shí)現(xiàn)選擇。例如,使用特殊電池或者時(shí)鐘樹插入技術(shù)。因此,RTL分析不足以通過微調(diào),來達(dá)到一個(gè)復(fù)雜超大規(guī)模集成電路低功耗設(shè)計(jì)的目標(biāo)。這比較適合功率特性的設(shè)計(jì)修改和跟蹤趨勢的對比。然而,這對于相關(guān)產(chǎn)品設(shè)計(jì)與生產(chǎn)來講,仍然不夠精確,特別是一些必須要符合嚴(yán)格電源規(guī)格的特殊設(shè)計(jì)。

有幾種方法可以用來精確地估計(jì)功率消耗。一種共同的做法是在同一路由表中,通過發(fā)送端和路由表結(jié)合使用,全注釋模擬來估計(jì)真實(shí)情景,使用標(biāo)準(zhǔn)或非標(biāo)準(zhǔn)延遲格式(SDF)。在這種方法中,所有的時(shí)鐘樹和導(dǎo)線電容應(yīng)被重視納入為最準(zhǔn)確的估計(jì)方式,這種方法需要造就門級的設(shè)計(jì)環(huán)境。

門級波形生成的挑戰(zhàn)

生成一個(gè)門級仿真環(huán)境是一項(xiàng)非常需要努力的任務(wù),因?yàn)樗鼈兊拿诤铣膳c仿真的不匹配。相比使用模擬接口,合成通常表現(xiàn)在不同的RTL接口上。由于在合成過程中,信號(hào)不能保持完整性,匹配新接口的過程,將是一項(xiàng)繁瑣、費(fèi)時(shí)的手工任務(wù)。此外,在往后的端點(diǎn)和路由上,該接口可以完全改變,以使其工作在更高的效率上。

此外,這種傳統(tǒng)生成波形的方法,總需要模擬運(yùn)行的時(shí)間從零開始。這不僅導(dǎo)致了較長的模擬運(yùn)行時(shí)間,也使得為設(shè)計(jì)團(tuán)隊(duì)找到周期相關(guān)的功率估計(jì)任務(wù)更為必要。鑒于門級傳輸水平(GTL)波形文件的龐大與復(fù)雜,手動(dòng)定位周期相關(guān)將是非常耗費(fèi)時(shí)間的。

由于長時(shí)間的模擬運(yùn)行,大量的匹配和調(diào)試命名,并努力找到功率相關(guān)所需的模擬周期,只有在項(xiàng)目的最后階段,許多設(shè)計(jì)小組才進(jìn)行門級電路的仿真。這在優(yōu)化功率效率流程上顯得太晚了。事實(shí)上,許多設(shè)計(jì)團(tuán)隊(duì)在完成項(xiàng)目之前放棄了功率分析階段——他們僅僅只是時(shí)間用完了。

新的自動(dòng)門級波形生成方法

新方法由英國CSR公司和思源科技公司共同制定

1 自動(dòng)生成準(zhǔn)確門級波形;

2 使設(shè)計(jì)團(tuán)隊(duì)在RTL環(huán)境中關(guān)聯(lián)和分析結(jié)果,消除使用的必要性,并提出門級設(shè)計(jì)環(huán)境;

3 消除必要性,并從零開始為每個(gè)功率做運(yùn)行分析;

4 保持建立功率估計(jì)方法和工具流程沒有變化。

該設(shè)計(jì)通過結(jié)合了思源已有Siloti可視自動(dòng)化系統(tǒng)和使用CSR腳本定期合成、端點(diǎn)、及路由工具,生成的CSR地圖文件。類似某些仿真與FPGA設(shè)計(jì)工具,這項(xiàng)可視自動(dòng)化系統(tǒng)可以從基本信號(hào)波形中提取全波形(觸發(fā)器輸入)。此外,在RTL中,設(shè)計(jì)將映射每個(gè)門級觸發(fā)器到相應(yīng)的源觸發(fā)器上。功能的結(jié)合是為了從RTL中提取必要的信號(hào)。這樣的結(jié)果是,一個(gè)門級的波形跟RTL仿真派生出來的波形基本上是相同的(或者是幾乎相同)。因此,它可以通過表單項(xiàng)的每個(gè)端口獲取切換速率——這也正是所需數(shù)據(jù)的準(zhǔn)確的功率估計(jì)。

這種自動(dòng)生成活動(dòng)端口數(shù)據(jù)大大地減少了生成門級波形上的時(shí)間和精力,并消除了必須的門級電路測試環(huán)境。在波形產(chǎn)生后,使用CSR已有功率估算流程進(jìn)行能耗分析,這種新的估算方法無需改變波形。

使用新的估計(jì)方法,門級波形可以根據(jù)相應(yīng)的范圍和時(shí)間域產(chǎn)生波形,消除了模擬運(yùn)行需要從零開始生成的限制。該方法也可以用于驗(yàn)證運(yùn)行于內(nèi)部驅(qū)動(dòng)設(shè)計(jì)的測試部分。比如,用CPU默認(rèn)頭文件代替CPU RTL電路。

可視自動(dòng)化技術(shù)

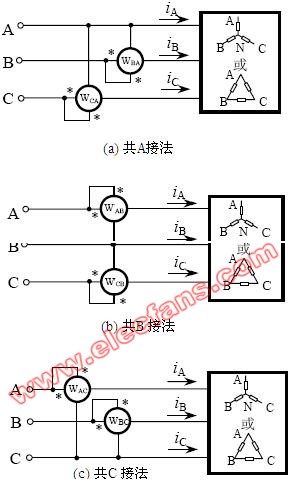

新方法采用的兩個(gè)主要工具的功能——“假設(shè)重復(fù)”和“相關(guān)性”——和RTL模擬波形作為輸入激源,重新運(yùn)行門級模擬。

“假設(shè)重復(fù)”與先前生成的波形數(shù)據(jù),作為輸入激源,重新模擬用戶指定的設(shè)計(jì)。用戶還可以為模擬指定時(shí)間窗。

“相關(guān)性”從RTL映射信號(hào)到門級,反之亦然。

在功率分析上,該技術(shù)用于映射RTL信號(hào)波形到門級波形,以便為了更好的重復(fù)模擬驅(qū)動(dòng)。

上述波形數(shù)據(jù)(被稱為快速信號(hào)數(shù)據(jù)庫FSDB),是思源Verdi可視自動(dòng)化調(diào)試系統(tǒng)的一項(xiàng)開放的部分,并且它已得到許多第三方工具的支持。

正如新方法要求的CSR功率估計(jì)方法無需改變,使得可視自動(dòng)化技術(shù)要求CSR工具流也無需作出改變。當(dāng)模擬繼續(xù)使用諸如Cadence的統(tǒng)一模擬器時(shí),流程繼續(xù)使用傳統(tǒng)物理設(shè)計(jì)工具,例如Synopsys設(shè)計(jì)編譯器,IC編譯器,PrimeTime PX工具等。

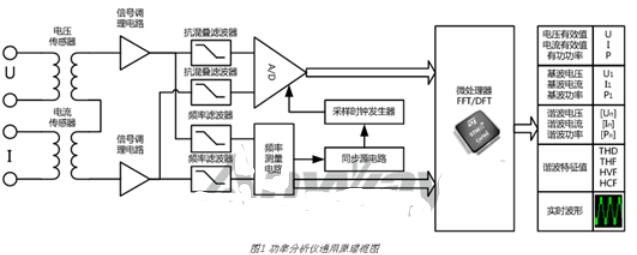

可視自動(dòng)化工具輸入、映射文件生成和執(zhí)行流程如下所示:

工具輸入

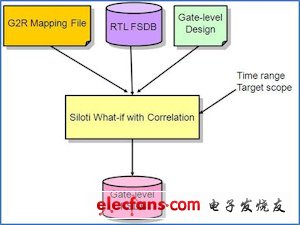

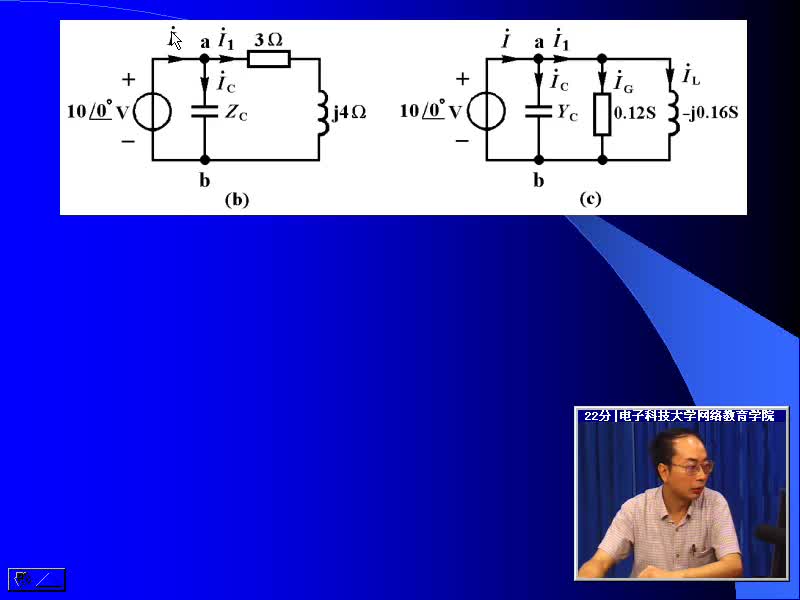

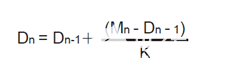

該工具使用下面的輸入數(shù)據(jù)來生成門級波形(參見圖1):

1 RTL模擬仿真中的快速信號(hào)數(shù)據(jù)庫FSDB、波形及其范圍,必須重新生成。

2 從每個(gè)必要的門級信號(hào)到RTL快速信號(hào)數(shù)據(jù)中相應(yīng)的RTL信號(hào)的門級到RTL的映射文件。在重復(fù)模擬實(shí)驗(yàn)中,用戶還可以匹配信號(hào)到一個(gè)固定的恒定值上。

3 門級文件列表包含了編譯門級網(wǎng)表命令(除去任何測試)。該文件也包含了“定義”和其他任何的編譯選項(xiàng)。

4 配置文件指定用戶設(shè)置“假設(shè)重復(fù)”運(yùn)行,關(guān)鍵參數(shù)包括如下:

(1)從模擬運(yùn)行、到門級波形生成的門級設(shè)計(jì)范圍;

(2)開始和結(jié)束時(shí)間的門級波形時(shí)間范圍;

(3)模擬與仿真編譯腳本和設(shè)置;

(4)模擬與仿真運(yùn)行腳本和設(shè)置;

(5)SDF文件和路徑使用,其他。

圖片1:工具輸入流

映射文件生成

由CSR公司開發(fā)的映射文件生成工具,包含了觸發(fā)器映射和輸入映射。

觸發(fā)器映射可以從等價(jià)輸出檢查工具,或者合成/地點(diǎn),線路工具輸出衍生。

當(dāng)門級層次結(jié)構(gòu)確定以后,門級輸入映射將會(huì)是一件簡單的事情。當(dāng)門級層次沒有確定時(shí),把輸入映射到最高層次,就像確定一個(gè)高層次的物理設(shè)計(jì)宏,這是非常必要的。在這樣的情況下,足以進(jìn)行時(shí)鐘映射、可測試性設(shè)計(jì)(DFT)信號(hào),例如內(nèi)置自測試(BIST),掃描,以及具體的控制信號(hào)。映射驅(qū)動(dòng)所有適當(dāng)?shù)臅r(shí)鐘和控制輸入所需要的范圍。它同時(shí)也失去了某些接口數(shù)據(jù),比如存儲(chǔ)輸出直到第一個(gè)樣本,并從輸入采樣到第一個(gè)采樣觸發(fā)器間切換信息。然而,這一損失對總功率估計(jì)的影響可以忽略不計(jì)。

執(zhí)行流程

執(zhí)行流程有三個(gè)階段:提取、編譯和仿真。

在提取階段,工具使用輸入文件和用戶設(shè)置產(chǎn)生兩項(xiàng)主要組成部分:

新的設(shè)計(jì)實(shí)驗(yàn)源文件進(jìn)行設(shè)計(jì)提取選定的范圍,這是DUT的重復(fù)模擬實(shí)驗(yàn)。

新的測試文件,使用RTL仿真結(jié)果(FSDB)作為輸入刺激,在重復(fù)模擬中提取DUT。

然后,設(shè)計(jì)準(zhǔn)備編譯和重復(fù)模擬。工具會(huì)自動(dòng)驅(qū)動(dòng)編譯,并執(zhí)行仿真任務(wù)。使用通用仿真工具,比如Synopsys公司的VCS和Cadence的統(tǒng)一模擬器(IUS),在模擬設(shè)計(jì)編譯階段產(chǎn)生波形。

在一定時(shí)間和范圍內(nèi)生成的門級波形后,它可以使用任何流行的功率估計(jì)方法處理。如果一項(xiàng)給定的功率估計(jì)方法不能接受FSDB作為直接輸入,還可以通過轉(zhuǎn)換FSDB輸出至其他格式,例如VCD、SAIF文件,這些格式可使用在任何的功率估計(jì)方法中。

分析結(jié)果

準(zhǔn)確性

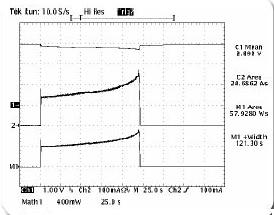

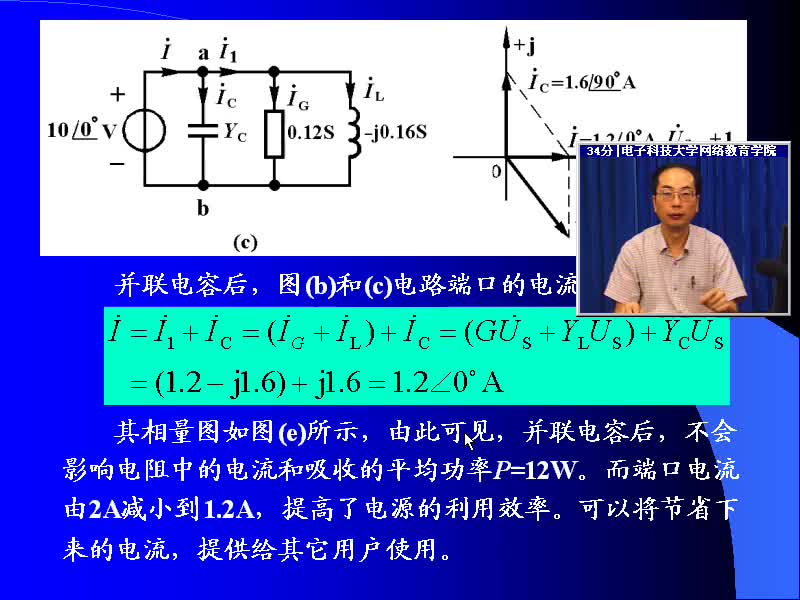

新的波形產(chǎn)生結(jié)果,與傳統(tǒng)仿真生成的門級波形進(jìn)行比較。新流程產(chǎn)生的門級波形,與傳統(tǒng)方法生成的波形,相同或者幾乎相同。下面對五個(gè)案例進(jìn)行分析和比較,結(jié)果如下:

1 在設(shè)計(jì)中從零時(shí)間開始,包括記憶體,使用新的流程設(shè)計(jì),導(dǎo)致產(chǎn)生與傳統(tǒng)零延遲門級流程完全相同的波形。

2 重復(fù)之前的設(shè)計(jì)比較,包括記憶體部分,并取得相同的實(shí)驗(yàn)結(jié)果。

3 在設(shè)計(jì)中使用新的流程,包括記憶體部分,在一個(gè)特定的時(shí)間點(diǎn)(非零點(diǎn))產(chǎn)生波形,隨著具體時(shí)間模擬傾斜波形,產(chǎn)生與門級仿真相同的波形。

4 與記憶體部分,一起重復(fù)之前的設(shè)計(jì)比較,關(guān)于門級仿真新流程,幾乎實(shí)現(xiàn)了數(shù)據(jù)100%的準(zhǔn)確性。兩者唯一的區(qū)別是,內(nèi)存輸出到第一個(gè)樣本的路徑不同。但這點(diǎn)小差異并沒有影響功率分析結(jié)果。在添加硬件宏輸出后,比如內(nèi)存數(shù)據(jù)輸出引腳,到相應(yīng)的映射文件,這種方法也可以取得100%準(zhǔn)確性。

5 在設(shè)計(jì)中使用新的流程,驅(qū)動(dòng)唯一必要的輸入時(shí)鐘,并測試模式引腳與特殊控制,對所有的“觸發(fā)器-觸發(fā)器”路徑產(chǎn)生與門級模擬相同的波形。只有從輸入到第一個(gè)樣本之間的路徑是不相關(guān)的。在一個(gè)大型設(shè)計(jì)中會(huì)包含許多這樣的路徑,路徑的相關(guān)性可高達(dá)99%。這種情況是典型的,新一代功率估計(jì)選擇方法,使用post-place和路由表生成最終波形。

表現(xiàn)結(jié)果

實(shí)例所產(chǎn)生的門級波形結(jié)果和功率性能估計(jì)包括:

1 門級環(huán)境生成的波形塊(預(yù)置端點(diǎn)和線路)約有1.4百萬個(gè)位置點(diǎn),1000個(gè)輸入端口,100us(大概40K個(gè)周期)大約花費(fèi)60分鐘的時(shí)間。總功率估計(jì)時(shí)間為2個(gè)小時(shí),包括加載數(shù)據(jù)庫到PrimeTime PX,生成映射文件,運(yùn)行工具,從門級波形產(chǎn)生SAIF文件,并使用PrimeTime計(jì)算功率消耗。

2 一個(gè)時(shí)鐘波形大約生成1.6百萬個(gè)位置元素:400us(大概150K個(gè)周期)在90分鐘內(nèi)完成。整個(gè)功率估計(jì)流程大約執(zhí)行2.5個(gè)小時(shí)。

3 大約花一個(gè)小時(shí),時(shí)鐘波形產(chǎn)生約1.4百萬個(gè)位置元素。利用 “點(diǎn)- 路徑”網(wǎng)表和使用Specman存根代替若干CPU在RTL環(huán)境下執(zhí)行生成的RTL FSDB庫進(jìn)行發(fā)送。在前一波形塊中,“點(diǎn) – 路徑”網(wǎng)表的功率估計(jì),在三個(gè)項(xiàng)目周期后被棄用。因?yàn)轫?xiàng)目要求STUB接口和“點(diǎn) – 路徑”接口的匹配屬于過渡階段。

更多的自動(dòng)化

設(shè)計(jì)團(tuán)隊(duì)可以進(jìn)一步自動(dòng)化和擴(kuò)展新門級波形生成分析能力,通過使用思源的verdi3自動(dòng)化調(diào)試系統(tǒng)進(jìn)入流程,然后使用Verdi互操作性應(yīng)用程序(VIA)平臺(tái)。上述整個(gè)流程可以與Verdi的圖形用戶界面和數(shù)據(jù)庫基礎(chǔ)集成。以便于從下游功率估計(jì)工具包含結(jié)果。這使得設(shè)計(jì)團(tuán)隊(duì)把相關(guān)功率特性與具體的設(shè)計(jì)實(shí)例關(guān)聯(lián)起來,從而大大地提高了可視化與精度的分析。

電子發(fā)燒友App

電子發(fā)燒友App

評論