電子發(fā)燒友網(wǎng): 本文主要為大家淺析Altera公司 28nm Stratix V FPGA。Altera公司公布了其28nm Stratix V FPGA的性能參數(shù)指標,具體參數(shù)如下表所示。該款芯片發(fā)售日期為2011年一季度。 與Altera St

2012-08-10 10:07:04 7384

7384 賽靈思在其FPGA中提供了豐富的時鐘資源,大多數(shù)設(shè)計人員在他們的FPGA設(shè)計中或多或少都會用到。不過對FPGA設(shè)計新手來說,什么時候用DCM、PLL、PMCD和MMCM四大類型中的哪一種,讓他們頗為困惑。本文為您解惑......

2013-07-23 09:25:53 19707

19707

7系列FPGA擁有豐富的時鐘資源。各種緩沖器類型、時鐘輸入管腳和時鐘連接,可以滿足許多不同的應用需求。選擇合適的時鐘資源可以改善布線、性能和一般FPGA資源利用率。BUFGCTRL(最常用作BUFG

2022-07-22 09:40:25 2475

2475 7系列FPGA時鐘資源通過專用的全局和區(qū)域I/O和時鐘資源管理符合復雜和簡單的時鐘要求。時鐘管理塊(CMT)提供時鐘頻率合成、減少偏移和抖動過濾等功能。非時鐘資源,如本地布線,不推薦用于時鐘功能。

2022-07-28 09:07:34 1276

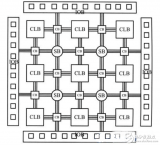

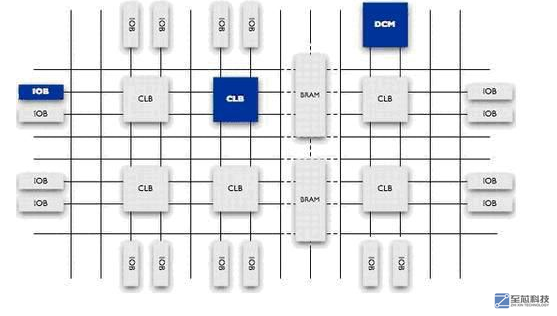

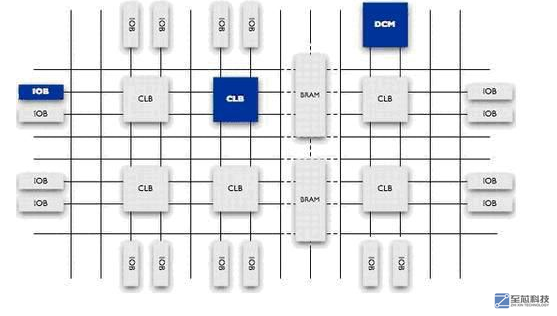

1276 每一個系列的FPGA都有其相應的內(nèi)部結(jié)構(gòu)),FPGA芯片主要由6部分完成,分別為:可編程輸入輸出單元、基本可編程邏輯單元、完整的時鐘管理、嵌入塊式RAM、豐富的布線資源、內(nèi)嵌的底層功能單元和內(nèi)嵌專用硬件模塊。

2022-10-25 09:01:05 1817

1817 FPGA CPLD同步設(shè)計若干問題淺析摘要:針對FPGA/CPLD同步設(shè)計過程中一些容易被忽視的問題進行了研究,分析了問題產(chǎn)生的原因、對可靠性的影響,并給出了解決方案。關(guān)鍵詞:FPGA/CPLD

2009-04-21 16:42:01

,實際上每一個系列的FPGA都有其相應的內(nèi)部結(jié)構(gòu)),FPGA芯片主要由6部分完成,分別為:可編程輸入輸出單元、基本可編程邏輯單元、完整的時鐘管理、嵌入塊式RAM、豐富的布線資源、內(nèi)嵌的底層功能單元

2021-07-29 09:41:30

是整個FPGA學習生涯的必經(jīng)之路。我個人建議在選擇FPGA的時候,應該抓住如下幾個原則:1、選擇主流廠家的流行的型號,這樣更容易獲取學習資源。選擇一家主流公司的FPGA芯片:在國內(nèi)目前來說,主流

2020-09-04 10:10:49

芯片。

內(nèi)部互聯(lián)線(Interconnects):用于連接上述的各種資源。

而ASIC是為特定應用定制的硬件電路,其設(shè)計和制造過程是一次性的。因此,ASIC的資源與FPGA的對應關(guān)系并不直接。

在一些

2024-02-22 09:52:22

、FPGA一般觸發(fā)器資源比較豐富,而CPLD組合邏輯資源更豐富。6、FPGA和CPLD的組成:FPGA基本有可編程I/O單元、基本可編程邏輯單元、嵌入式塊RAM、豐富的布線資源、底層嵌入功能單元和內(nèi)嵌專用硬核

2020-10-21 10:32:50

主要區(qū)別有二點:1、FPGA基本有可編程I/O單元、基本可編程邏輯單元、嵌入式塊RAM、豐富的布線資源、底層嵌入功能單元和內(nèi)嵌專用硬核等6部分組成。CPLD的結(jié)構(gòu)相對比較簡單,主要由可編程I/O單元

2018-08-28 09:15:53

和DSP)的硬核(ASIC型)模塊。FPGA芯片主要由7部分完成,分別為:可編程輸入輸出單元、基本可編程邏輯單元、完整的時鐘管理、嵌入塊式RAM、豐富的布線資源、內(nèi)嵌的底層功能單元和內(nèi)嵌專用硬件模塊。1.

2014-08-16 10:32:45

FPGA由6部分組成,分別為可編程輸入/輸出單元、基本可編程邏輯單元、嵌入式塊RAM、豐富的布線資源、底層嵌入功能單元和內(nèi)嵌專用硬核等。

2019-05-24 06:15:05

,利用芯片內(nèi)部的各種連線資源,合理正確地連接各個元件。目前,FPGA的結(jié)構(gòu)非常復雜,特別是在有時序約束條件時,需要利用時序驅(qū)動的引擎進行布局布線。布線結(jié)束后,軟件工具會自動生成報告,提供有關(guān)設(shè)計中各部分

2023-12-31 21:15:31

,實際上每一個系列的FPGA都有其相應的內(nèi)部結(jié)構(gòu)),FPGA芯片主 要由6部分完成,分別為:可編程輸入輸出單元、基本可編程邏輯單元、完整的時鐘管理、嵌入塊式RAM、豐富的布線資源、內(nèi)嵌的底層功能單元和內(nèi)嵌

2017-05-09 15:10:02

單元、基本可編程邏輯單元、完整的時鐘管理、嵌入塊式RAM、豐富的布線資源、內(nèi)嵌的底層功能單元和內(nèi)嵌專用硬件模塊。圖1-1 FPGA芯片的內(nèi)部結(jié)構(gòu)每個模塊的功能如下:1. 可編程輸入輸出單元(IOB

2023-05-30 20:53:24

。

3、時鐘偏差

時鐘偏差(Clock Skew)表示在同一個時鐘域內(nèi)時鐘信號到達各個寄存器用時的差異。時鐘信號在FPGA芯片中也是需要走線的,所以也存在布線延遲。

時鐘的不確定性,就是由時鐘抖動

2023-11-15 17:41:10

工藝的發(fā)展,FPGA登上了歷史舞臺成為主角,他內(nèi)部資源豐富,不管是時序邏輯還是組合邏輯都很多。它是作為專用集成電路領(lǐng)域中的一種半定制電路而出現(xiàn)的,既解決了定制電路的不足,又克服了原有可編程器件門電路

2020-06-23 15:04:14

它資源中的過程。 (3)布局與布線:布局是指從映射取出定義的邏輯和輸入輸出塊,并把它們分配到FPGA內(nèi)部的物理位置,通常基于某種先進的算法,如最小分割、模擬退火和一般的受力方向張弛等來完成;布線是指利用

2018-08-29 09:59:08

請問FPGA的資源使用如何評估?

2024-02-22 09:55:53

一、FPGA的基本結(jié)構(gòu) FPGA由6部分組成,分別為可編程輸入/輸出單元、基本可編程邏輯單元、嵌入式摸塊RAM、豐富的布線資源、底層嵌入式功能單元和內(nèi)嵌專用硬核等。 每個單元簡介如下: 1.

2019-09-24 11:54:53

一、FPGA的基本結(jié)構(gòu) FPGA由6部分組成,分別為可編程輸入/輸出單元、基本可編程邏輯單元、嵌入式摸塊RAM、豐富的布線資源、底層嵌入式功能單元和內(nèi)嵌專用硬核等。 每個單元簡介如下: 1.

2016-07-16 15:32:39

一、FPGA的基本結(jié)構(gòu) FPGA由6部分組成,分別為可編程輸入/輸出單元、基本可編程邏輯單元、嵌入式摸塊RAM、豐富的布線資源、底層嵌入式功能單元和內(nèi)嵌專用硬核等。 每個單元簡介如下: 1.

2016-08-23 10:33:54

一、FPGA的基本結(jié)構(gòu) FPGA由6部分組成,分別為可編程輸入/輸出單元、基本可編程邏輯單元、嵌入式摸塊RAM、豐富的布線資源、底層嵌入式功能單元和內(nèi)嵌專用硬核等。 每個單元簡介如下: 1.

2016-09-18 11:15:11

一、FPGA的基本結(jié)構(gòu) FPGA由6部分組成,分別為可編程輸入/輸出單元、基本可編程邏輯單元、嵌入式摸塊RAM、豐富的布線資源、底層嵌入式功能單元和內(nèi)嵌專用硬核等。 每個單元簡介如下: 1.

2016-10-08 14:43:50

FPGA由6部分組成,分別為可編程輸入/輸出單元、基本可編程邏輯單元、嵌入式塊RAM、豐富的布線資源、底層嵌入功能單元和內(nèi)嵌專用硬核等。

2019-09-26 06:11:33

。4.布局布線CAD Fitter工具決定網(wǎng)表中定義的LEs如何布置成FPGA芯片中的實際LEs。5.時序分析分析已布局布線電路中的不同路徑的傳播延遲,用以指示所需電路的性能。6.時序仿真測試已布局布線

2017-10-24 14:59:23

上,這往往需要在速度最優(yōu)和面積最優(yōu)之間進行選擇。布線是指根據(jù)布局的拓撲結(jié)構(gòu),利用芯片內(nèi)部的各種連線資源,合理正確地連接各個元件。目前,FPGA的結(jié)構(gòu)非常復雜,特別是在有時序約束條件時,需要利用時序驅(qū)動

2020-11-30 16:22:59

:將邏輯網(wǎng)表配置到具體的FPGA芯片上,需要在速度和面積之間進行選擇 7、時序仿真:后仿真,是將布局布線延時反標注到設(shè)計網(wǎng)表中 8、板級仿真與驗證:應用于高速電路,對高速系統(tǒng)信號完整性,電磁干擾等特征進行分析 9、芯片編程與調(diào)試:產(chǎn)生位數(shù)據(jù)流文件,將編程數(shù)據(jù)下載到FPGA芯片中

2020-12-04 15:28:09

FPGA芯片基本由6個部分組成:IOB可編程輸入輸出單元;CLB基本可編程邏輯單元;嵌入式RAM;豐富的布線資源;底層嵌入式功能單元:PLL/DCM/CPU/DSP/乘法器等;內(nèi)嵌專用硬核:SERDES等;

2019-08-02 09:09:49

/O的靜態(tài)電流,時鐘管理和其它部分電路的靜態(tài)功耗l設(shè)計動態(tài)功耗:FPGA內(nèi)設(shè)計正常啟動后,設(shè)計的功耗;這部分功耗的多少主要取決于芯片所用電平,以及FPGA內(nèi)部邏輯和布線資源的占用顯而易見,前兩部分

2014-08-21 15:31:23

電容的布局布線 - 電源是不是必須從濾波電容進入芯片管腳(PCB設(shè)計十大誤區(qū)-1)

2021-12-27 06:02:41

我現(xiàn)在用fpga掛4個DAC,其中三個DAC與fpga之間的布線(指的是數(shù)據(jù)傳輸線)長度為100,另一個DAC與FPGA之間的布線長度為400,問題:fpga同時給4路DAC發(fā)送數(shù)據(jù),在4路DAC的輸出端數(shù)據(jù)是同步輸出的嗎?

2017-04-21 08:57:04

你好。我正在寫一篇技術(shù)論文和需要知道LUT和Kintex 7 FPGA芯片中的FF所需的資源。資源可以是晶體管數(shù)量,柵極數(shù),芯片面積大小等等。我在一個網(wǎng)站上聽說LUT需要2.5倍的“FPGA門”,但

2019-02-27 13:49:58

前言FPGA芯片主 要由6部分完成,分別為:可編程輸入輸出單元(IOB)基本可編程邏輯單元(configurable logic block,CLB) 完整的時鐘管理嵌入塊式RAM豐富的布線資源內(nèi)嵌

2021-07-26 06:54:01

,此時只受限于芯片內(nèi)塊RAM 的數(shù)量,而不再受上面兩條原則約束。5. 豐富的布線資源布線資源連通 FPGA 內(nèi)部的所有單元,而連線的長度和工藝決定著信號在連線上的驅(qū)動能力和傳輸速度。FPGA 芯片內(nèi)部

2012-03-08 11:03:49

關(guān)于FPGA芯片資源介紹不看肯定后悔

2021-09-18 08:53:05

NoC 去替代傳統(tǒng)的邏輯去做高速數(shù)據(jù)傳輸和數(shù)據(jù)總線管理。· 增加了 FPGA 的布線資源,對于資源占用很高的設(shè)計有效地降低布局布線擁塞的風險。· 實現(xiàn)真正的模塊化設(shè)計,減小 FPGA 設(shè)計人員調(diào)試

2020-09-07 15:25:33

在如何使用Arm-2D在小資源Cortex-M處理器芯片中實現(xiàn)圖形界面中,效果器顯示效果和MDK調(diào)試代碼怎么關(guān)聯(lián)?模擬器不是單獨運行在PC環(huán)境里的嗎?

2022-08-26 14:40:46

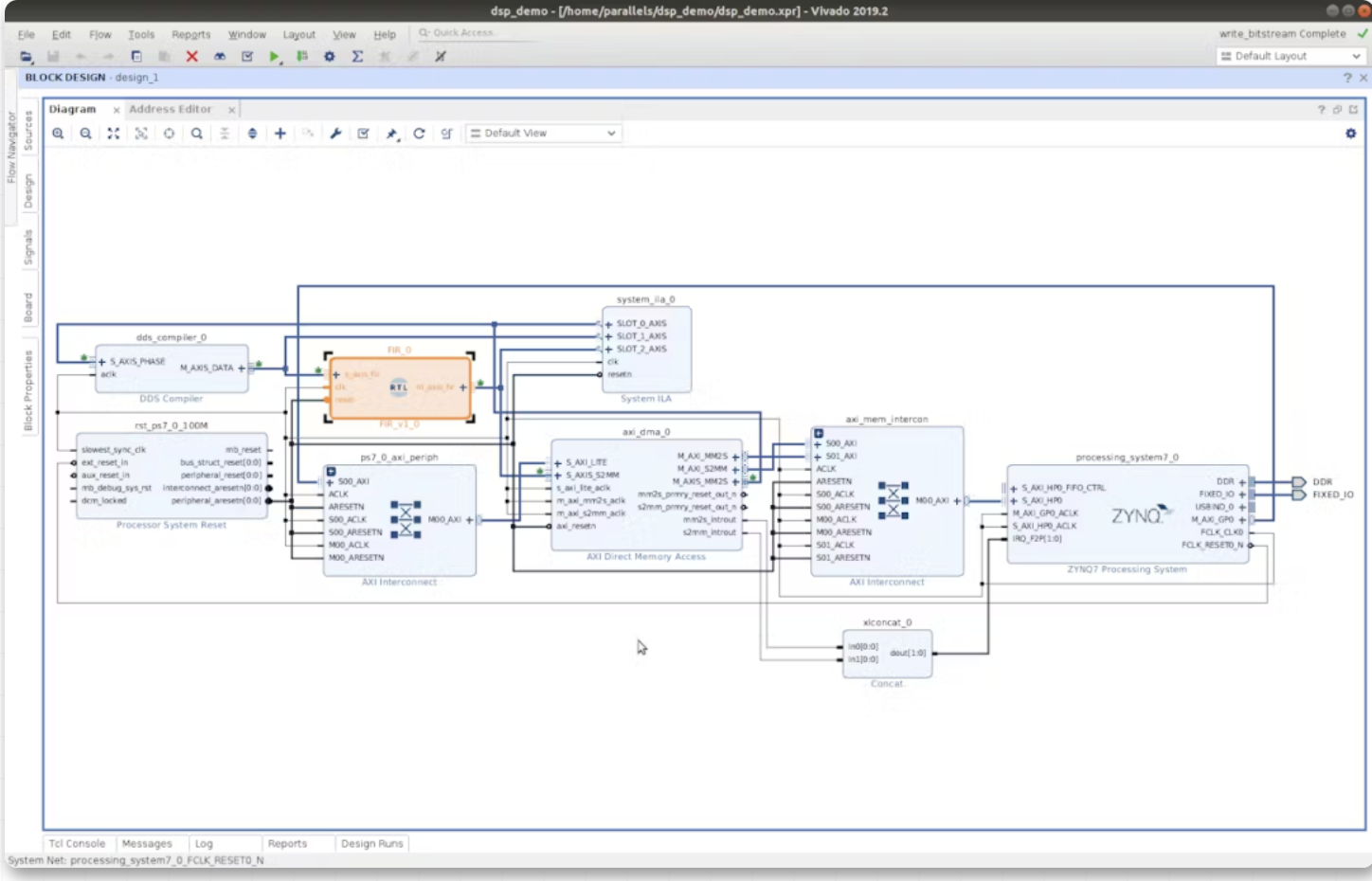

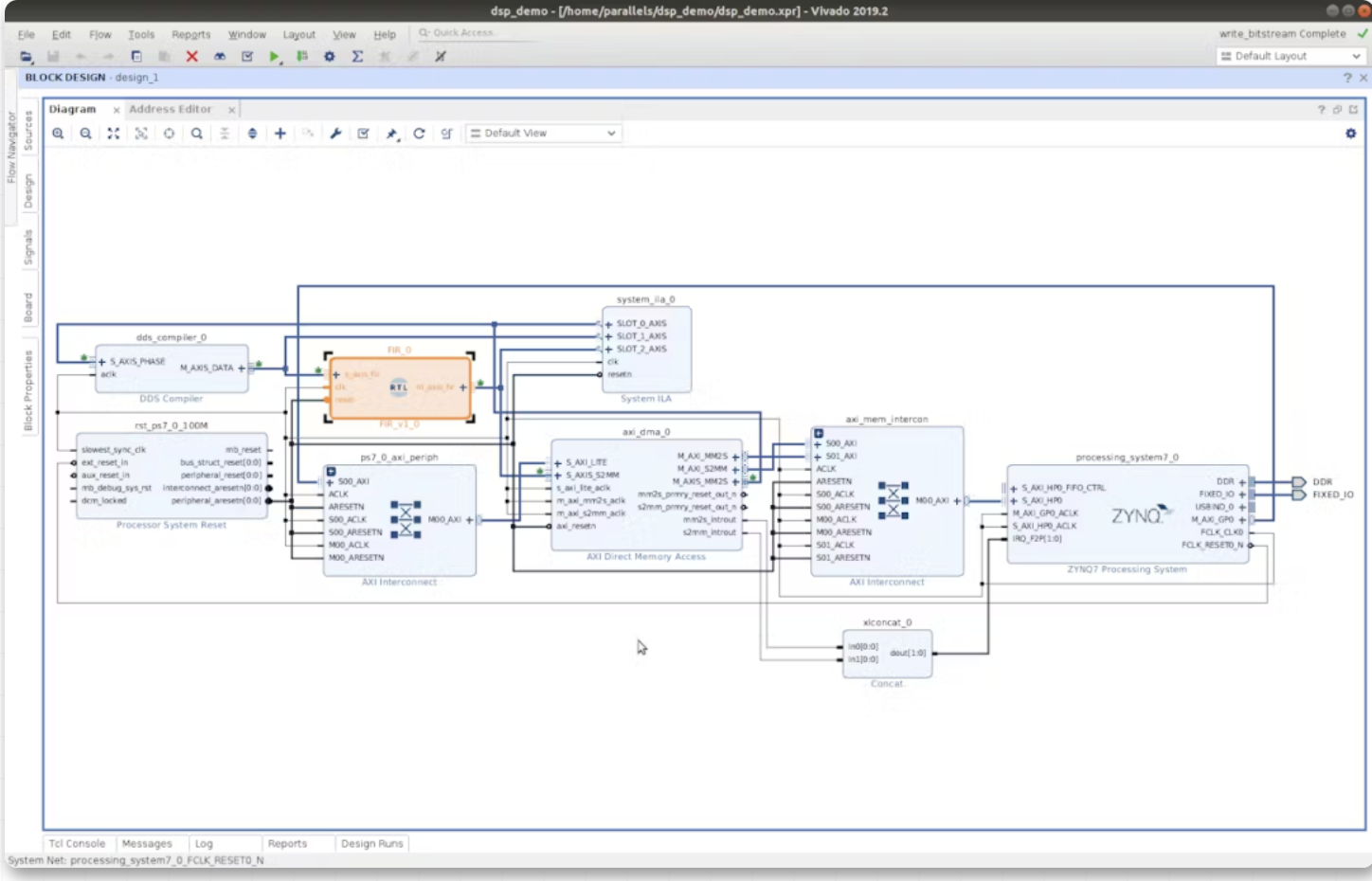

的布線資源,對于資源占用很高的設(shè)計有效地降低布局布線擁塞的風險。實現(xiàn)真正的模塊化設(shè)計,減小FPGA設(shè)計人員調(diào)試的工作量。本文用了一個具體的FPGA設(shè)計案例,來體現(xiàn)上面提到的NoC在FPGA設(shè)計中的幾項

2020-10-20 09:54:00

把握DCM、PLL、PMCD和MMCM知識是穩(wěn)健可靠的時鐘設(shè)計策略的基礎(chǔ)。賽靈思在其FPGA中提供了豐富的時鐘資源,大多數(shù)設(shè)計人員在他們的FPGA設(shè)計中或多或少都會用到。不過對FPGA設(shè)計新手來說,什么時候用DCM、PLL、PMCD和MMCM四大類型中的哪一種,讓他們頗為困惑。

2019-09-18 08:26:21

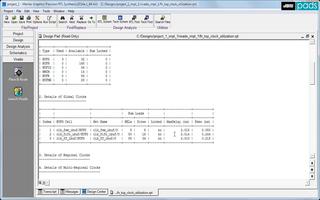

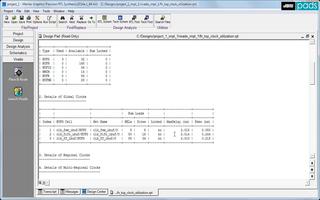

。 解析FPGA的片上資源使用情況 如何分析FPGA芯片上的組合邏輯(LUT)和時序邏輯(REG)的利用率。 一、如何得到LUT與REG的使用比例我們先看一個FPGA工程的編譯結(jié)果

2019-06-17 09:03:28

三、定時器、中斷在STM32芯片中提供了非常豐富的定時器資源:普通定時器和其他定時器普通定時器 : TIM1 TIM2 TIM3 TIM4 (4X16bit定時器)其他定時器 : IWDG WWDG

2022-01-14 06:57:03

Xilinx 的 CPLD 和 Altera 的 FPGA ,其速度等級的數(shù)值越大,反而代表芯片性能越差 溫度等級: 4.價格 在芯片選型時,價格也是特別重要的一個因素,畢竟不同芯片的價格可能相差數(shù)倍至數(shù)十倍、數(shù)百倍。應該在滿足要求的芯片中,挑選性價比最高的一款。

2020-12-23 17:21:03

求大神告知目前資源最豐富的CPLD/FPGA的詳情!萬分感謝!!!

2013-03-24 17:15:12

用FPGA往SRAM芯片中寫數(shù)據(jù)重復寫多次才能寫是怎么回事呢?

2023-04-23 11:46:44

求大神告知目前資源最豐富的CPLD/FPGA的詳情!萬分感謝!!!

2013-03-24 17:01:22

請問目前資源豐富的一款CPLD或FPGA是什么?

2013-03-22 00:18:27

FPGA編譯器生成一個比特流來配置FPGA芯片。它是如何工作的?在軟件中,節(jié)點,源,接收器,路由由int,strcuture,鏈表,指針,矩陣表示,我的意思是,在軟件軟件中,它沒有物理線的概念,如線

2019-04-15 14:17:53

在實際中設(shè)計者不需要直接選擇布線資源,布局布線器可自動地根據(jù)輸入邏輯網(wǎng)表的拓撲結(jié)構(gòu)和約束條件選擇布線資源來連通各個模塊單元。從本質(zhì)上講,布線資源的使用方法和設(shè)計的

2013-01-06 16:12:44 1586

1586 如何正確使用FPGA的時鐘資源

2017-01-18 20:39:13 22

22 DS1302芯片中文資料

2017-09-21 08:15:52 59

59 74系列芯片中文資料下載

2017-10-13 09:58:45 71

71 布線資源連通FPGA內(nèi)部的所有單元,而連線的長度和工藝決定著信號在連線上的驅(qū)動能力和傳輸速度。FPGA芯片內(nèi)部有著豐富的布線資源,根據(jù)工藝、長度、寬度和分布位置的不同而劃分為4類不同的類別。第一類

2017-12-05 11:48:44 8

8 FPGA芯片主要由6部分完成,分別為:可編程輸入輸出單元、基本可編程邏輯單元、完整的時鐘管理、嵌入塊式RAM、豐富的布線資源、內(nèi)嵌的底層功能單元和內(nèi)嵌專用硬件模塊。

2018-01-02 15:46:40 26601

26601

。FPGA芯片主要由7部分完成,分別為:可編程輸入輸出單元、基本可編程邏輯單元、完整的時鐘管理、嵌入塊式RAM、豐富的布線資源、內(nèi)嵌的底層功能單元和內(nèi)嵌專用硬件模塊。

2018-01-15 14:34:41 11850

11850

FPGA基本有可編程I/O單元、基本可編程邏輯單元、嵌入式 塊RAM、豐富的布線資源、底層嵌入功能單元和內(nèi)嵌專用硬核等6部分組成。

2018-04-11 14:49:00 2784

2784 (ASIC型)模塊。如圖所示,FPGA芯片主要由7部分組成,分別為:可編程輸入輸出單元(IOB)、基本可編程邏輯單元(CLB)、完整的時鐘管理(DCM)、嵌入式塊RAM、豐富的布線資源、內(nèi)嵌的底層功能單元和內(nèi)嵌專用硬件模塊。 1.可編程輸入輸出單元(IOB) 可編程

2018-05-25 14:11:47 8558

8558

FPGA以計算速度快、資源豐富、可編程著稱,之前一直應用于高速數(shù)字信號領(lǐng)域和ASIC驗證。隨著邏輯資源的豐富和編程工具的改進,FPGA在機器學習和硬件加速上得到越來越多的重視,目前數(shù)據(jù)中心已經(jīng)大量

2018-07-31 10:34:35 977

977

現(xiàn)在的FPGA里面有很多存儲資源,DSP(數(shù)字信號處理)資源,布線通道,I/O資源,當然最根本的還是CLB(Configurable Logic Block)。Xilinx的資源分布采用ASMBL架構(gòu)。

2018-10-22 11:00:43 5270

5270 在使用FPGA過程中,通常需要對資源做出評估,下面簡單談談如何評估FPGA的資源。

2019-02-15 15:09:05 3580

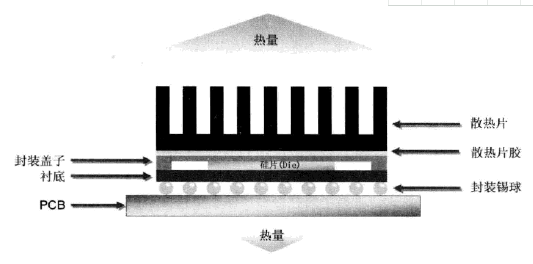

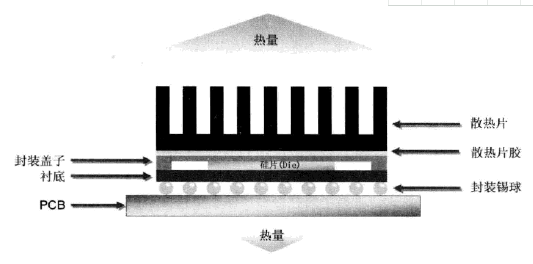

3580 ALTERA的FPGA分為商用級(commercial)和工業(yè)級(induatrial)兩種,商用級的芯片可以正常工作的結(jié)溫范圍為0~85攝氏度,而工業(yè)級芯片的范圍是-40~100攝氏度。在實際電路中,我們必須保證芯片的結(jié)溫在其可以承受的范圍之內(nèi)。

2019-02-28 14:41:50 6990

6990

在FPGA高速AD采集設(shè)計中,PCB布線差會產(chǎn)生干擾。今天小編為大家介紹一些布線解決方案。

2019-03-07 14:52:24 6086

6086 在一個環(huán)境中實施從合成到塑封式布局和布線以及比特流生成的全套 FPGA 設(shè)計。界面中內(nèi)置了用于運行布局和布線的常用選項,并在與合成結(jié)果相同的位置提供所有報告。

2019-05-17 06:06:00 2586

2586

FPGA 的基本結(jié)構(gòu)包括可編程輸入輸出單元,可配置邏輯塊,數(shù)字時鐘管理模塊,嵌入式塊RAM,布線資源,內(nèi)嵌專用硬核,底層內(nèi)嵌功能單元。由于FPGA具有布線資源豐富,可重復編程和集成度高,投資較低的特點,在數(shù)字電路設(shè)計領(lǐng)域得到了廣泛的應用

2019-12-19 07:08:00 1266

1266 FPGA 的基本結(jié)構(gòu)包括可編程輸入輸出單元,可配置邏輯塊,數(shù)字時鐘管理模塊,嵌入式塊RAM,布線資源,內(nèi)嵌專用硬核,底層內(nèi)嵌功能單元。由于FPGA具有布線資源豐富,可重復編程和集成度高,投資較低的特點,在數(shù)字電路設(shè)計領(lǐng)域得到了廣泛的應用。

2019-11-25 07:07:00 1020

1020 FPGA 的基本結(jié)構(gòu)包括可編程輸入輸出單元,可配置邏輯塊,數(shù)字時鐘管理模塊,嵌入式塊RAM,布線資源,內(nèi)嵌專用硬核,底層內(nèi)嵌功能單元。由于FPGA具有布線資源豐富,可重復編程和集成度高,投資較低的特點,在數(shù)字電路設(shè)計領(lǐng)域得到了廣泛的應用。

2019-11-21 07:03:00 1842

1842 FPGA的基本組成有:可編程I\O單元、基本可編程邏輯單元、內(nèi)嵌RAM塊、豐富的布線資源、底層嵌入功能單元和內(nèi)嵌專用硬核等。

2020-06-04 10:55:16 15883

15883 雖然很多 FPGA 工程師都是寫代碼,但是作為硬件編程工程師,如果不熟悉 FPGA 的底層資源和架構(gòu),是很難寫出高質(zhì)量的代碼——至少很難寫出復雜邏輯的高質(zhì)量代碼,也很難站在系統(tǒng)的層面去考慮芯片的選型等問題。那熟悉 FPGA 架構(gòu),首先最主要的一點,我們先來了解 FPGA 的 IO。

2020-07-16 17:53:02 9031

9031

在本輔導教材中,將重點講解如何將一個設(shè)計項目物理地實現(xiàn)于FPGA 芯片中。我們將展示如何用手工的方法選擇器件封裝的引腳,并且把這些引腳用做電路的輸入和輸出信號,此外還將描述如何使用Quartus II 編程器模塊把編譯完的電路傳送到所選擇的FPGA芯片中。

2020-10-27 16:26:00 20

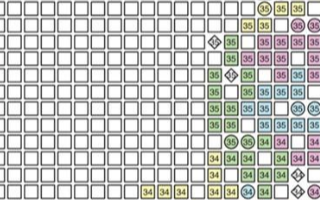

20 在使用 FPGA 過程中,通常需要對資源做出評估,下面簡單談談如何評估 FPGA 的資源。 FF 和 LUT 的數(shù)目:這個在寫出具體代碼之前,初學者通常沒法估算,但資深 FPGA 工程師會估算

2020-12-28 07:59:00 8

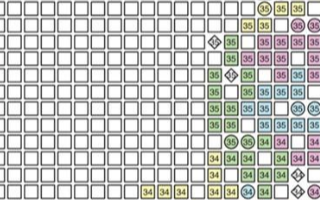

8 區(qū)域(Region):每個FPGA器件被分為多個區(qū)域,不同的型號的器件區(qū)域數(shù)量不同。

FPGA時鐘資源主要有三大類:時鐘管理模、時鐘IO、時鐘布線資源。

時鐘管理模塊:不同廠家及型號的FPGA

2020-12-09 14:49:03 20

20 FPGA時鐘資源主要有三大類 時鐘管理模、時鐘 IO 、時鐘布線資源。

2020-12-09 18:14:00 13

13 在FPGA中block ram是很常見的硬核資源,合理的利用這些硬件資源一定程度上可以優(yōu)化整個設(shè)計,節(jié)約資源利用率,充分開發(fā)FPGA芯片中的潛在價值,本文結(jié)合安路科技FPGA做簡單總結(jié),說明基本原理。

2020-12-24 14:28:09 916

916 是最佳的,然后通過使用適當?shù)腎/O和時鐘緩沖器來訪問這些時鐘路由資源。該章節(jié)包括: 時鐘緩沖選擇考慮 時鐘輸入管腳 1.時鐘緩沖器選擇考慮 7系列FPGA擁有豐富的時鐘資源。各種緩沖器類型、時鐘輸入管腳和時鐘連接,可以滿足許多不同的應用需求

2021-03-22 10:16:18 4352

4352

FPGA_ASIC-S698MSoC芯片中EDAC模塊的設(shè)計與實現(xiàn)(第四屆星載電源技術(shù)學術(shù)研討會)-該文檔為FPGA_ASIC-S698MSoC芯片中EDAC模塊的設(shè)計與實現(xiàn)總結(jié)文檔,是一份很不錯的參考資料,具有較高參考價值,感興趣的可以下載看看………………

2021-09-15 11:05:19 6

6 FPGA-SoC芯片中EDAC模塊的設(shè)計與實現(xiàn)(深圳市宇衡源電源技術(shù))-該文檔為FPGA-SoC芯片中EDAC模塊的設(shè)計與實現(xiàn)簡介文檔,是一份還算不錯的參考文檔,感興趣的可以下載看看,,,,,,,,,,,,,,,,,

2021-09-27 14:32:18 13

13 (06)FPGA資源評估1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA資源評估5)結(jié)語1.2 FPGA簡介FPGA(Field Programmable Gate

2021-12-29 19:40:45 6

6 FPGA芯片本身就具有可以反復擦寫的特性,允許FPGA開發(fā)者編寫不同的代碼進行重復編程,而FPGA可重構(gòu)技術(shù)正是在這個特性之上,采用分時復用的模式讓不同任務功能的Bitstream文件使用FPGA芯片內(nèi)部的各種邏輯資源

2022-04-26 10:38:54 2872

2872 BUCK電源芯片中自舉電容的說明

2022-05-09 16:07:16 2

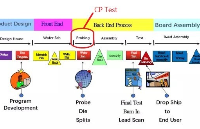

2 芯片中的CP一般指的是CP測試,也就是晶圓測試(Chip Probing)。

2022-07-12 17:00:57 13842

13842

關(guān)于 FPGA 的 IO資源分析共分為三個系列進行具體闡述,分別為: IO資源:分析FPGA IO資源的電氣特性; IO邏輯資源:分析FPGA的輸入輸出數(shù)據(jù)寄存器、DDR工作方式、可編程輸入延時

2022-12-13 13:20:06 1099

1099 當在目標 FPGA 芯片中布局和布線時,首先在 Vivado 中確定時序要求.

2023-06-20 17:31:27 389

389

FPGA的BRAM和LUT等資源都是有限的,在FPGA開發(fā)過程中,可能經(jīng)常遇到BRAM或者LUT資源不夠用的情況。

2023-08-30 16:12:04 949

949

把握DCM、PLL、PMCD和MMCM知識是穩(wěn)健可靠的時鐘設(shè)計策略的基礎(chǔ)。賽靈思在其FPGA中提供了豐富的時鐘資源,大多數(shù)設(shè)計人員在他們的FPGA設(shè)計中或多或少都會用到。

2023-10-30 11:47:55 523

523

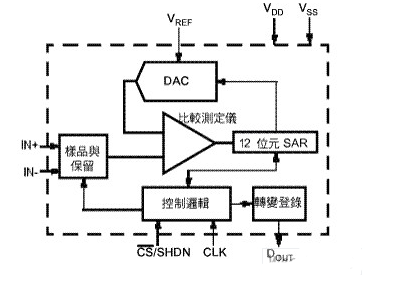

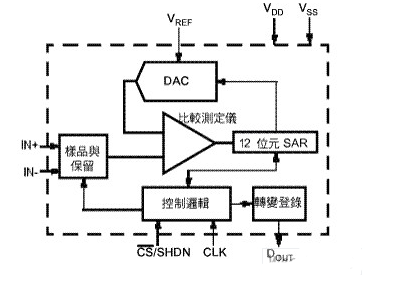

初模擬數(shù)字轉(zhuǎn)換器在芯片中大部份仍為模擬的電路組成。由于新設(shè)計型態(tài)的改進,慢速的模擬數(shù)字轉(zhuǎn)換器大多變成數(shù)字式。即使在芯片中從模擬變成數(shù)字,電路板布線工作并沒有改變。目前仍是如此,布線設(shè)計者在處理混合訊號電路時,想使布線成效良好,仍需基本的布線常識。

2023-11-02 15:16:18 164

164

現(xiàn)代電子設(shè)備中,針對復雜的數(shù)字電路,FPGA(Field-Programmable Gate Array)是一種非常優(yōu)秀的可編程邏輯器件。在FPGA的設(shè)計過程中,布局布線算法是關(guān)鍵步驟之一,其主要

2023-12-20 09:55:13 200

200 本文主要探討了金在芯片中的廣泛應用領(lǐng)域。隨著科技的發(fā)展,金作為一種優(yōu)質(zhì)的導電材料,在芯片產(chǎn)業(yè)中發(fā)揮著重要作用。

2023-12-22 10:54:24 285

285 國產(chǎn)FPGA芯片中,有幾家知名的廠商提供的產(chǎn)品在市場上表現(xiàn)較好,包括復旦微電、紫光國微、安路科技等。

2024-03-14 16:17:54 158

158 FPGA芯片的種類非常豐富,以下是一些主要的FPGA芯片及其特點。

2024-03-14 17:35:33 219

219 FPGA(現(xiàn)場可編程門陣列)芯片中的觸發(fā)器是一種重要的存儲元件,它在數(shù)字電路設(shè)計中起著至關(guān)重要的作用。觸發(fā)器的主要功能是存儲和同步數(shù)字信號,確保電路在正確的時刻捕獲和保持信號狀態(tài)。

2024-03-15 15:20:48 116

116

電子發(fā)燒友App

電子發(fā)燒友App

評論