完善資料讓更多小伙伴認識你,還能領取20積分哦,立即完善>

標簽 > fpga開發板

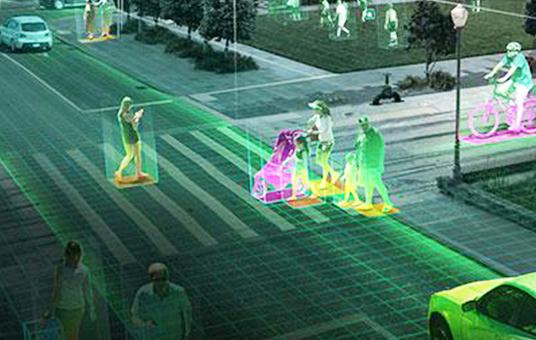

FPGA開發板在基于MCU、定制ASIC和體積龐大的電線束來實現引擎及控制電子的系統方案已發展至接近其技術和應用極限,汽車工業正面臨新的設計挑戰。過去汽車電子產品的開發周期是漫長的,而許多汽車制造商現正致力于在更短的時間內,裝備消費者所需的新一代汽車。

文章:95個 瀏覽:31875次 帖子:255個

FPGA開發板與Linux開發板是兩種不同的硬件開發平臺,各自具有不同的特點和應用場景。在以下的文章中,我將詳細介紹FPGA開發板和Linux開發板的區...

香蕉派 BPI-F2S FPGA開發板凌陽Sunplus Plus1(sp7021)芯片設計,512M RAM 和8G eMMC

香蕉派BPI-F2S 是 香蕉派團隊和 凌陽科技首次合作開發的一款工業級應用的開發板, 使用SP7021芯片設計.具有高性能,低功耗的特點; 內嵌 Li...

創龍科技(Tronlong)為您推薦基于TI TMS320C6678 + Xilinx Zynq-7045的高速多路高清視頻采集處理平臺,采用DSP+F...

2021-09-07 標簽:ZynqTMS320C6678FPGA開發板 1835 0

如果你曾看過VexRSICV的設計,對于從事邏輯設計的你會驚訝從未想過邏輯設計還能這么來做。

換一批

換一批

編輯推薦廠商產品技術軟件/工具OS/語言教程專題

| 電機控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機 | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機 | PID | MOSFET | 傳感器 | 人工智能 | 物聯網 | NXP | 賽靈思 |

| 步進電機 | SPWM | 充電樁 | IPM | 機器視覺 | 無人機 | 三菱電機 | ST |

| 伺服電機 | SVPWM | 光伏發電 | UPS | AR | 智能電網 | 國民技術 | Microchip |

| 開關電源 | 步進電機 | 無線充電 | LabVIEW | EMC | PLC | OLED | 單片機 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 藍牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太網 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 語音識別 | 萬用表 | CPLD | 耦合 | 電路仿真 | 電容濾波 | 保護電路 | 看門狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 閾值電壓 | UART | 機器學習 | TensorFlow |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |