分頻器是數字系統設計中的基本電路,根據不同設計的需要,我們會遇到偶數分頻、奇數分頻、半整數分頻等,有時要求等占空比,有時要求非等占空比。在同一個設計中有

2010-09-03 17:04:20 2442

2442

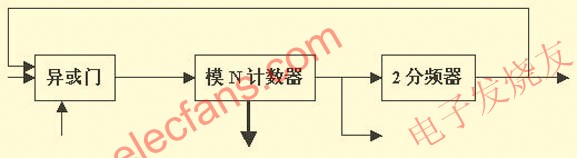

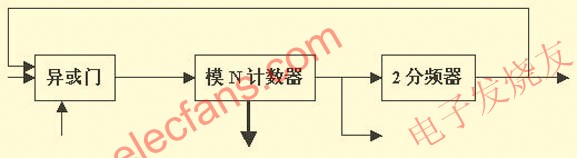

本文首先介紹了各種分頻器的實現原理,并在FPGA開發平臺上通過VHDL文本輸入和原理圖輸入相結合的方式,編程給出了仿真結果。最后通過對各種分頻的分析,利用層次化設計思想,綜合設計出了一種基于FPGA的通用數控分頻器,通過對可控端口的調節就能夠實現不同倍數及占空比的分頻器。

2015-05-07 09:43:16 4685

4685

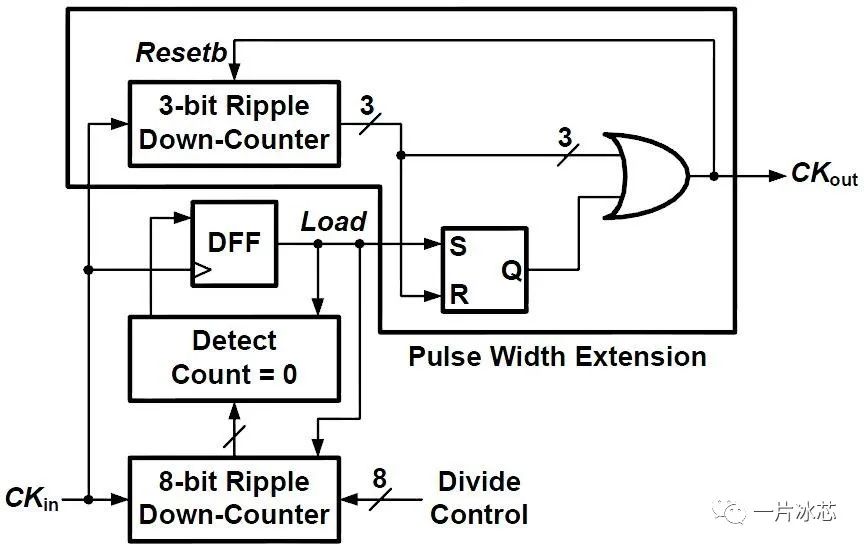

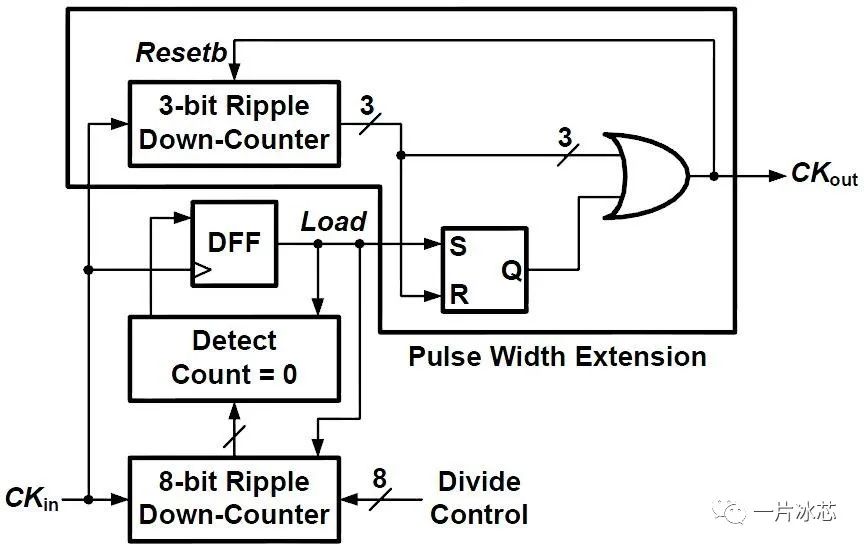

文獻給出的分頻器結構如圖1所示。該分頻器最高輸入頻率(f~in~)為16.3GHz,也就是一個周期只有(T~in~,T ~in~ = 1/ f~in~)61.3ps。

2023-10-31 12:54:56 767

767

`基于FPGA+的任意小數分頻器的設計基于FPGA的多種分頻設計與實現基于FPGA的小數分頻器的實用Verilog 實現基于FPGA 的通用分頻用Verilog+HDL實現基于FPGA的通用分頻器

2012-02-03 15:02:31

[table][tr][td] 1、半整數分頻占空比不為50%//說明:設計的史上最好用的半整數分頻占空比不為50%,包含設計思路module div_5(clk,clk_div,cnt1,cnt2

2018-07-03 02:44:45

分頻器EDA設計代碼···僅供參考···

2013-12-09 12:26:46

咨詢一個問題:CH34X系列USB轉串口芯片的波特率分頻方式只有整數分頻?還是有小數分頻?例如CP210x芯片的波特率生成只有整數分頻,為48 MHz/(2 × Prescale × n),生成

2022-07-07 07:09:19

如題,設置任意參數可變的整數分頻,分頻系數由DSP發送給CPLD,在調試的過程中發現由2分頻調到3分頻的時候,占空比不為50%,但是從新啟動后的3分頻的占空比為50%,猜測應該是計數器cnt1

2017-03-13 16:57:17

基于FPGACPLD的占空比為1∶n的n分頻器的設計

2017-09-30 09:11:08

本帖最后由 weihu_lu 于 2014-6-19 16:25 編輯

作者:盧威虎1、前言 分頻器是FPGA設計中使用頻率非常高的基本單元之一。盡管目前在大部分設計中還廣泛使用集成鎖相環(如

2014-06-19 16:15:28

【摘要】:介紹了基于FPGA的任意分頻系數的分頻器的設計,該分頻器能實現分頻系數和占空比均可以調節的3類分頻:整數分頻、小數分頻和分數分頻。所有分頻均通過VHDL語言進行了編譯并且給出了仿真圖。本

2010-04-26 16:09:01

雙模前置小數分頻原理是什么?如何對小數分頻器進行仿真測試?

2021-04-29 07:29:41

中從電子設計的外圍器件逐漸演變為數字系統的核心。伴隨著半導體工藝技術的進步,FPGA器件的設計技術取得了飛躍發展及突破。分頻器通常用來對某個給定的時鐘頻率進行分頻,以得到所需的時鐘頻率。在設計數

2019-10-08 10:08:10

分頻器在CPLD/FPGA設計中使用頻率比較高,盡管目前大部分設計中采用芯片廠家集成的鎖相環資源 ,但是對于要求奇數倍分頻(如3、5等)、小數倍(如2.5、3.5等)分頻、占空比50%的應用場合卻往往不能滿足要求。利用CPLD/FPGA設計多功能分頻器,我們具體該怎么做呢?

2019-08-12 07:50:25

小數分頻器整數邊界雜散問題的提出小數分頻器整數邊界雜散的優化設計

2021-04-19 08:32:15

要設計小數分頻PLL,基本架構已經確定:使用基于MASH111的DSM,雙模預分頻器+PScounter實現。現在遇到的問題是,不知道怎么把小數分頻控制字經過DSM后的輸出與整數分頻控制字結合起來去控制(雙模分頻器+PScounter)可編程分頻器此前沒做過小數分頻PLL,求助大佬們點撥一二

2021-06-24 07:20:38

所示。該器件具有一個輸出分頻器(在VCO之后),但輸出頻率和VCO頻率都接近20MHz的整數倍。這種設置將迫使任何PLL產生分數雜散。…

2022-11-18 07:51:05

是否有評估板的外部(FPGA外部)時鐘分頻器而不是使用DCM或PLL?問候,半

2020-03-16 09:11:44

使用VHDL語言怎樣實現數控半整數分頻器,就當輸入為3時,就實現3.5分頻,當輸入為4時,就實現4.5分頻,同時要求占空比為50%。

2014-12-02 18:28:57

置分頻有各種實施方案,但是數字化設計行業中最簡單且最經常使用的實施方案包括:* 紋波分頻器* 具有50%占空比的基于Div解碼的2N倍分頻器* 不具有50%占空比的基于時鐘門控使能技術的整數分頻器

2012-12-11 14:43:20

至芯昭哥帶你學FPGA之FPGA_100天之旅_任意分頻器

2017-08-19 11:14:57

我想對2GHz的正弦波(相位噪聲很低)進行16分頻,分頻出來的125M信號輸入給FPGA,想選用ADi的分頻器實現分頻功能,我有以下幾個問題:1.我查了ADi的分頻器,分為(1)時鐘分頻器,(2

2019-01-11 13:39:43

PWM預分頻器、分頻器和定時器的分辨率是多少?

2020-12-07 06:07:09

本帖最后由 haozix521 于 2013-10-4 20:42 編輯

想做一個占空比50%的奇數分頻器,但是不是很了解這其中的意思。網上的資料都是這樣講的“對于實現占空比為50%的N倍奇數分頻

2013-10-04 20:35:11

任意分頻系數小數分頻器相關文檔及源代碼

2009-08-03 09:49:30 75

75 在復雜數字邏輯電路設計中,經常會用到多個不同的時鐘信號。介紹一種通用的分頻器,可實現2~256 之間的任意奇數、偶數、半整數分頻。首先簡要介紹了FPGA 器件的特點和應用范

2009-11-01 14:39:19 78

78 分別為1.2 GHz和800 MHz。可選的CMOS時鐘輸出工作頻率為250 MHz。每路輸出都有一個可編程分頻器,可以旁路該分頻器或者設置最高32的整數分頻比。用

2023-02-13 14:46:44

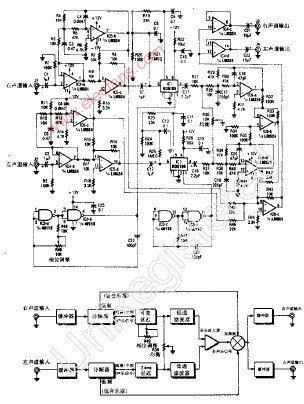

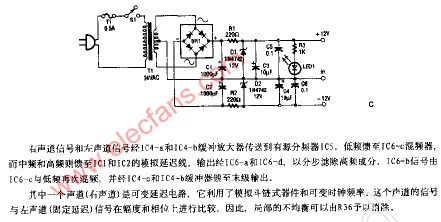

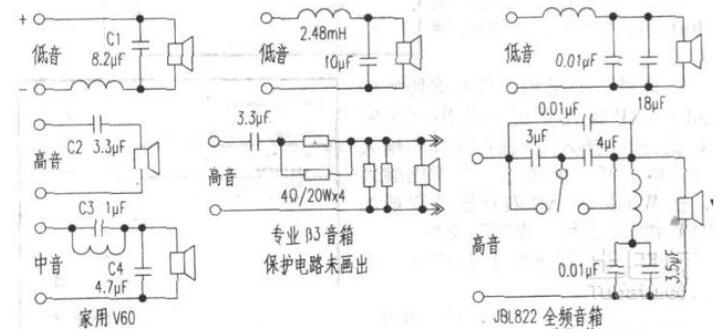

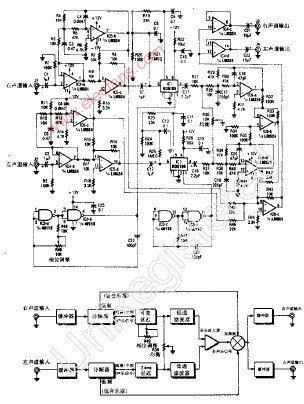

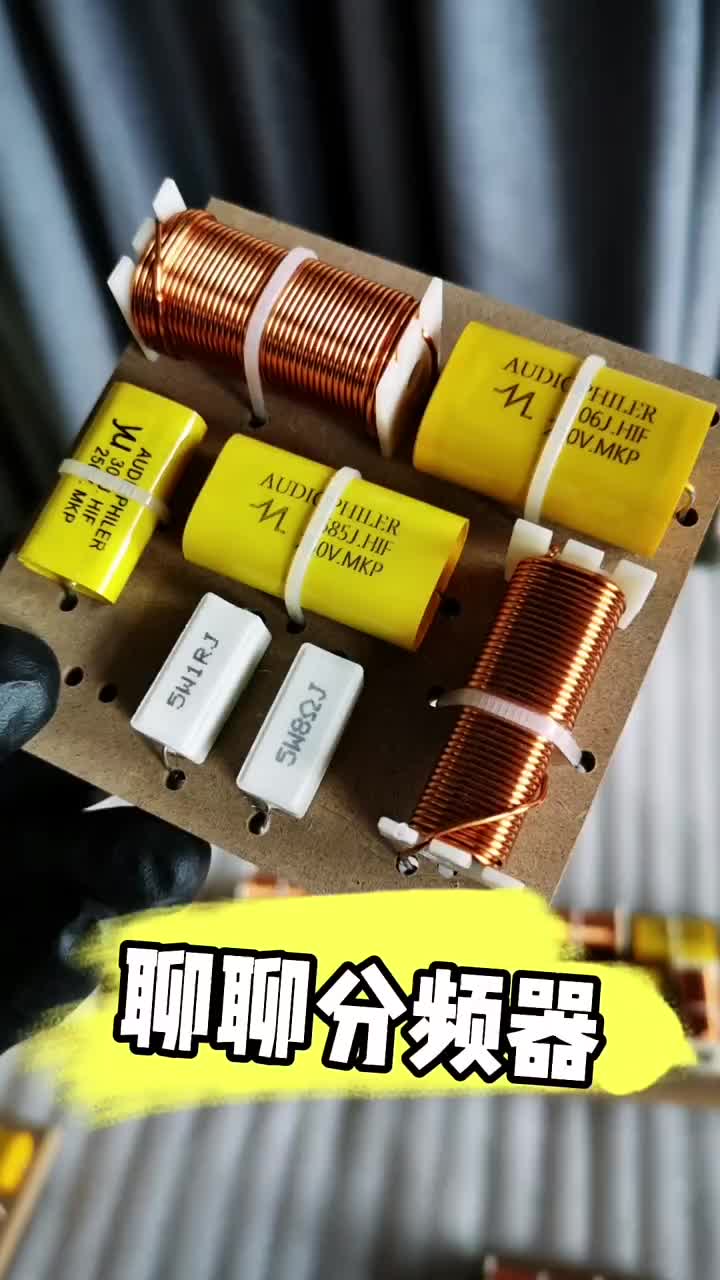

Hi-Fi三路有源分頻器:此立體聲三路有源分頻器與三路揚聲器系統配用,可避免無源分頻網絡的缺點,使揚聲器獲得最佳的功率電平。什么是有源分頻器?為什么需要有源分頻器 絕大多

2009-11-27 16:36:03 919

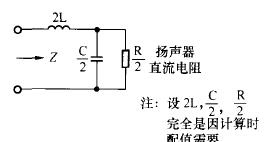

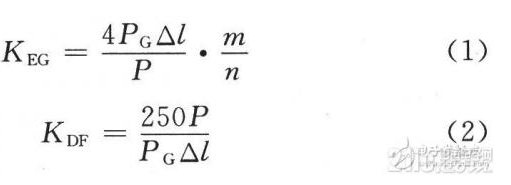

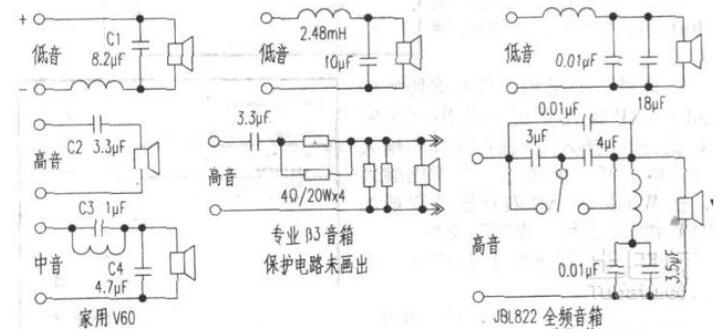

919 定阻型功率分頻器的設計與制作(四)-分頻器元器件的選取與制作:制作分頻器所需的電阻,一律用金屬膜電阻為宜,但要根據不同的需要適當選取相應大小的額定功率。2 電容器的

2009-12-02 15:46:59 71

71 定阻型功率分頻器的設計與制作(三)-二階功率分頻器

2009-12-02 15:48:19 76

76 定阻型功率分頻器的設計與制作(二)--一分頻點的選擇

2009-12-02 15:50:36 72

72 本文介紹了一種能夠完成半整數和各種占空比的奇/偶數和的通用的分頻器設計,并給出了本設計在Altera公司的FLEX10K系列EPF10K10LC84-3型FPGA芯片中實現后的測試數據和設計硬件的測

2009-12-19 16:25:09 65

65 基于FPGA 的等占空比任意整數分頻器的設計

給出了一種基于FPGA 的等占空比任意整數分頻電路的設計方法。首先簡要介紹了FPGA 器件的特點和應用范圍, 接著討論了一

2010-02-22 14:22:32 39

39 分頻器設計與制作 (電子書):分頻器的基本原理,分頻器設計,分頻頻率和截止帶衰減率的選擇與使用,元件的選配及要求等內容,電感線圈的設計與制作。

2010-03-29 10:53:02 702

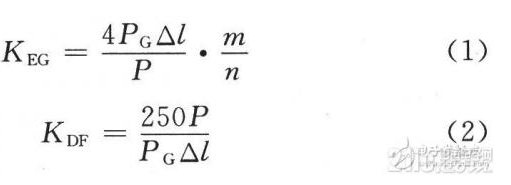

702 提出了一種通用的可編程雙模分頻器,電路主要由3 部分組成: 9/8 預分頻器,8 位可編程計數器和ΣΔ調制器構成。通過打開或者關斷ΣΔ 調制器的輸出來實現分數和整數分頻兩種工作

2010-04-23 08:39:35 30

30 簡要介紹了CPLD/FPGA器件的特點和應用范圍,并以分頻比為2.5和1.5的分頻器的設計為例,介紹了在MaxPlusII開發軟件下,利用VHDL硬件描述語言以及原理圖的輸入方式來設計數字邏輯電路的過

2010-07-17 17:55:57 36

36 UXN14M9P是一款高度靈活的整數分頻器,外殼8至511之間的所有整數分頻比。該器件具有單端或差分輸入和輸出功能。UXN14M9P封裝在40引腳、6mm x 6mm無引腳塑料SMT中

2024-02-29 13:58:38

UXN14M32K預分頻器15 GHz、32位有效分頻器UXN14M32KSuperDivider是一款DC-15 GHz、高度瞬時的整數分頻器,頂部1和4,294,967,295

2024-02-29 13:59:41

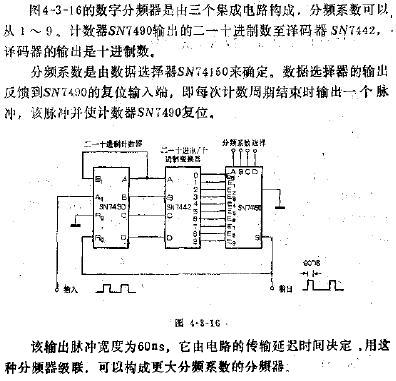

分頻系數可變的分頻器

2009-04-11 10:18:26 1206

1206

具有奇次和偶次分頻的分頻器

2009-04-11 10:22:12 880

880

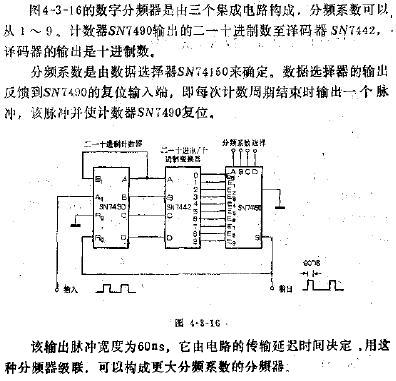

數字分頻器

2009-04-11 10:26:21 3033

3033

摘 要: 本文通過在QuartursⅡ開發平臺下,一種能夠實現等占空比、非等占空比整數分頻及半整數分頻的通用分頻器的FPGA設計與實現,介紹了利用VHDL硬件描

2009-06-20 12:43:07 562

562

摘要:簡要介紹了CPLD/FPGA器件的特點和應用范圍,并以分頻比為2.5的半整數分頻器的設計為例,介紹了在MAX+plus II開發軟件下,利用VHDL硬件描述語言以及原理圖的輸

2009-06-20 12:45:00 627

627

分頻器原理圖

2009-09-21 09:51:47 14659

14659

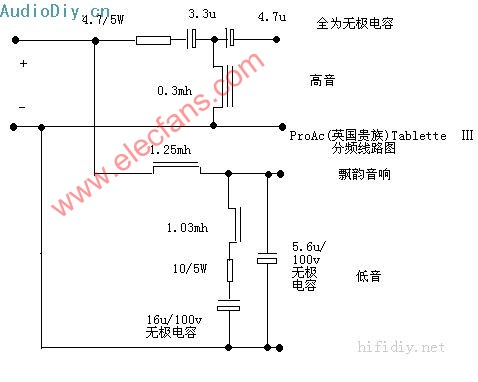

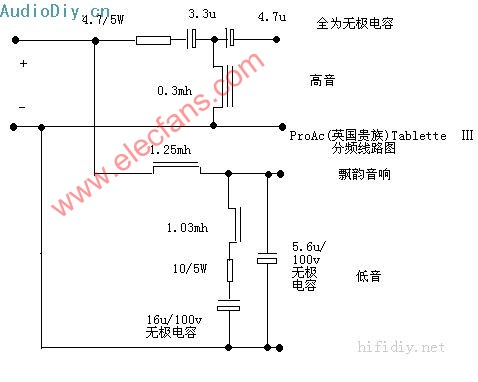

聲樂分頻器

2009-10-07 11:54:17 738

738

聲樂分頻器(續)

2009-10-07 11:55:27 498

498

基于CPLD/FPGA的多功能分頻器的設計與實現

引言

分頻器在CPLD/FPGA設計中使用頻率比較高,盡管目前大部分設計中采用芯片廠家集成的鎖相環資源 ,但是對于要求

2009-11-23 10:39:48 1139

1139

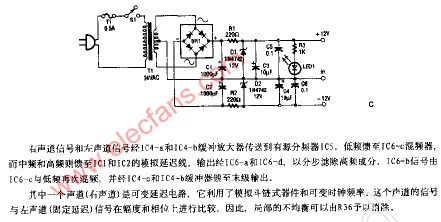

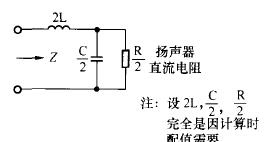

二階分頻器低通單元電路

二階(雙元件)低通分頻器電路結構如圖1所示。

2009-12-21 18:48:26 3121

3121

什么是分頻器 分頻器介紹

分頻器是指將不同頻段的聲音信號區分開來,分別給于放大,然后送到相應頻段的揚聲器中再進行重放

2010-02-05 17:51:10 3676

3676 分析了應用于倍頻電路的預置可逆分頻器的工作原理,推導了觸發器的驅動函數。并建立了基于simulink 和FPGA 的分頻器模型,實驗結果表明分頻器可以實現預置模和可逆分頻功能,滿足倍

2011-08-17 16:50:45 1896

1896

提出了一種基于FPGA的小數分頻實現方法,介紹了現有分頻方法的局限性,提出一種新的基于兩級計數器的分頻實現方法,給出了該設計方法的設計原理以及實現框圖

2011-11-09 09:36:22 121

121 給出了一種基于FPGA的分頻電路的設計方法.根據FPGA器件的特點和應用范圍,提出了基于Verilog的分頻方法.該方法時于在FPGA硬件平臺上設計常用的任意偶數分頻、奇數分頻、半整數分頻

2011-11-09 09:49:33 355

355 介紹了一種基于FPGA的雙模前置小數分頻器的分頻原理及電路設計,并用VHDL編程實現分頻器的仿真.

2011-11-29 16:43:06 48

48 △∑小數頻率合成器中的小數分頻器設計設計方案、技術指標、調試等。

2016-05-24 10:03:05 9

9 用 Verilog實現基于FPGA 的通用分頻器的設計時鐘分頻包括奇數和偶數分頻

2016-07-14 11:32:47 45

45 什么是分頻器 分頻器是指將不同頻段的聲音信號區分開來,分別給于放大,然后送到相應頻段的揚聲器中再進行重放。在高質量聲音重放時,需要進行電子分頻處理。 分頻器是音箱內的一種電路裝置,用以將輸入的模擬

2017-11-18 11:49:30 46430

46430 分頻器分為主動式、被動式、脈沖分頻器三種。主動式電子分音器的原理就是要把適當頻率訊號傳給適當的單體,被動式分音器“功能、用途”是介于擴大器與喇叭之間,由于單一喇叭無法達到“全頻段響應”,脈沖分頻器利用漢穩態電路的計數功能實現分頻的電路,又稱為數字分頻器。

2018-01-10 15:36:20 10793

10793 本文開始介紹了音箱分頻器原理,其次介紹了音箱分頻器分類與特點以及音箱分頻器電路及作用,最后介紹了音箱分頻器接線方法圖解。

2018-04-13 09:32:27 110675

110675 本文首先介紹了什么是分頻器,其次闡述了音箱箱體及音箱分頻器結構和原理,最后介紹了音箱分頻器特點和作用。

2018-05-25 17:47:16 11413

11413

本文主要介紹的是汽車音響的分頻器,首先介紹了汽車音響的分頻器的種類,其次介紹了分頻器的作用及分頻點的選擇,最后分析了汽車音響分頻器安裝位置,具體的跟隨小編一起來了解一下。

2018-05-28 11:54:38 12975

12975 本文首先介紹了分頻器的分類及電子分頻器的工作原理,其次介紹了主動分頻器的優缺點,最后介紹了被動分頻器的優缺點,具體的跟隨小編一起來了解一下。

2018-05-28 14:52:31 47204

47204 設計背景: 分頻在 fpga的設計中一直都擔任著很重要的角色,而說到分頻,我相信很多人都已經想到了利用計算器來計算達到想要的時鐘頻率,但問題是僅僅利用計數器來分頻,只可以實現偶數分頻,而如果我需要

2018-06-13 11:21:48 12390

12390

脈沖按照一定的比例,即分周比進行分頻。分頻的難點是,無論設定分周比是整數還是分數,分頻后輸出的A‘相,B’相脈沖仍然要保持正交或近似正交。為此提出一種基于FPGA的整數分周比實現方法。該方法邏輯結構簡單,配置靈活,易于擴展,具有很高的實用價值。

2018-11-20 09:39:03 1068

1068

偶數倍分頻器的實現非常簡單,只需要一個計數器進行計數就能實現。如需要N分頻器(N為偶數),就可以由待分頻的時鐘觸發計數器進行計數,當計數器從0計數到N/2-1時,將輸出時鐘進行翻轉,并給計數器一個復位信號,以使下一個時鐘開始從零計數。

2019-02-01 01:49:00 1029

1029

分頻器主要分為偶數分頻、奇數分頻、半整數分頻和小數分頻,如果在設計過程中采用參數化設計,就可以隨時改變參量以得到不同的分頻需要。

2019-02-01 01:28:00 15719

15719

分頻器是一種基本電路,通常用來對某個給定頻率進行分頻,得到所需的頻率。整數分頻器的實現非常簡單,可采用標準的計數器,也可以采用可編邏輯器件設計實現。但在某些場合下,時鐘源與所需的頻率不成整數倍關系,此時可采用小數分頻器進行分頻。

2019-11-20 07:05:00 6652

6652 論文分析了雙模前置小數分頻器的分頻原理和電路實現。結合脈沖刪除技術,提出了一種適于硬件電路實現的任意小數分頻的設計方案 ,用 VerilogHDL語 言編程 ,在 QuartusII下對 此方案進 行 了仿 真 ,并用 Cyclone 系 列 的 EP1C12Q240C8芯 片來 實 現 。

2019-08-02 08:00:00 5

5 本文主要闡述看音箱分頻器的維修方法及音箱分頻器接喇叭的方法。

2020-03-28 11:09:59 14938

14938

在數字系統設計中,根據不同的設計需要,經常會遇到偶數分頻、奇數分頻、半整數分頻等,有的還要求等占空比。在基于cpld(復雜可編程邏輯器件)的數字系統設計中,很容易實現由計數器或其級聯構成各種形式的偶數分頻及非等占空比的奇數分頻,但對等占空比的奇數分頻及半整數分頻的實現較為困難。

2020-06-26 09:36:00 825

825

因為偶數分頻器過于簡單,所以我們從奇數分頻器開始說起8 01 奇數分頻器 ? ? 假設我們要實現一個2N+1分頻的分頻器,就需要高電平占N+0.5個周期,低電平占N+0.5個周期,這樣進行處理的最小

2021-03-12 15:44:54 5614

5614

簡要介紹了CPLD/FPGA器件的特點和應用范圍,并以分頻比為2.5和1.5的分頻器的設計為例,介紹了在MaxPlusII開發軟件下,利用VHDL硬件描述語言以及原理圖的輸入方式來設計數字邏輯電路的過程和方法。該設計具有結構簡單、實現方便、便于系統升級的特點。

2021-03-16 09:45:53 10

10 整數N分頻軟件

2021-03-18 13:06:26 7

7 簡要介紹了 CPLD/FPGA器件的特點和應用范圍,并以分頻比為2.5和15的分頻器的設計為例,介紹了在 Maxplusll開發軟件下,利用ⅤHDL硬件描述語言以及原理圖的輸入方式來設計數字邏輯電路的過程和方法。該設計具有結構簡單、實現方便、便于系統升級的特點。

2021-03-22 16:52:15 5

5 簡要介紹了CPLD/FPGA器件的特點和應用范圍,并以分頻比為25和15的分頻器的設計為例,介紹了在 Maxplus開發軟件下,利用VHDL硬件描述語言以及原理圖的輸入方式來設計數字邏輯電路的過程和方法該設計具有結構簡單、實現方便、便于系統升級的特點。

2021-04-12 16:29:05 11

11 一種基于FPGA的分頻器的實現說明。

2021-05-25 16:57:08 16

16 基于CPLD/FPGA的半整數分頻器設計方案

2021-06-17 09:37:02 21

21 時序至關重要:改善分數分頻鎖相環合成器中的整數邊界雜散狀況

2022-11-04 09:50:31 1

1 偶數倍分頻器的實現非常簡單,只需要一個計數器進行計數就能實現。如需要N分頻器(N為偶數),就可以由待分頻的時鐘觸發計數器進行計數,當計數器從0計數到N/2-1時,將輸出時鐘進行翻轉,并給計數器一個復位信號,以使下一個時鐘開始從零計數。

2022-11-21 09:41:24 751

751 所謂“分頻”,就是把輸入信號的頻率變成成倍數地低于輸入頻率的輸出信號。數字電路中的分頻器主要是分為兩種:整數分頻和小數分頻。其中整數分頻又分為偶分頻和奇分頻,首先從偶分頻開始吧,入門先從簡單的開始!

2023-03-23 15:06:22 948

948

上一篇文章介紹了偶分頻,今天來介紹一下奇數分頻器的設計。

2023-03-23 15:06:49 692

692

前面分別介紹了偶數和奇數分頻(即整數分頻),接下來本文介紹小數分頻。

2023-03-23 15:08:04 658

658

初學 Verilog 時許多模塊都是通過計數與分頻完成設計,例如 PWM 脈寬調制、頻率計等。而分頻邏輯往往通過計數邏輯完成。本節主要對偶數分頻、奇數分頻、半整數分頻以及小數分頻進行簡單的總結。

2023-03-29 11:38:40 3108

3108

上一篇文章時鐘分頻系列——偶數分頻/奇數分頻/分數分頻,IC君介紹了各種分頻器的設計原理,其中分數分頻器較為復雜,這一篇文章IC君再跟大家聊聊分數分頻的具體設計實現。

2023-04-25 14:47:44 1028

1028

FPGA分頻器是一種常用于數字信號處理、通信系統、雷達系統等領域的電路,其作用是將信號分成多個頻段。

2023-05-22 14:29:44 1032

1032

對于要求相位以及占空比嚴格的小數分頻,建議采用模擬電路實現。而使用數字電路實現只能保證盡量均勻,在長時間內進行分頻。

2023-06-05 17:20:51 969

969

是用于滿足設計的需求。 分頻:產生比板載時鐘小的時鐘。 倍頻:產生比板載時鐘大的時鐘。 二:分頻器的種類 對于分頻電路來說,可以分為整數分頻和小數分頻。 整數分頻:偶數分頻和奇數分頻。 小數分頻:半整數分頻和非半整數分頻。 三:分頻器的思想 采用計數器的思想實

2023-11-03 15:55:02 471

471

鎖相環整數分頻和小數分頻的區別是什么? 鎖相環(PLL)是一種常用的電子電路,用于將輸入的時鐘信號與參考信號進行同步,并生成輸出信號的一種技術。在PLL中,分頻器模塊起到關鍵作用,可以實現整數分頻

2024-01-31 15:24:48 312

312 分頻器是一種電子設備,用于將輸入信號分成不同頻率的輸出信號。其主要作用是將原始輸入信號分離成多個頻率范圍內的信號,以供不同的電路進行處理。分頻器廣泛應用于通信、測量和音頻系統中。 分頻器的主要

2024-02-01 11:19:51 461

461

2442

2442

4685

4685

767

767

78

78 919

919 71

71 65

65 39

39 702

702 30

30 36

36 562

562

627

627

1139

1139

1896

1896

121

121 355

355 46430

46430 10793

10793 110675

110675 12975

12975 47204

47204 12390

12390

1068

1068

1029

1029

15719

15719

6652

6652 5

5 825

825

5614

5614

10

10 5

5 11

11 751

751 948

948

3108

3108

1028

1028

471

471

312

312 461

461 電子發燒友App

電子發燒友App

評論