在數字電路中,凡是任一時刻的穩定輸出不僅決定于該時刻的輸入,而且還和電路原來狀態有關者都叫時序邏輯電路。時序邏輯電路結構示意圖如圖2-41所示。時序邏輯電路的狀態是靠具有存儲功能的觸發器所組成的存儲電路來記憶和表征的。

2018-01-31 09:27:23 53523

53523

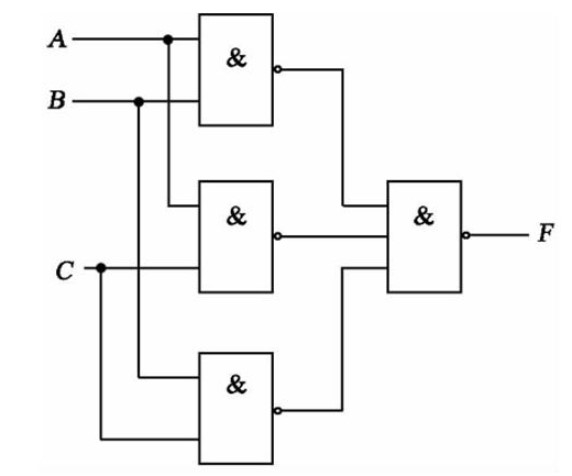

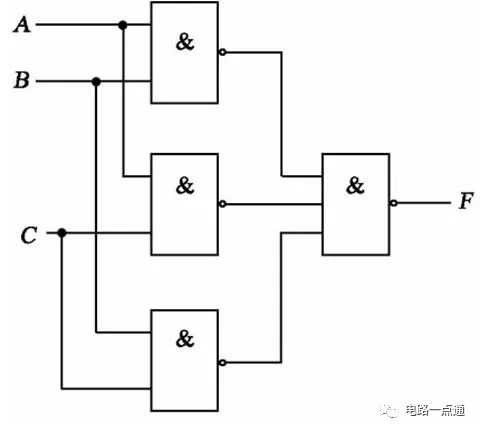

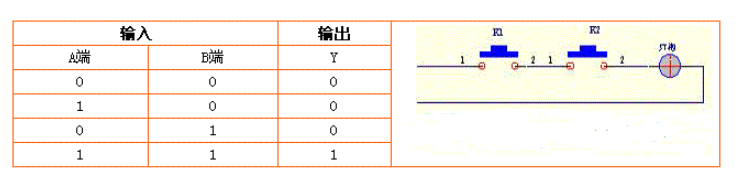

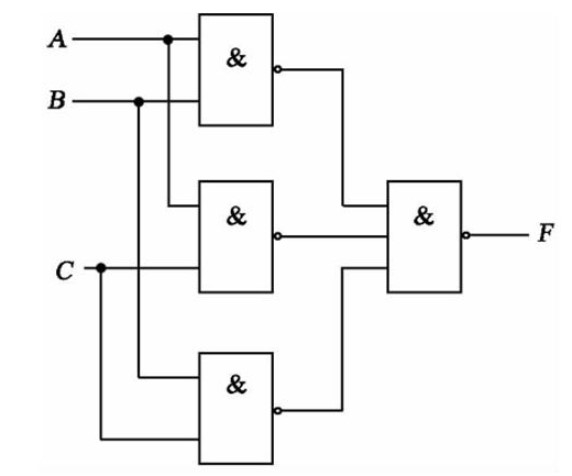

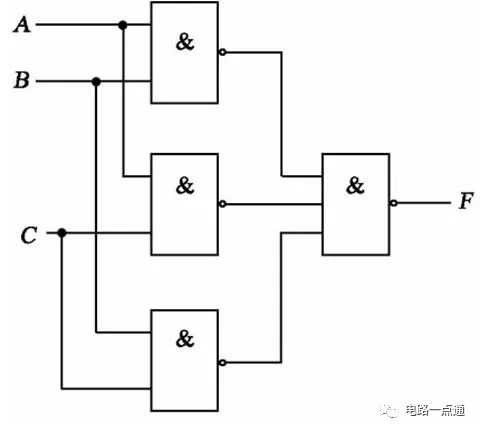

分析組合邏輯電路的目的是,對于一個給定的邏輯電路,確定其邏輯功能。

2020-08-04 15:50:00 32561

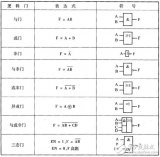

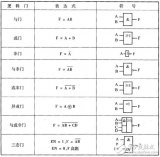

32561 邏輯門及組合邏輯電路實驗實驗目的1. 掌握與非門、或非門、與或非門及異或門的邏輯功能。2. 了解三態門的邏輯功能以及禁止狀態的判別方法。了解三態門的應用。3. 掌握組合邏輯電路的設計和實現方法。4.

2008-09-25 17:28:34

邏輯電路主要邏輯門電路之間的關系是怎樣的

2020-04-15 17:53:30

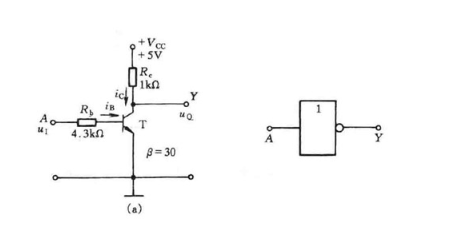

是一種離散信號的傳遞和處理,以二進制為原理、實現數字信號邏輯運算和操作的電路。分組合邏輯電路和時序邏輯電路。前者由最基本的“與門”電路、“或門”電路和“非門”電路組成,其輸出值僅依賴于其輸入變量的當前值

2020-12-23 17:25:49

邏輯電路的糾錯技術是如何實現的?糾錯技術在邏輯電路中有什么作用?

2021-06-18 09:50:31

CPLD邏輯電路

2019-10-29 09:10:54

表達式:(4)畫出邏輯圖: 從以上邏輯表達式和邏輯圖可以看出,用異或門代替與門和或門能使邏輯電路比較簡單。在化簡和變換邏輯表達式時,應盡可能使某些輸出作為另一些輸出的條件,例如,利用Y2作為Y1的一

2009-04-07 10:54:26

fpga時序邏輯電路的分析和設計 時序邏輯電路的結構及特點時序邏輯電路——任何一個時刻的輸出狀態不僅取決于當時的輸入信號,還與電路的原狀態有關。[hide][/hide]

2012-06-20 11:18:44

。五、邏輯電路 根據是否包含記憶元件課分為組合邏輯電路和時序邏輯電路。 組合邏輯電路:不包含記憶元件,某時間點的輸出僅僅取決于當時的輸入。有多個輸入輸出,內部用于基本邏輯函數的邏輯門,以及門電路間的連線

2019-12-10 20:32:03

為什么FPGA可以用來實現組合邏輯電路和時序邏輯電路呢?

2023-04-23 11:53:26

各位師兄: 小弟不才,誰能愿意發一份基本緊邏輯電路應用舉例電路圖看看,謝謝了.

2012-07-04 17:49:06

集成電路編碼器和譯碼器的工作原理即邏輯功能是什么?如何利用邏輯門去實現一種集成電路編碼器呢?如何利用譯碼器進行組合邏輯電路的設計呢?

2021-11-03 06:55:24

Verilog程序模塊的結構是由哪些部分組成的?如何去實現時序邏輯電路和組合邏輯電路的設計呢?

2021-11-03 06:35:57

嵌入式硬件(三)數字邏輯電路一、組合邏輯電路1.非門2.與門3.與非門4.或門5.或非門6.異或門7.三態門二、時序邏輯電路1.觸發器(flip-flop)(1)RS觸發器(2)D觸發器2.鎖存器

2021-07-26 08:02:44

0-1或1-0改變狀態,則默認情況下,組合邏輯電路的結果輸出也將在其設計中具有“無內存”,“時序”或“反饋環路”。組合邏輯組合邏輯電路由“組合”或連接在一起以產生更復雜的開關電路的基本邏輯“與非”門

2021-01-19 09:29:30

;1.3.2 “或”邏輯與“或門”電路 1.3.3 “非”邏輯與“非門”電路 1.3.4 復合邏輯運算及其

2008-05-15 21:57:28

時序邏輯電路的特點

2019-10-08 05:34:53

時序邏輯電路的設計實驗1 進一步強化EDA仿真軟件的使用;2 掌握利用MSI

2009-03-19 15:10:18

組合邏輯電路PPT電子教案學習要點: 組合電路的分析方法和設計方法 利用數據選擇器和譯碼器進行邏輯設計的方法 加法器、編碼器、譯碼器等中

2009-09-16 16:05:29

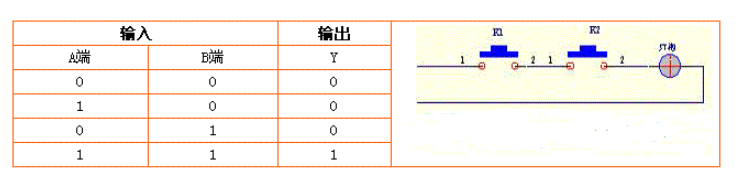

組合邏輯電路 一、實驗目的 1. 加深理解組合邏輯電路

2009-09-16 15:09:13

組合邏輯電路的分析方法2、 預習用與或非和異或門構成的半加器、全加器的工作原理四、 實驗內容1、 組合邏輯電路功能測試

2009-03-20 18:11:09

”。 組合邏輯 組合邏輯電路由“組合”或連接在一起以產生更復雜的開關電路的基本邏輯“與非”門,“或非”門組成。這些邏輯門是組合邏輯電路的基礎。組合電路的一個示例是解碼器,該解碼器將其輸入處存在

2020-12-31 17:01:17

組合邏輯電路的設計及實驗

2009-10-10 11:44:49

設計時序邏輯電路時,如何解決電路不能自啟動的問題?

是如何解決電路不能自啟動,不是‘不能自啟動’的定義

2023-05-10 14:44:22

組合邏輯電路的基本模塊是什么?時序邏輯電路怎樣進行工作的?

2021-09-18 09:19:42

鐘控傳輸門絕熱邏輯電路和SRAM 的設計本文利用NMOS管的自舉效應設計了一種新的采用二相無交疊功率時鐘的絕熱邏輯電路---鐘控傳輸門絕熱邏輯電路,實現對輸出負載全絕熱方式充放電.依此進一步設計了

2009-08-08 09:48:05

集成邏輯電路、組合邏輯電路實驗目的1. 掌握與非門、或非門、與或非門及異或門的邏輯功能。2. 了解三態門的邏輯功能以及禁止狀態的判別方法。了解三態門的應用。3. 掌握組合邏輯電路的設計和實現方法

2008-12-11 23:36:32

組合邏輯電路 :

2007-12-20 23:02:07 28

28

數字邏輯電路的內容:數制與編碼,,邏輯代數和邏輯函數,集成邏輯門,組合邏輯電路,中規模集成組

2008-09-06 01:54:26 33

33 基本邏輯電路: 組合邏輯電路、&

2008-09-12 16:35:29 40

40 組合邏輯電路設計一、實驗目的1. 熟悉組合邏輯電路的基本設計方法;2. 練習用門電路、譯碼器、數據選擇器設計組合邏輯電路。二、實驗設備1.

2008-09-12 16:41:23 0

0 時序邏輯電路的輸出不但和當前輸入有關,還與系統的原先狀態有關,即時序電路的當前輸出由輸入變量與電路原先的狀態共同決定。為達到這一目的,時序邏輯電路從某一狀態

2009-03-18 22:13:04 71

71 組合邏輯電路(簡稱組合電路)任意時刻的輸出信號僅取決于該時刻的輸入信號,與信號作用前電路原來的狀態無關時序邏輯電路(簡稱時序電路)任意時刻的輸出信號不僅取決

2009-07-15 18:45:58 0

0 組合邏輯電路電子教案:數字邏輯電路可分為兩大類: 一類叫組合邏輯電路;另一類叫時序邏輯電路。本章首先介紹組合邏輯電路的共同特點和描述方法,然后重點介紹組合邏輯電

2009-09-01 08:58:29 0

0 同步時序邏輯電路:本章系統的講授同步時序邏輯電路的工作原理、分析方法和設計方法。從同步時序邏輯電路模型與描述方法開始,介紹同步時序邏輯電路的分析步驟和方法。然后

2009-09-01 09:06:27 0

0 異步時序邏輯電路:本章主要從同步時序邏輯電路與異步時序邏輯電路狀態改變方式不同的特殊性出發, 系統的介紹異步時序邏輯電路的電路結構、工作原理、分析方法和設計方法。

2009-09-01 09:12:34 0

0 鐘控傳輸門絕熱邏輯電路和SRAM 的設計

本文利用NMOS管的自舉效應設計了一種新的采用二相無交疊功率時鐘的絕熱邏輯電路---鐘控傳輸門絕熱邏輯電路,實現對輸

2010-02-23 10:14:13 15

15 講述組合邏輯電路設計基礎

2010-05-06 10:29:15 0

0 數字邏輯電路設計課程

數字邏輯電路的設計包括兩個方面:基本邏輯功能電路設計和邏輯電路系統設計。關于基本邏輯功能電路設計一般在《數字電路技術基礎

2010-05-24 16:05:50 0

0 摘要:基于邏輯電路的設計中經常涉及到用卡諾圖化簡邏輯函數的過程,給出了利用次態卡諾圖設計邏輯電路的方法及不同觸發器的狀態方程在次態卡諾圖上的表示,并舉例加以說

2010-05-25 09:41:28 13

13 數字邏輯電路按邏輯功能和電路組成的特點可分為組合邏輯電路和時序邏輯電路兩大類。

2010-08-10 11:51:58 39

39 數字邏輯電路可分為組合邏輯電路和時序邏輯電路兩大類。組合邏輯電路在任一時刻的穩定輸出只取決于當前的輸入,而與過去的輸入無關。在結構上,組合邏輯電路僅由若干邏

2010-08-12 15:54:42 0

0 數字集成電路,根據原理可分為兩大類,既組合邏輯電路和時序邏輯電路。

組合邏輯電路的組成是邏輯門電路。電路的輸出狀態僅由同一時刻的輸入狀態決定,與電路的原

2010-08-18 15:05:23 55

55 一、實驗目的掌握組合邏輯電路的設計與測試方法

2010-09-21 16:52:20 0

0 基本組合邏輯電路

一、 實驗目的?⒈ 掌握一般組合邏輯電路的分析和設計方法。?⒉ 熟悉集成優先編碼器的邏輯功能及簡單應用。

2008-09-24 22:14:03 2504

2504

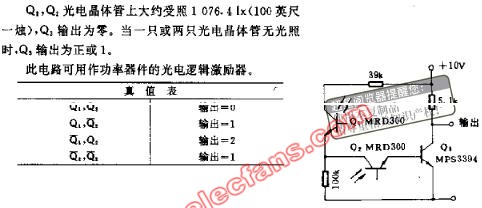

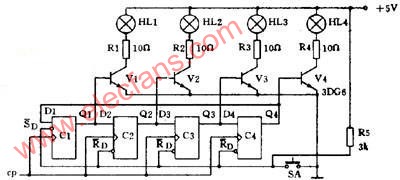

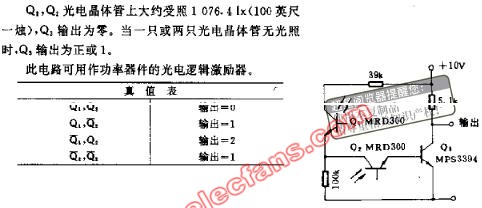

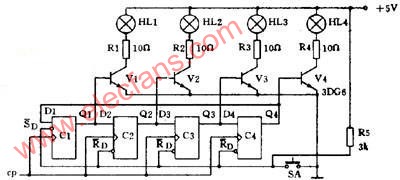

光電邏輯電路圖

2008-12-22 02:33:35 803

803

第十五講 組合邏輯電路的分析方法和設計方法

6.1概述組合邏輯電路:定義構成電路特點6.2.1組合邏輯電路的分析方法

2009-03-30 16:21:07 4567

4567

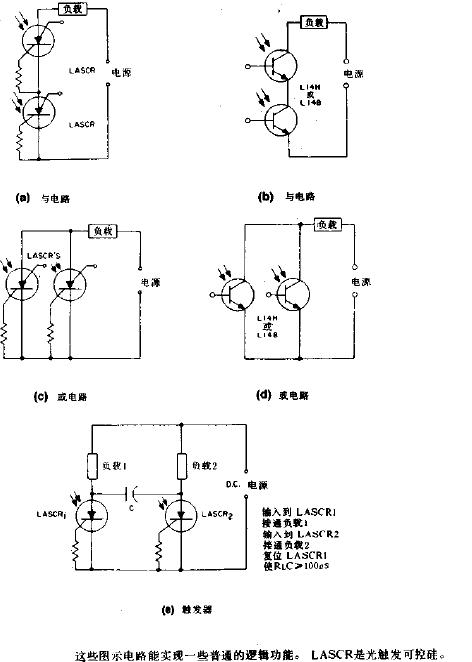

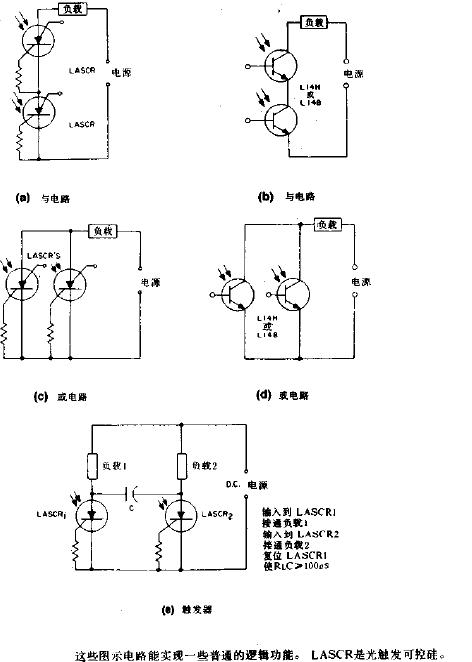

光觸發邏輯電路圖

2009-04-02 09:20:41 770

770

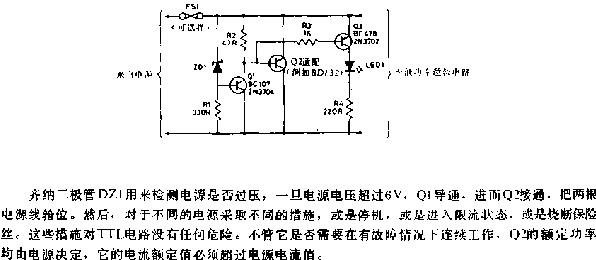

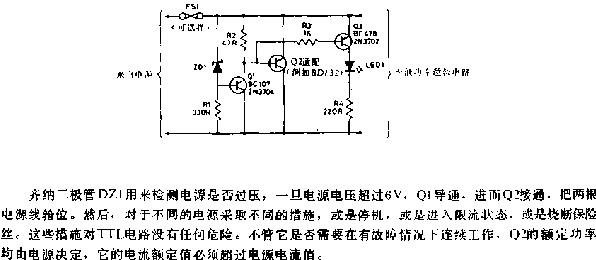

邏輯電路電源的過壓保護電路圖

2009-04-07 09:08:44 928

928

時序邏輯電路的分析方法

1. 時序邏輯電路的特點 在時序邏輯電路中,任意時刻的輸出信號不僅取決于當時的輸入信

2009-04-07 23:18:11 8145

8145

時序邏輯電路的特點

在第三章所討論的組合邏輯電路中,任一時刻的輸出信號僅僅取決于該時刻的輸入信號,而與電路原來

2009-09-30 18:19:22 9900

9900

數字邏輯電路

數字邏輯電路的用途和特點

數字電子電路中的后起之秀是數字邏輯電路。把它叫做數字電路是因為電路中傳遞的雖然也是脈沖,但這些脈沖是

2009-11-10 10:13:26 17158

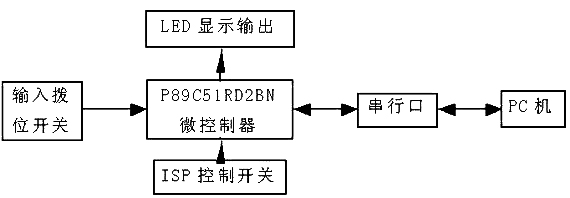

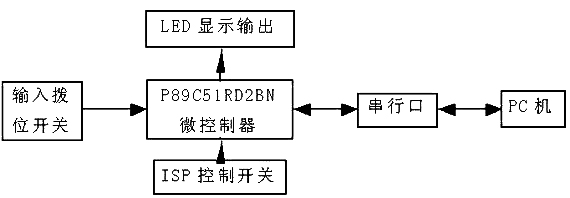

17158 CPLD邏輯電路 圖6是CPLD內部邏輯電路,CPLD選用的是LATTICE公司的ispLSI1016E,邏輯設計采用原理圖輸入法,主要功能是對MUX的通道進行選擇、對A/D轉換器進

2009-11-13 12:04:13 2502

2502

各種邏輯電路簡介

邏輯電路:

以二進制為原理、實現數字信號邏輯運算和操作的電路。分組合邏輯電路和

2009-11-24 13:27:04 2959

2959 CMOS邏輯電路,CMOS邏輯電路是什么意思

CMOS是單詞的首字母縮寫,代表互補的金屬氧化物半導體(Complementary Metal-Oxide-Semiconductor),它指的是一種特殊類

2010-03-08 11:31:47 3574

3574 什么是陣列邏輯電路

陣列邏輯電路的特點: 邏輯元件在硅片上以陣列形式排列,芯片面積小、用戶自編程、設計方便。 典型的陣列

2010-04-15 13:43:17 3714

3714 如何看懂數字邏輯電路

數字電子電路中的后起之秀是數字邏輯電路。把它叫做數字電路是因為電路中傳遞的雖然也是脈沖,但這些脈沖是用來表示二進制數碼的,例如

2010-05-24 11:35:01 2727

2727

數字邏輯電路教學中的C語言描述和應用

摘要:為了改進數字邏輯電路教學方法以適應電子技術迅猛發展的需要,我們探索和實踐了數字邏輯電路教

2010-05-24 15:40:52 1839

1839

組合邏輯電路,感興趣的可以下載看看,免費的哦!

2015-10-29 15:08:16 31

31 定時控制器邏輯電路設計定時控制器邏輯電路設計定時控制器邏輯電路設計定時控制器邏輯電路設計定時控制器邏輯電路設計定時控制器邏輯電路設計

2015-12-17 18:18:50 0

0 數字邏輯電路第3章的PPT,一些難度大,質量很高。

2016-06-03 16:57:53 0

0 詳細介紹了組合邏輯電路的分析方法,包括加法器、譯碼器、編碼器、分配器、選擇器等組合邏輯電路的分析方法

2017-01-22 13:13:01 3

3 1、掌握組合邏輯電路的設計方法。

2、掌握組合邏輯電路的靜態測試方法。

3、熟悉CPLD設計的過程,比較原理圖輸入和文本輸入的優劣。

2022-07-10 14:38:36 16

16 邏輯電路是包含邏輯關系的數字電路, 以二進制為原理、實現數字離散信號的傳遞,邏輯運算和操作的電路。最基本的邏輯電路是常見的門電路,而最簡單的門電路為與電路、或電路和非電路。

2017-05-22 09:58:43 20474

20474

邏輯電路按其邏輯功能和結構特點可分為組合邏輯電路和時序邏輯電路。

2017-05-22 15:15:59 70752

70752

若一個邏輯電路在任何時刻產生的穩定輸出信號僅僅取決于該時刻的輸入信號,而與過去的輸入信號無關,即與輸入信號作用前的電路狀態無關,則稱該電路為組合邏輯電路。

2018-01-30 16:03:16 49495

49495

數字電路根據邏輯功能的不同特點,可以分成兩大類,一類叫組合邏輯電路(簡稱組合電路),另一類叫做時序邏輯電路(簡稱時序電路)。組合邏輯電路在邏輯功能上的特點是任意時刻的輸出僅僅取決于該時刻的輸入,與電路原來的狀態無關。

2018-01-30 16:24:25 37995

37995

組合邏輯電路的設計與分析過程相反,本文小編主要跟大家介紹一下關于組合邏輯電路的設計步驟,順便回顧一下組合邏輯電路的分析方法。

2018-01-30 16:46:31 119434

119434

邏輯電路按其邏輯功能和結構特點可分為組合邏輯電路和時序邏輯電路。單一的與門、或門、與非門、或非門、非門等邏輯門不足以完成復雜的數字系統設計要求。組合邏輯電路是采用兩個或兩個以上基本邏輯門來實現更實用、復雜的邏輯功能。

2018-01-30 17:05:44 62958

62958

組合邏輯電路和時序邏輯電路都是數字電路,組合邏輯電路在邏輯功能上的特點是任意時刻的輸出僅僅取決于該時刻的輸入,與電路原來的狀態無關。而時序邏輯電路在邏輯功能上的特點是任意時刻的輸出不僅取決于當時的輸入信號,而且還取決于電路原來的狀態,或者說,還與以前的輸入有關。

2018-01-30 17:26:04 91322

91322

分析時序邏輯電路也就是找出該時序邏輯電路的邏輯功能,即找出時序邏輯電路的狀態和輸出變量在輸入變量和時鐘信號作用下的變化規律。上面講過的時序邏輯電路的驅動方程、狀態方程和輸出方程就全面地描述了時序邏輯電路的邏輯功能。

2018-01-30 18:55:32 123039

123039

本文開始介紹了時序邏輯電路的特點和時序邏輯電路的三種邏輯器件,其次介紹了時序邏輯電路的組成與時序邏輯電路檢修方法,最后介紹了時序邏輯電路的應用舉例。

2018-03-01 10:53:38 106878

106878

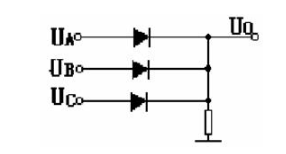

三態指其輸出既可以是一般二值邏輯電路,即正常的高電平(邏輯1)或低電平(邏輯0),又可以保持特有的高阻抗狀態。本文開始介紹了三態門的定義,其次介紹了三態門的邏輯符號,最后介紹了三款三態門邏輯電路。

2018-03-01 14:03:10 73756

73756

根據邏輯功能的不同,可把數字電路分為組合邏輯電路(Combinational Logic Circuit)和 時序邏輯電路(Sequential Logic Circuit)兩大類。

2018-07-20 08:00:00 0

0 數字電路根據邏輯功能的不同特點,可以分成兩大類,一類叫組合邏輯電路(簡稱組合電路),另一類叫做時序邏輯電路(簡稱時序電路)。組合邏輯電路在邏輯功能上的特點是任意時刻的輸出僅僅取決于該時刻的輸入

2019-02-26 15:22:20 30482

30482 時序邏輯電路是由組合邏輯電路與記憶電路(又稱存儲電路) 組合而成的。 常見時序邏輯電路有觸發器、 寄存器和計數器等。

2019-02-26 15:25:01 49621

49621 組合邏輯電路是任意時刻的輸出僅僅取決于該時刻的輸入,與電路原來的狀態無關。而時序邏輯電路不僅僅取決于當前的輸入信號,而且還取決于電路原來的狀態,或者說,還與以前的輸入有關。

2019-02-26 15:32:30 62614

62614 數字電路根據邏輯功能的不同特點,可以分成兩大類,一類叫組合邏輯電路(簡稱組合電路),另一類叫做時序邏輯電路(簡稱時序電路)。組合邏輯電路在邏輯功能上的特點是任意時刻的輸出僅僅取決于該時刻的輸入

2019-05-16 18:32:37 7636

7636

組合邏輯電路是無記憶數字邏輯電路,其任何時刻的輸出僅取決于其輸入的組合.

2019-06-22 10:53:20 46648

46648

在邏輯電路中,輸入和輸出只有兩種狀態,即高電平和低電平。通常以邏輯“1”和“0”表示電平高低

2020-06-19 16:51:17 11256

11256

邏輯電路在任何時刻產生的穩定的輸出信號僅僅取決于該時刻的輸入信號,而與過去的輸入信號無關,即與輸入信號作用前的狀態無關,這樣的電路稱為組合邏輯電路。

2020-08-08 10:40:00 5154

5154

所謂組合邏輯電路的分析,就是根據給定的邏輯電路圖,求出電路的邏輯功能。

2022-08-12 17:19:26 11078

11078

組合邏輯電路的特點是輸入的變化直接反映了輸出的變化,其輸出的狀態僅取決于輸入的當前狀態,與輸入、輸出的原始狀態無關。如果從電路結構上來講,組合邏輯電路是沒有觸發器組件的電路。

2022-10-24 16:02:32 965

965 數字電路的分類

(1)按電路結構分類

組合邏輯電路

時序邏輯電路:。

(2)按集成電路規模分:小規模、中規模和大規模。

2022-12-05 14:54:47 12

12 組合邏輯電路:用各種門電路組成的,用于實現某種功能的復雜邏輯電路。特點:某一時刻的輸出狀態僅由該時刻電路的輸入信號決定, 而與該電路在此輸入信號之前所具有的狀態無關。

2022-12-05 14:52:54 9

9 本文介紹開發組合邏輯電路時可能發生的意外開關事件,稱為危險。 本文是關于使用邏輯門進行組合電路設計和仿真的介紹性系列文章的第二部分。在上一篇文章中,我們介紹了 組合邏輯電路 以及如何簡化它們

2023-01-27 14:18:00 1078

1078

所謂組合邏輯電路的分析,就是根據給定的邏輯電路圖,求出電路的邏輯功能。

2023-03-06 14:37:26 1843

1843 數字電路根據邏輯功能的不同特點,可以分成兩大類,一類叫組合邏輯電路(簡稱組合電路),另一類叫做時序邏輯電路(簡稱時序電路)。組合邏輯電路在邏輯功能上的特點是任意時刻的輸出僅僅取決于該時刻的輸入

2023-03-14 17:06:50 4815

4815

時序邏輯電路分析和設計的基礎是組合邏輯電路與觸發器,所以想要分析和設計,前提就是必須熟練掌握各種常見的組合邏輯電路與觸發器功能,尤其是各種觸發器的特征方程與觸發模式,因此前幾文的基礎顯得尤為重要。 本文主要介紹時序邏輯電路的分析方法。

2023-05-22 18:24:31 1983

1983

?時序邏輯電路分為同步時序邏輯電路和異步時序邏輯電路兩大類。

2023-06-21 14:35:58 2538

2538

所謂組合邏輯電路的分析,就是根據給定的邏輯電路圖,求出電路的邏輯功能。

2023-08-16 09:15:23 3555

3555

當邏輯電路由多個邏輯門組成且不含存儲電路,對于給定的輸入變量組合將產生確定的輸出,則這種邏輯電路稱為組合邏輯電路。

2024-02-04 11:46:36 319

319

組合邏輯電路和時序邏輯電路是數字電路中兩種重要的邏輯電路類型,它們主要區別在于其輸出信號的依賴關系和對時間的敏感性。

2024-02-04 16:00:27 445

445 時序邏輯電路是一種能夠存儲信息并根據時鐘信號按照特定順序執行操作的電路。它是計算機硬件中非常重要的一部分,用于實現存儲器、時序控制器等功能。與之相對的是組合邏輯電路,它根據輸入信號的組合情況,立即

2024-02-06 11:18:34 497

497

電子發燒友App

電子發燒友App

評論