數十年來,光刻一直是關鍵的芯片生產技術。今天它仍然很重要。不過,在最近的SPIE先進光刻技術大會中,一些跡象顯示,光刻界及其客戶需要的微縮──字面上的微縮──事實上幾乎已經有點像心理安慰了。

焦慮、緊張和憂慮或許適合用來描述今天的光刻領域。但也許后頭還有更嚴重的苦難,因為三個主要的下一代候選光刻技術(NGL)──超紫外光(EUV)、無光罩和納米壓印──統統遲到。第四個NGL選項:定向自組裝(DSA)盡管來勢洶洶,但它畢竟仍處于探索階段。

擺脫光刻技術的沮喪看來遙遙無期。今天的193nm浸入式光刻技術仍然遠遠領先。業界一度認為193nm浸入式光刻會在32nm遭遇極限,但令人驚訝,看來該技術可擴展到1-x納米節點。不過,要獲得這些幾何圖形,芯片制造商必須采取更多、更昂貴的雙重曝光步驟。

而一度領先的下一代光刻候選技術EUV仍然頑固地因為缺乏光源能、阻抗和關鍵光罩以及量測基礎設施而延遲。結果是EUV的聲望持續下滑,并失去了在1-x納米節點大展身手的良機。

NAND閃存供應商之間存在著一種對EUV的迫切感,因為需要EUV來實現進一步微縮。NAND閃存廠商將193nm浸入式技術推進到了2-x納米節點,但他們遲早需要在1-x納米部份用到EUV技術。“我們的確曾對EUV技術充滿寄望,”SanDisk公司技術總監Tuan Pham說。SanDisk和東芝(Toshiba)在日本有一座合資的NAND晶圓廠。

當被問及是否擔心EUV的地位時,Globalfoundries資深院士Harry Levinson表示:“我是必須擔心。”Levinson也是該公司的光刻策略經理。

由于EUV技術持續落后于半導體的微縮腳步,設備制造商ASML Holding NV據報導仍在思考將EUV波長從13nm減少到6.7nm,以追上摩爾定律。這也意味著該產業必須發展更新和更昂貴的EUV工具技術和基礎架構,這讓該領域的專家們不寒而栗。

身處EUV技術陣營的領先芯片制造商,現在也對其他NGL技術持開放態度,如無光罩、納米壓印,甚至是未來的IC自組裝。“賭注非常大,”VLSI Research公司總裁Risto Puhakka說。“如果你做出錯誤的決定,就可能導致一場災難。”

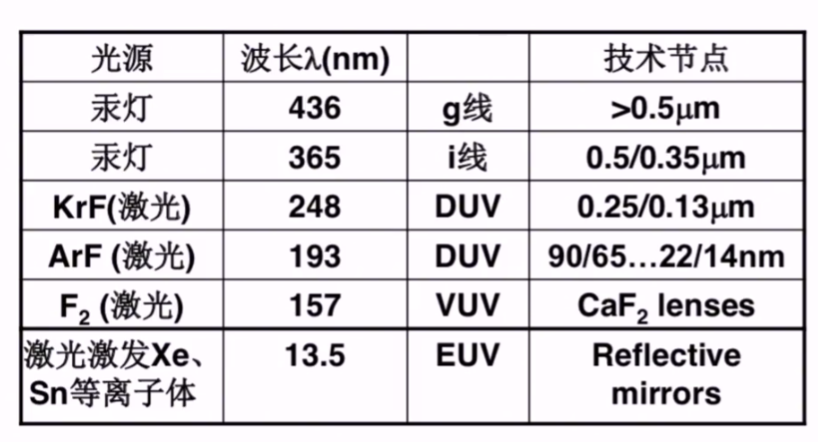

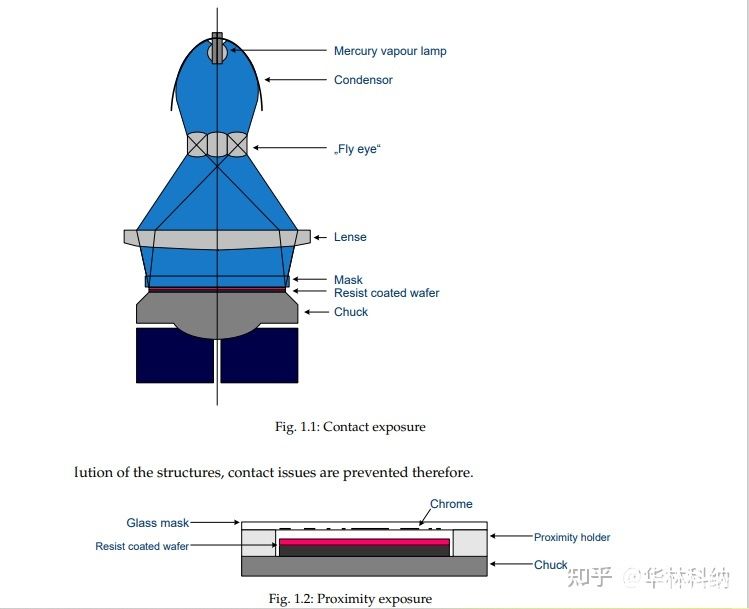

多年來,業界一直依靠傳統的光學光刻來維持摩爾定律的發展。但恐怕早在上世紀70年代,光學光刻便將發展動能用光了。

?

圖:業界預測的光刻技術發展路線圖

當時,芯片制造商認為他們需要昂貴的X光光刻以微縮元件。當光學光刻技術在20世紀80年代打破了1微米壁壘時,該技術推動了對X光的需求,但最終也將X光釘入了棺木。

而后,在1990年代,關于光學光刻是末代技術的擔憂再次浮現。當時有眾多針對65nm芯片制造及以下制程的NGL技術,包括:157nm波長、電子束、電子束投影光刻(EPL)、超紫外光、離子束、解剖刀掃描電子束等。而在過去十年內,高指數(high-index)、納米壓印、無光罩和自組裝也陸續問世。

隨著時間的推移,157nm、高指數、EPL、解剖刀掃描電子束和其他技術逐漸銷聲匿跡。今天,余下的四個競爭者是EUV技術、納米壓印、無光罩和自組裝。

在20世紀90年代,軟X光技術的出現成為推動EUV的關鍵。包括英特爾(Intel)、超微(AMD)、摩托羅拉(Motorola)和國家實驗室,開始在加州Livermore的Lawrence Livermore Labs開發EUV技術。

EUV:前景光明,道路曲折

EUV技術采用13.5nm波長,在真空室中加工。其光學元件基本上是一個可透過層間干擾方式反射光線的無缺陷透鏡。

EUV技術一度被認為可用于65nm節點的生產,但該技術不斷延遲。而總擁有成本(COO)仍是一大問題,因為與現行的光學'光簇'(photo-cluster)售價7,000萬美元相比,今天EUV的'光簇'(photo-cluster)售價高達1.2億美元,Globalfoundries的Levinson表示。

?

圖:EUV光刻技術原理

ASML、佳能(Canon)和尼康(Nikon)是三大主要的EUV掃描器制造商。但最近,佳能跌出了領先光刻廠商排行榜。

剩下的兩家廠商ASML和Nikon則有不同的策略。ASML公司正努力讓EUV技術能應用在22nm節點,但Nikon認為在16或11nm節點前,該技術都尚未就緒。“EUV生態系統也會延遲,”Nikon的新世代技術開發部門總經理Yuichi Shibasaki說。

尼康一直在開發的EUV工具稱為EUV1,這是一套生產系統,據報導該系統預計在2012年左出貨。

ASML公司的策略相對明確。如同其193nm浸入式策略,該公司趕在Nikon之前向客戶交付試產的EUV技術工具。ASML希望客戶將藉由這套試產工具獲得經驗,從而逼使Nikon退出市場。

截至目前,ASML已出貨兩套alpha EUV工具,一套交付給Albany Nanotech,另一套則交貨給IMEC。ASML最近也對三星電子推出了其首款獨立的預生產EUV工具NXE:3100。ASML公司剛剛付運另外一套系統給IMEC。整體來說,ASML現有六張NXE:3100訂單。

NXE:3100據聞擁有27nm解析度,數值孔徑(NA)為0.25,場尺寸為26nm,光刻壘對(overlay)為4nm,flare則少于5%。這套工具售價將近1億美元。

該工具的目標是在今年底達到每小時60片晶圓的吞吐量。但目前它的吞吐量每小時僅5片晶圓。EUV工具每小時約需200W的功率來處理100~150片晶圓。目前,ASML的EUV工具僅運作在10W左右。

分析師認為,ASML公司在推動EUV的過程中已經做了非常好的努力。現在,該公司的EUV客戶正在等待由幾家第三方合作伙伴開發的光源能。

盡管問題頻傳,但ASML對光源供應商付出了無比耐心。“我們有三家全力合作的廠商,”ASML執行副總裁暨首席產品和技術長Martin van den Brink說。

有兩家廠商為ASML的NXE:3100工具提供光源能:Cymer公司和Ushio公司。Cymer已經開發了基于雷射激發電漿型(laser-produced plasma, LPP)技術的光源能。據ASML表示,Cymer的LPP光源能是在11W的持續功率上運作。

競爭對手Ushio則正在開發一種基于放電技術的光源能。ASML稱Ushio的光源能已達到12W功率。另一家廠商Gigaphoton公司則展現了20W的功率。

“Cymer已經售出了四套EUV光源能給客戶,而且正準備推出第五套,來自三星的初步反饋指出混合圖案相當良好,但吞吐量很差,”Barclays Capital分析師CJ Muse在一份報告中提到。

迫切需要光源能

我們的調查反饋仍然有差異,當前的EUV吞吐量大約每小時7-15片晶圓左右,遠低于每小時60片的目標,Muse說。不過,這仍然讓Cymer領先其主要競爭對手Gigaphoton約六個月。

另一個問題是,當ASML和Nikon在2012年出貨其EUV工具時,EUV光源必須達到要求的目標。

“根據技術藍圖,HVM Gen 1 Cymer光源的目標是達到105W的輸出功率;HVM Gen 2約達250W(根據目前揭露的設計細節),而HVM Gen 3則約350W;”Muse說。“也就是說,Cymer的腳步有點落后于功耗調整。他們目前的光源是運作在11W左右;該公司主管認為今年中他們將達到約22W,實驗室的性能表現約為80W,而2011年中可望實現100W功率并推出產品,希望2011年第四季能交付給客戶。”

放電激發電漿型(discharge-produced plasma,DPP)和激光激發電漿型(LPP)光源技術將以平均10~20W的曝光功率水平持續對ASML的NXE:3100設備作出貢獻,咨詢公司EUV Litho Inc.總裁Vivek Bakshi表示。

“我估計在2011年該數字將增加一倍達到40W,在2012年之前都無法實現100W的目標,”他說。“所以我們可以預期100W的光源與NXE:3300工具同時問世,這是一件好事,因為100W可支援每小時80片晶圓的吞吐量,一些專家認為必須為量產做準備,”他表示。

這是個好消息。現在,輪到壞消息了。“我相信,目前的光源技術版本可以達到100~150W。然而,就算達到100W,我們還是需要更多的創新,以獲得150W和發展250W光源,我們還需要思考更多。”

不過,最大的問題是,EUV技術是否仍是芯片生產的首要考量。而在這其中,EUV技術仍然落后遂成為關鍵。SanDisk-東芝已經推出24nm的NAND元件,并宣布今年稍晚將推出1-x納米產品。

對于,SanDisk與東芝的合資工廠使用193nm浸入式光刻技術,再加上雙重曝光技術生產24nm的NAND元件,稱之為隔層(spacer)技術,SanDisk的Pham說。據報導,Hynix、美光(Micron)和三星都在2-x納米NAND生產中使用了類似技術。

在發展1-x納米節點早期階段,有跡象顯示NAND閃存廠商SanDisk-東芝可能需要延長193nm浸入式技術,直到EUV準備好,Pham表示。

另一家廠商──三星,則一直努力推動將EUV技術導入DRAM和閃存的生產。三星認為DRAM將是率先使用EUV的應用,理論上這適用于下一代元件中難以致密的接觸孔成像和間隔。

在邏輯方面,英特爾公司計劃將目前的193nm浸入式光刻技術拓展到14nm邏輯節點,預計在2013年下半年實現。然后,這家芯片巨擘希望在10nm節點使用EUV技術,該目標預計在2015年下半年達到。

英特爾的10nm節點發展已歷時四年多,該公司目前正在制訂相關設計規則,但延遲的EUV依然未能參與此一盛晏。“EUV趕不及參與10nm節點設計規則的定義,”英特爾光刻技術總監Sam Sivakumar說。(參考閱讀:英特爾10nm設計規則初定,EUV技術恐錯過良機)

另外兩家代工競爭對手──Globalfoundries和臺積電(TSMC)則有不同的光刻技術策略。

一些人認為EUV技術在6.7nm波長的基礎上將是更可行的解決方案,這很有可能推動次1nm元件的實現。但像13.5nm EUV、6.7nm等技術卻面臨著許多相同障礙:光源能、測量等。

基于6.7nm波長的EUV技術是一種有趣的概念,但業界至今甚至仍未征服13.5nm技術,TSMC納米成像部門副總裁Burn Lin觀察。

那么,EUV技術是不是有可能永遠無法成為商業上可行的量產方案,即使投注了大量的時間和金錢?“當然,”Peterson Advanced Lithography公司總裁暨主席Jim Peterson說。Peterson Advanced Lithography是一家提供光刻產品和服務的公司。

“如果一項技術具有競爭力,那么,在進入商用化之前,它就必須取得巨大的進展,”日本凸版印刷(Toppan Printing)美國子公司Toppan Photomasks技術長Franklin Kalk說。

?

圖:造價高昂的EUV光刻系統

Kalk堅持,EUV光罩在這點上并沒有遭遇瓶頸;EUV光罩的成像非常簡單,但直到EUV進入量產,業界是不會知道哪一個步驟是必須在EUV光罩上進行缺陷管理的,他表示。

Kalk和一些專家指出,EUV技術的商業化生產并不是一個問題。可能有很多公司口袋很深,也或許只有少數幾家,但這些公司將繼續建立先進的晶圓廠并持續EUV的研發,Kalk說。“這必然會發生。”

不過,Kalk也與其他人一樣,關注EUV的潛在吞吐量。目前的共識是EUV生產工具必須達到至少每小時65~80片晶圓的吞吐量,才能讓EUV具經濟效益。雖然根據Kalk的建議,這將是初期令人滿意的吞吐量,但長遠來看,吞吐量也將有所改善,他說。

對許多人來說,EUV是唯一的下一代光刻技術。“光學光刻已經接近尾聲了,”VLSI Research的CEO Dan Hutcheson和該公司的Puhakka表示。他們指出,短期內EUV是昂貴的,但也只有它才能確保競爭力。

無光罩光刻:研發進度落后,商業化進程緩慢

EUV比其他的NGL技術獲得更多進展。過去十年內,一些公司開始研究新一代電子束技術,稱為無光罩光刻(ML2)。包括IMS、KLA-Tencor、Mapper、Multibeam和其他公司都各自進行開發,他們的方法是在單一機臺上使用多波束。理論上,ML2應該能克服與單一波束直接寫入相關的吞吐量問題。

無光罩仍然缺乏資金且進度落后。要讓無光罩技術商用化,業界至少要募到1億美元,Design2Silicon(D2S)總裁兼CEO Aki Fujimura表示。

這個數字可能還被低估了。在今年的SPIE上,新創的無光罩公司Multibeam Corp.介紹了互補電子束光刻(CEBL)技術,及甚努力推動無光罩技術商業化的努力。

晶圓廠設備巨擘KLA-Tencor也提出了更多正在為無光罩技術商業化努力的細節,包括反射電子束光刻(REBL)技術在內,該計劃由KLA-Tencor和DARPA公司贊助。

最初的工具使用使100 KeV源、旋轉臺和一個數位圖案產生器(DPG)。旋轉臺是一個六晶圓平臺。該DPG是一款CMOS芯片,帶有小型、獨立可控的金屬單元或畫素陣列,它主要用途是作為電子鏡陣列。

該工具允許100萬個'細光束'(beamlets)同時被暴露在芯片上。REBL的目標是在16nm節點實現晶圓成像,KLA-Tencor的REBL資深總監Paul Petric說。

最初,單柱型工具使用'靜態DPG'芯片。KLA-Tencor正在開發一種基于CMOS的新型DPG,它由28個金屬層和1,454個焊盤組成。然而,該公司目前在焊盤方面有些困難,他表示。

在商業化以前,REBL看來還有很長的路要走。荷蘭的Mapper Lithography Bv公司在今年的SPIE上并沒有提出太多實質性的進展報告。該公司提出的成果包括使用其110電子束的系統在32nm半間距節點進行晶圓成像。

納米壓印、定向自組裝:仍未準備好迎接黃金時代

Mapper的pre-alpha系統獲臺積電采購,該系統每小時吞吐量目前為10~20片晶圓。Mapper推動其技術邁向量產的計劃,是建立一個約由10套工具組成的叢集,以達到每小時約100片晶圓的吞吐量。

另一個候選的NGL技術──納米壓印,同樣進展緩慢。包括EV Group、Nanonex、Nanolithosolution、Molecular Imprints Inc.(MII)、Obducat、Suss都投入了納米壓印領域。

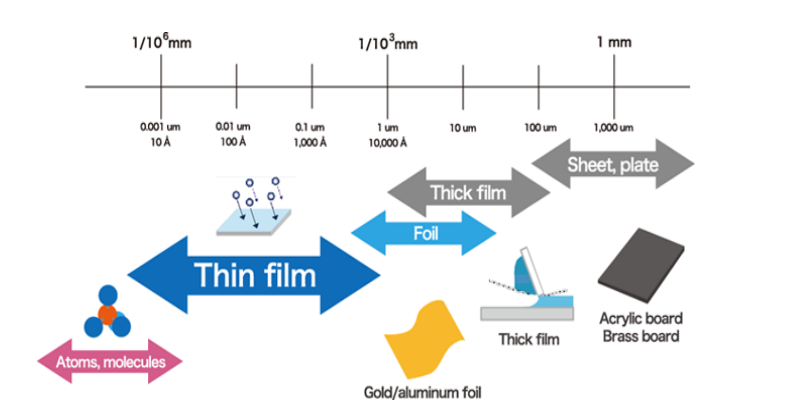

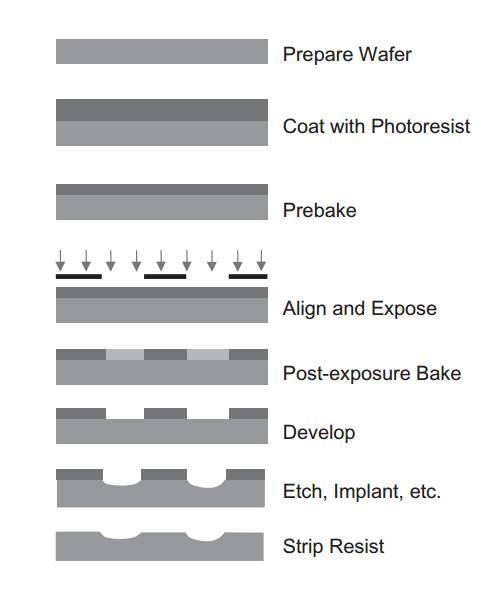

納米壓印技術并未使用昂貴的光學元件,而是采用簡單的壓印或熱鑄制程,在元件上產生特征圖案。這種制程先從模板或鑄模著手,然后再由電子束工具根據1:1比例的縮減機制在模板上選擇特征圖案。使用納米壓印工具──就像一臺巨大的壓印機──模板被壓向加熱的單層基板,最終形成微型的特征尺寸。

但納米壓印的低吞吐量、光刻壘對(overlay)、缺陷率等缺點,使其還無法成為主流制程。

出于這些原因,納米壓印一直無法用于芯片生產,至少現在還沒有辦法。它仍然停留在研發實驗室或大學研究階段。

幾年前,MII公司出貨了納米壓印工具給東芝公司。但在今年的SPIE上,東芝表示納米壓印仍然沒有準備好迎接其黃金時代。

但另一方面,納米壓印也正在取得進展。同樣在SPIE上,Sematech“展示了具體缺陷率0.09cm2的良好結果,”MII公司總裁暨CEO Mark Melliar-Smith表示。“由于這已經低于東芝所設定的0.1cm2水平,我認為我們正在走向成功。”

MII展示了多款已在過去12個月內出貨的工具平臺。包括一款針對CMOS的工具,“5xx系列每小時吞吐量為20片晶圓,而且擁有良好的光刻壘對(overlay),”他表示。

但納米壓印在其最大的潛在市場──硬盤(HDD)──也有可能延誤。目前硬盤制造商使用濺鍍技術在硬盤上實現磁性介質,但這些產品很快地就會遭遇1TB容量的極限。

大約在今年底左右,硬盤制造商們將使用一種名為'位元規則介質'(bit-patterned media)的下一代技術來生產硬盤;這種技術據稱可將傳統的儲存容量擴展到10TB。

在爭相取代EUV的NGL技術中,定向自組裝(DSA)在今年SPIE上的表現最為搶眼。DSA技術概念聽起來像科幻小說,它是將塊狀共聚合物(block copolymer)或是聚合物混合物(polymer blend)沉積在基板上,通常采用旋轉涂布,并經由退火過程以'指揮'其形成有序的結構。研究人員指出,DSA相容于傳統的193nm光刻設備,不再需要雙重曝光步驟。

但DSA仍處在研發階段,但已經有一些機構提出令人振奮的報告,包括IBM、應用材料等。JSR稍早前也才針對次20nm半間距節點推出了DSA技術,這是該公司與IBM研發協議的一部份

電子發燒友App

電子發燒友App

評論