在 SoC 上集成更多功能的難度越來越大,這促使著整個芯片行業對新封裝方法的探索,其中既有更復雜的集成 SoC,也有多芯片封裝等形式的先進封裝。

截至目前,這一領域的大部分工作都是高度定制化的。但隨著先進封裝日益主流,差距也在開始出現。

“IC 封裝在過去 10 年中取得了非常顯著的進展,但 IC 封裝今天所能應對的復雜度還相當有限。”eda2asic Consulting 總裁 Herb Reiter 說,“正如我們所見,價值創造正越來越多地轉向封裝而且封裝與硅方面的合作也越來越多,我們遇到了一個讓人頭疼的大問題,因為目前還沒有什么 die-封裝聯合設計流程。從硅領域向封裝領域輸送信息是非常困難的,而硅領域要從封裝領域獲取反饋信息甚至還要更加困難,但這樣才能聯合優化這兩個領域。”

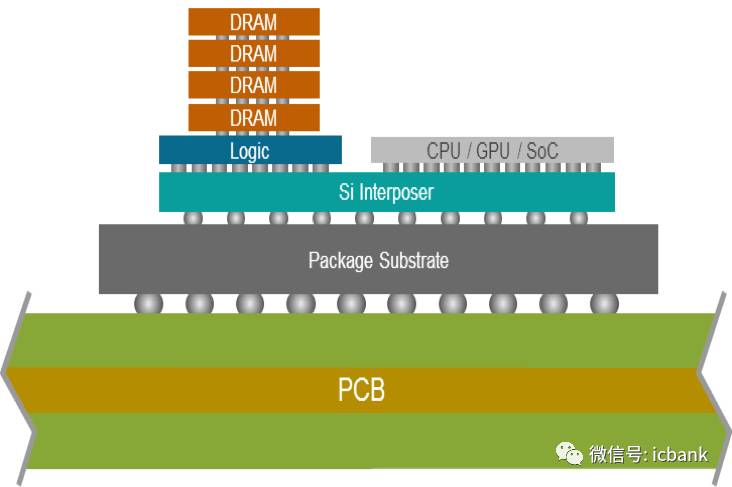

圖 1:超越摩爾定律,來自 Cadence

要取得成功,封裝必須接近由摩爾定律擴展所帶來的 PRA 收益,而更快的上市時間還能帶來額外的收益。

“但隨著工程開發團隊成功實現這些多 die 異構設計,在一個封裝中放入更多內容的難度也會越來越大。”西門子一個業務部門 Mentor 的產品營銷經理 Keith Felton 表示,“在紙面上這看起來很合情合理。你可以混合技術節點、工藝,你可以將具有不同功能的不同異構芯片放到一起,將它們與 interposer 一起組合到同一個封裝中,然后基本上你就得到了一個非常好的可工作的子系統,而且幾乎就像是在單個 SoC 中一樣高效。理論上,這僅需遠遠更低的成本和風險就能接近 SoC 的性能表現。它的面積會多一點點,高度也會多一點點,但現在他們正在解決這些問題。”

他們想在每個方面都能趕上。“甚至英特爾也脫離了更小更小更小的‘經典’摩爾定律算法,因為這個東西沒效了。”Optimal+ 全球營銷副總裁 David Park 表示,“他們做的是開始進軍多芯片封裝、多芯片模塊,因為這比試圖將所有東西都放在 28nm 等節點上要容易得多。‘我們會將數字邏輯放在 28nm,但讓模擬部分留在 45nm,因為這樣效果很好,然后我們會在基板上將它們連接起來。’這差不多就是人們繞過摩爾定律的方式——通過某種類型的 interposer 將多個芯片組合到一起。這樣他們就能將具有收益的小特征尺寸和能提供更高魯棒性和質量的更大特征尺寸組合到一起。”

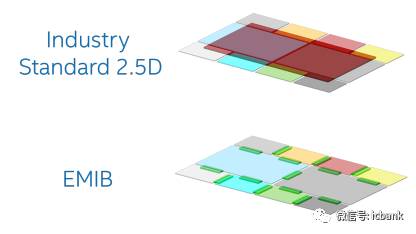

圖 2:英特爾的 EMIB 方法,來自英特爾

集成方面的問題

盡管這項工藝的細節設計和布局部分已經得到了很好的理解,但要將芯片與 interposer 放到一起并找到正確的連接方法卻并不輕松。“過去這通常是在紙面上完成的,還有每個人都在談的 bump ball spreadsheet,這是這個工藝的代名詞。”Felton 說,“但這是靜態文檔,不是真正的設計工具。它們無助于你了解其中的權衡。它們不會給你的連接是否正確提供任何反饋。它們只是記錄了你按順序做的事情的文檔,以便你能將其提供給別人,所以它們只是靜態的文檔,實際沒什么用。盡管可能看起來很不錯,但從信號集成的角度和熱分析的角度看,這可能是無效的。”

一旦物理布局完成,就要驗證設計,這又會增加潛在的雷區。如果一開始就在邏輯連接各個部分之間出了錯,當你進入最后的設計階段并在驗證過程中發現問題時,就會需要大量返工。Felton 說:“如果你和你的代工廠和 OSAT 鎖定了生產時間,這就會變得非常困難。你實際上就會錯過他們的生產計劃安排。”

為了避免這些問題,一些設計團隊已經開始關注在系統層面上創造前期設計原型——基本上就是創造整個設計的數字模型。這讓他們可以從頂部 die 一直到 package ball 或甚至到印制電路板上一路跟蹤導通性,而且也可以在該模型上修改設計,然后將其送入仿真工具。但從多個來源組合數據以構建整個封裝結構的邏輯原型并不是簡單的工作。

Felton 說:“即使你是一家無晶圓廠半導體公司,你也不需要設計放入設備的所有芯片。你可能會從一些公司那里得到內存堆棧或 memory cube,你可能會使用你自己設計的處理器或微控制器,但也會使用其它現成可用的器件。通常你需要 Verilog 網表(netlist)這樣的東西,你也需要其它 die 的某種形式的 footprint 模型,實體 footprint 通常是以 GDS 形式提供的。你可能會得到一個 SPICE 網表或一個 Verilog 頂級網表,但你還是要將所有這些組合到一起并且保證你的組合方式是正確的。”

此外,針對這些組合到一起的單個器件的邏輯模型,必須為這種物理數字模型進行布局與原理圖驗證。

一旦創造出了驗證過的模型并且得到了正確的邏輯驗證,那就有可能開始要在 die 的封裝方式上做一些權衡——用并排結構還是垂直結構、應該使用什么類型的封裝和互連。

Felton 說:“一些人試圖使用原理圖捕獲(schematic capture)。他們試圖繪制符號來表示 die,他們試圖導入 Verilog 網表作為 die 的主體。然后他們會在上面連接外部端口。你又帶來了另一層不正確連接的風險。這有很大的風險。也可能有好處,你可以將其看作是一副生動的原理圖,這可能對工程師而言非常有用。但將不同的數據部分放到一起,正確連接,然后以此為基礎向前發展,這個過程中存在非常多的風險。通常他們會發現,在他們進入實體設計階段時會有 LVS 錯誤,所以他們必須返回去調試這個錯誤出現的確切位置。是不是原來的 Verilog 網絡不正確,還是在構建原理圖時 Verilog 端口映射得不對?人們已經試過使用原理圖了,但這沒法提供任何實體方面的理解,因為這是平面的靜態的,沒法說明在 3D 情況的狀況。”

人類因素

說服設計工程師使用新方法也并不容易。

Felton 說:“如果你看看我們今天的客戶,我可以說有 30% 在嘗試使用新方法,但這要在設計工藝和設計流程上做根本性的改變。首先,你需要讓這些設計師用那種方式思考,這可能需要時間。他們已經知道該怎么做一些事了。他們知道這并不完美,但是有效。而且他們知道在任何不得不改變的時候,都只會帶來更大的風險,所以他們會后撤,直到他們解決這個問題或遭遇災難性的失敗。”

另外設計和封裝團隊往往工作在不同的管理層面上。這些團隊往往會被人為地拉入一個組,這么做并不總是很有用的,因為這個組中的人往往分散在世界的不同地理位置。這里的關鍵是要能安全地來回傳遞設計的改變和模型。

通過為他們定義一種更好更智能的數據交換流程,很多公司才能采用這種方法,而不是迫使他們的團隊聚到一起或處在同樣的管理結構層次中。而這又會真正落入到所有數據的產品生命周期管理中。

“在 SoC 設計領域的 IC 方面,我們喜歡說這是一個幸福大家庭。”Mentor 技術營銷工程師 John Ferguson 說,“但實際并不是。其中有很多溝通問題。我們有一些設計團隊在研究不同的 IP 模塊,與此同時還有其他一些人在研究如何將這些 IP 在 SoC 中連接到一起。而且即使有最好的意圖,也不會百分之百正確,很大程度上是因為他們是各自為戰的團隊。一般他們會在開始時聚在一起研究出規格,似乎每個人都想主導并且認為他們做的事別人都同意。但是之后你會發現中間會有些溝通不暢。我認為這種情況并不會真正改變。關于誰在做什么、誰負責什么以及怎么溝通上都一直不會連貫一致。”

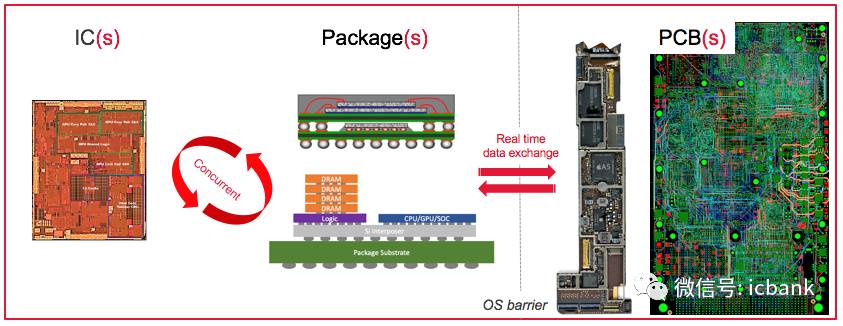

圖 3:先進封裝的現有流程,來自 Cadence

而且隨著先進封裝的發展,難度還會越來越大。

“項目規模越大,讓人們合作的難度也就越大。”Flex Logix CEO Geoff Tate 說,“單個芯片設計團隊可能會有數百人,而封裝團隊可能在另一個樓層或另一棟樓里——或者另一個城市。所以當所有東西都變得非常大非常專業化時,緊密合作的能力就會下降。在一起緊密工作的團隊總是有益的。在團隊規模非常大的時候,這事兒就會非常難。當你的樓里面有 500 人時,你就沒法讓他們一起緊密工作。其中一些會在一起緊密工作,另一些則分散在不同的多個樓層。當你的團隊很大的時候,就會遇到組織上難題。”

不過,也可能會出現變化。Cadence 的 IC 封裝和跨平臺解決方案產品管理總監 John Park 說芯片設計團隊、封裝設計團隊甚至電路板設計團隊都已經開始更緊密的合作了。他說過去 7 或 8 年來大型的半導體公司都是這樣。

直到最近,他們的合作還基本上沒有在信息協同設計流程中共享 EDA 工具、微軟 Visio 制圖、PowerPoint 幻燈片、Excel 電子表格、電子郵件和白板制圖。

“但至少他們已經認識到他們不能只設計一塊芯片然后就扔過墻壁給設計團隊,然后讓他們處理各種問題,然后再扔過墻給電路板設計團隊。”Park 說,“所有的大公司都意識到這種方法已經不再可行。事實上,英特爾在 7 或 8 年前就在一場會議上做了一篇論文說他們正在使用那種方法,這使得他們的封裝成本高于他們的芯片成本。很顯然這殺死了這個項目。英特爾是這一趨勢的最早采用者之一,這個行業中很多人都說這是‘探路’,其中許多做芯片的人和做封裝的人甚至做電路板的人都開始在芯片流程早期進行合作,同時規劃應該以什么封裝技術為目標進行設計”

展望未來,對 3D 堆疊的興趣和采用肯定會在半導體系統上帶來更大的價值,并為 3D 堆疊上智能分區能力等 EDA 創新帶來機會。Park 說:“這不只是為了在單個技術上規劃單個芯片。它也可以在一個堆疊上做三個芯片的智能布局規劃,以便根據產生熱量和電氣性能等要求,確定哪個模塊應該位于堆疊中的哪塊芯片上。這是一個有價值的領域。這幾乎就像是引入芯片的 RTL 描述,但可以用于每個垂直堆疊中的 2 個或 3 個芯片。”

-

半導體

+關注

關注

335文章

28702瀏覽量

234207 -

數據

+關注

關注

8文章

7249瀏覽量

91320 -

邏輯

+關注

關注

2文章

834瀏覽量

29728

發布評論請先 登錄

先進封裝技術:3.5D封裝、AMD、AI訓練降本

日月光擴大CoWoS先進封裝產能

簡要解析HDMI 2.2標準

先進封裝技術-19 HBM與3D封裝仿真

一文解析全球先進封裝市場現狀與趨勢

先進封裝技術-17硅橋技術(下)

先進封裝技術-7扇出型板級封裝(FOPLP)

先進封裝技術的類型簡述

先進封裝技術綜述

簡要解析先進封裝的優點和缺陷

簡要解析先進封裝的優點和缺陷

評論