先進封裝技術(Semiconductor Advanced Packaging) - 1 混合鍵合技術(上)

先進封裝技術(Semiconductor Advanced Packaging) - 2 混合鍵合技術(下)

先進封裝技術(Semiconductor Advanced Packaging) - 3 Chiplet 異構集成(上)

先進封裝技術(Semiconductor Advanced Packaging) - 4 Chiplet 異構集成(下)

先進封裝技術(Semiconductor Advanced Packaging) - 5 TSV 異構集成與等效熱仿真

先進封裝技術(Semiconductor Advanced Packaging) - 6 扇出型晶圓級封裝(FOWLP)

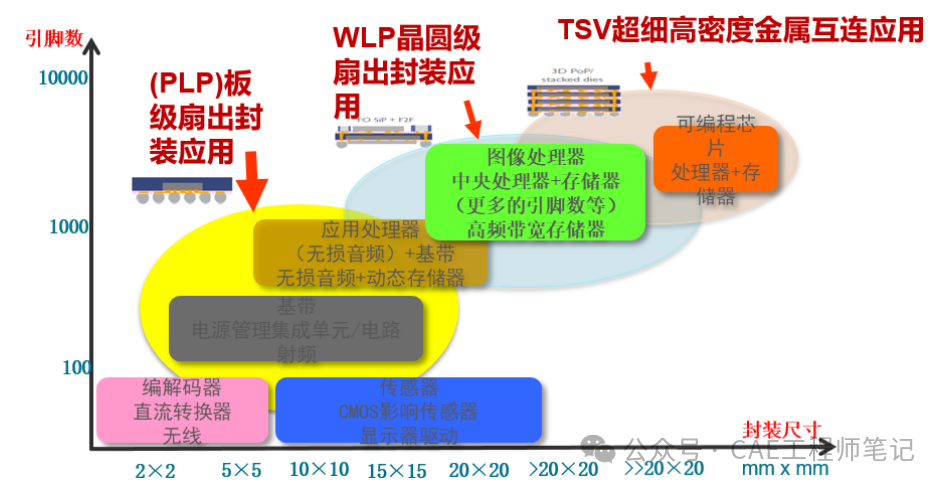

封裝技術從早期到現在的發展都是為了提高半導體相關產品的價值,不斷增加芯片的功能,增加 I/O 數從而將更多的功能整合到終端產品中去。但是,由于摩爾定律極限的不斷逼近使得電子產品的性能已經不能再通過縮小芯片的尺寸來實現,甚至不斷增多的 I/O 引腳數已經使得基板下面不能再容納更多數目的錫球,而如果通過將錫球的尺寸減小這又將帶來成本的不斷增加。因此,扇出型封裝技術的提出就是為了突破芯片與基板面積之間所帶來的限制。

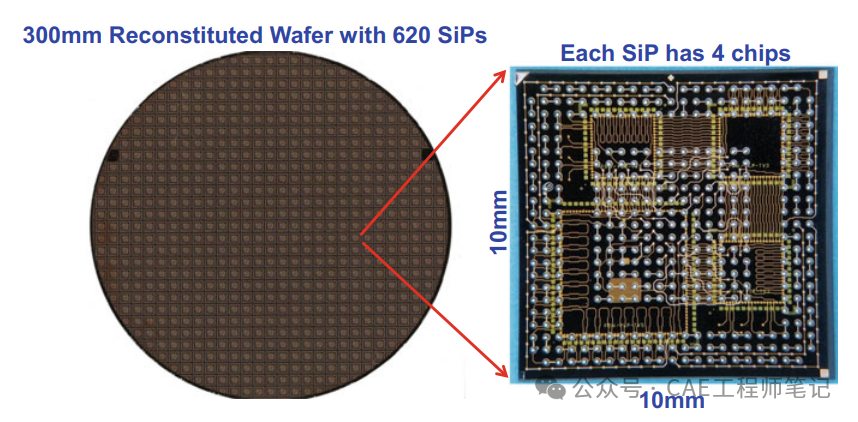

在此背景下,FOWLP(Fan-Out Wafer Level Package)作為一種新興的封裝技術,在商業領域得到了廣泛的使用。該技術具有完善的生產過程,可滿足各種不斷變化的需求。2016 年,蘋果公司將 FOWLP 成功地運用到了其最具代表性的產品 iPhone7 的處理器和模塊中。

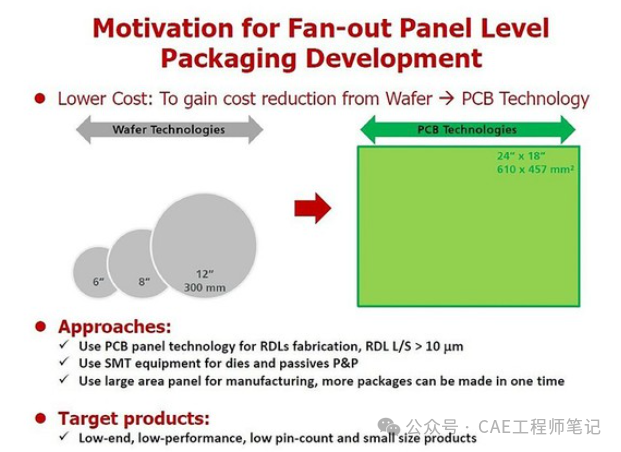

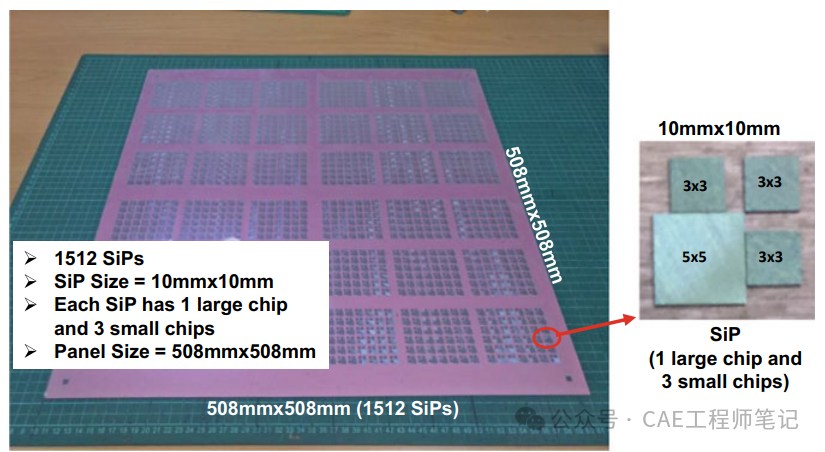

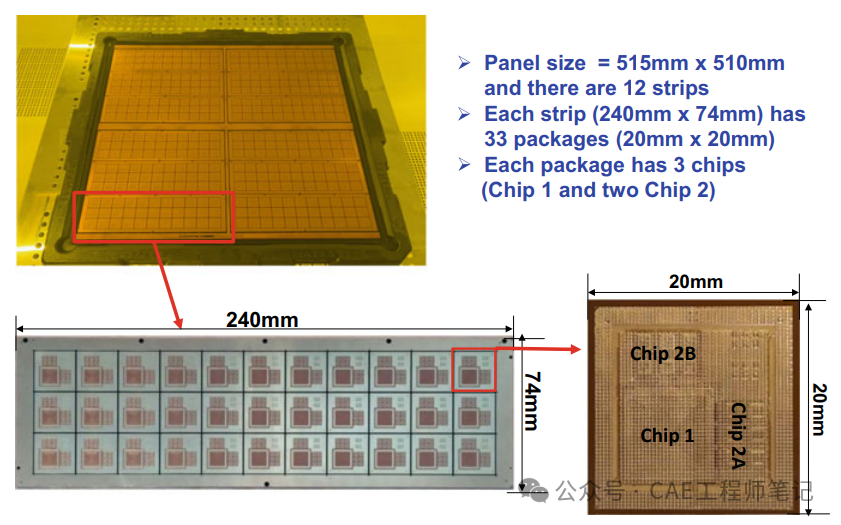

目前扇出型晶圓級封裝技術主流的晶圓尺寸為 12 寸,但是為了能在更低的生產成本下有更高的實際產出量,生產方向朝著 18 寸晶圓進行,但是生產過程中也存在很多困難,比如制造 18 寸晶圓所使用的設備需要更新換代,這就需要投入大量的資金,且生產過程中的工藝要求也亟需有所提升。因此,工程師們便考慮通過使用尺寸更大的面板級封裝去代替晶圓級封裝,這樣可以更好地利用其封裝規模大和使用效率高的優勢。

采用面板級封裝去替代晶圓級封裝,若在工藝技術已經完備的情況下,其生產成本可以有很大幅度的降低。同時相比較晶圓級封裝來說,面板級封裝也有著更加高的成品合格率。此外,面板級封裝生產所使用的生產設備、技術支持和所涉及到的專業知識都和晶圓級封裝以及 PCB 板大相徑庭,這也使得面板級封裝具有更加良好的前景和發展空間。隨著多種因素的共同作用,扇出型板級封裝(Fan-out Panel Level Packaging, FOPLP)迅速發展起來。

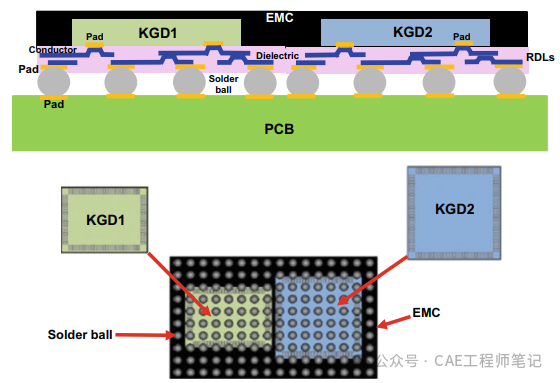

FOPLP 是相對于 FOWLP 來說的,它將晶圓基板替換為面板基板,并采用扇出型封裝的方式進行封裝,從而實現更高效、更精確的產品。FOPLP 所使用的工藝生產方法與 FOWLP 相似,不同的是FOPLP 具有更高的利用率、更低成本的潛力。

FOPLP 與 FOWLP 并不是競爭關系,而是相輔相成,目前行業內 FOWLP應用于 I/O 密度高和細線寬/線距的高端應用,而扇出型板級封裝 FOPLP則關注于 I/O 密度低和粗線寬/線距的低端或中端應用,這樣 FOPLP 可以更好的發揮成本優勢,基于扇出型板級封裝 FOPLP 技術,可以實現更高的封裝組件密度和性能。

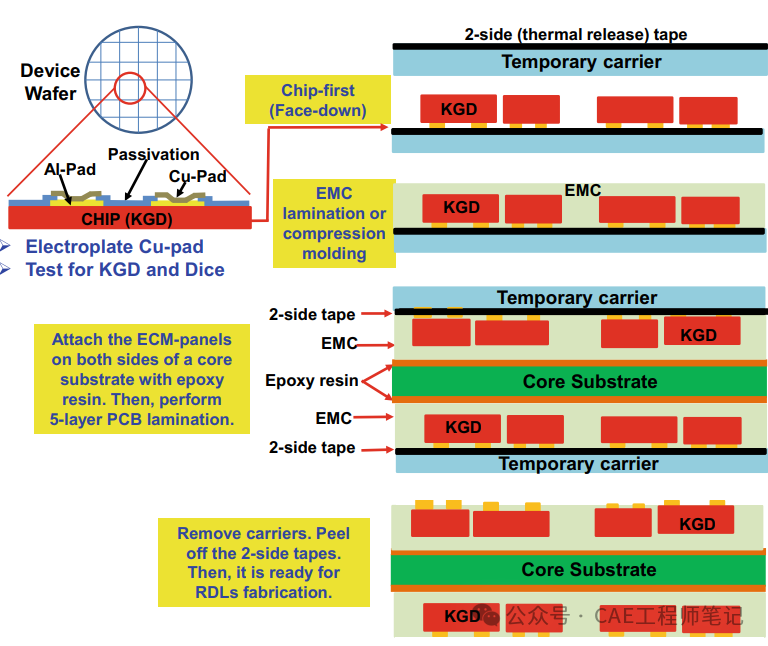

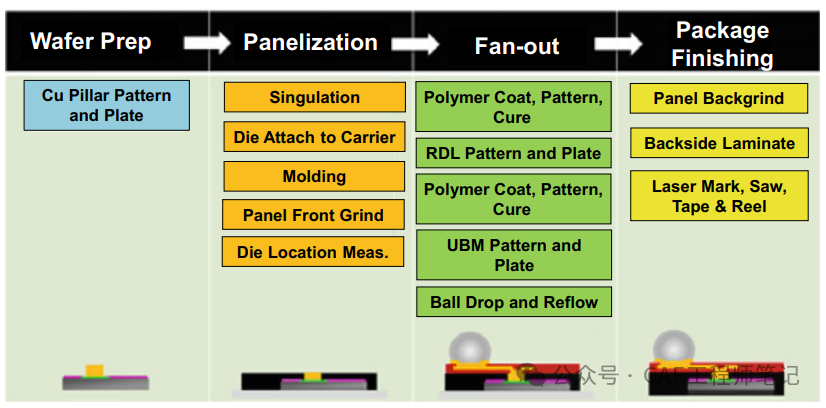

FOPLP Chip First 工藝通常有 Face up 與 Face down兩種形式。

Chip-First and Face-Down

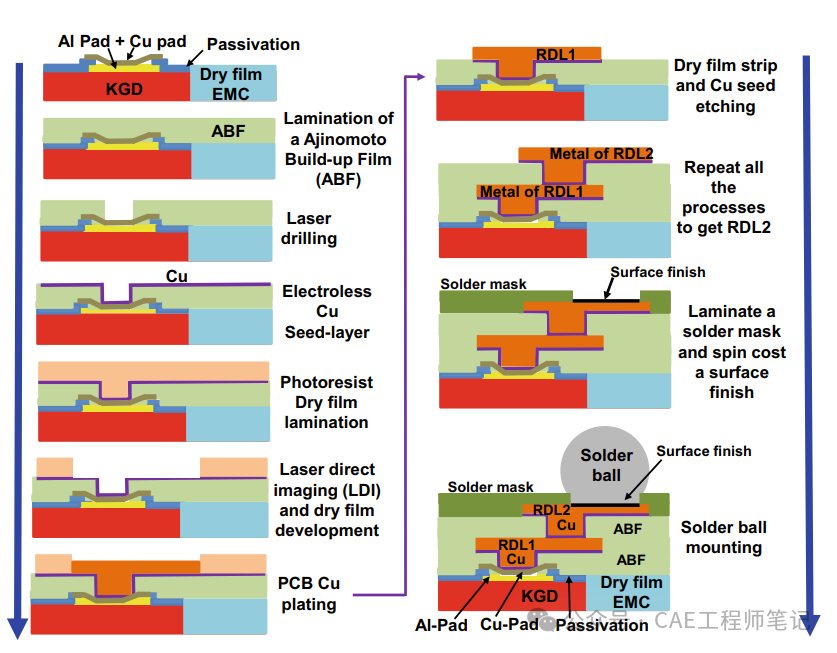

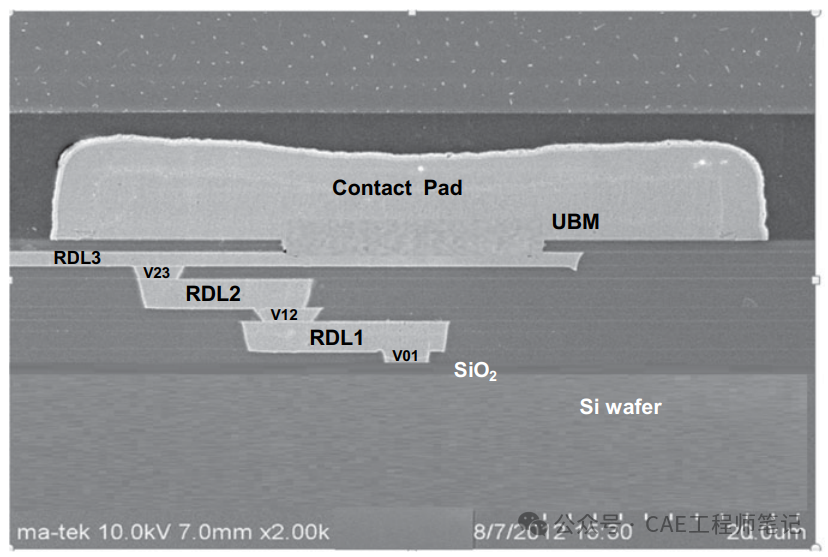

對于 Face down 來說,芯片 I/O 面朝下,粘貼在附帶臨時鍵合膠的載板上,然后進行塑封固化和移除載板,接著在芯片 I/O 面熱壓一層介電層,對 I/O 口處進行激光開孔,露出芯片 I/O 口并清除殘余介電層,后續采用真空濺射生成 Ti/Cu 種子層,在種子層上熱壓一層干膜,進行曝光、顯影、電鍍做出線路層,最后進行退膜處理,除去多余種子層,在線路層上覆蓋感光油墨以及切割成單個封裝體。

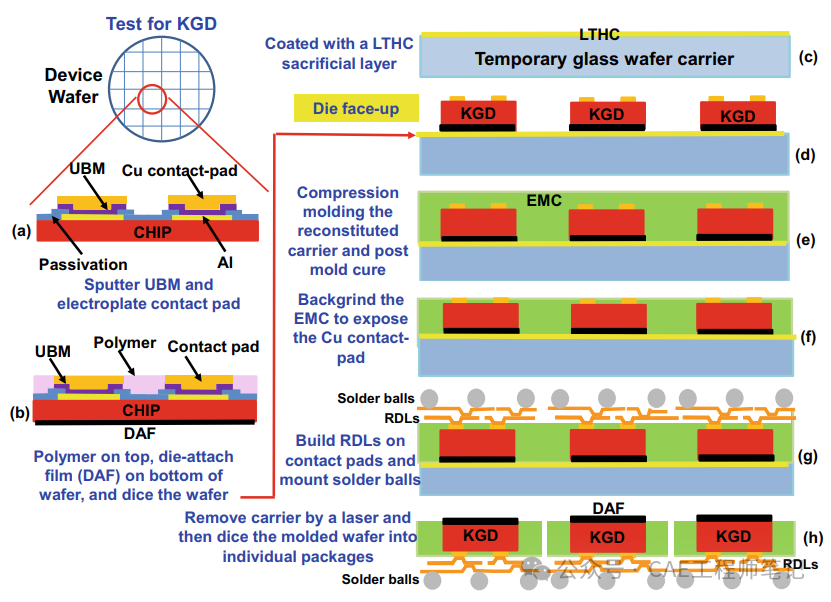

Chip-First and Face-Up

對于 Face up 來說,芯片面朝上粘貼在臨時鍵合膠上,但此處芯片 I/O 口需先具有銅柱,然后進行塑封固化和研磨露出銅柱,接著在銅柱上熱壓一層介電層,對 I/O 口處進行激光開孔,露出芯片 I/O 口并清除殘余介電層,后續采用真空濺射生成 Ti/Cu 種子層,在種子層上熱壓一層干膜,進行曝光、顯影、電鍍做出線路層,最后進行退膜處理,除去多余種子層,在線路層上覆蓋感光油墨以及切割成單個封裝體。

以上兩種 Chip First 封裝工藝中存在以下幾項挑戰性問題:

其封裝產量由 RDL 的生產良率決定;

芯片表面的 I/O 間距會受到芯片與 RDL 之間對準誤差的限制;

重構晶圓中需要可以低溫固化的樹脂,可能會降低封裝可靠性;

RDL 的工藝制程一般都在 10 μm 以下,在制作 RDL 前,重構晶圓的輕微翹曲或芯片偏移均會嚴重影響 RDL 的生產良率;

一旦發現有部分 RDL 損壞,損壞部分的RDL 對應的 KGDs 也無法再利用,容易造成資源的浪費。

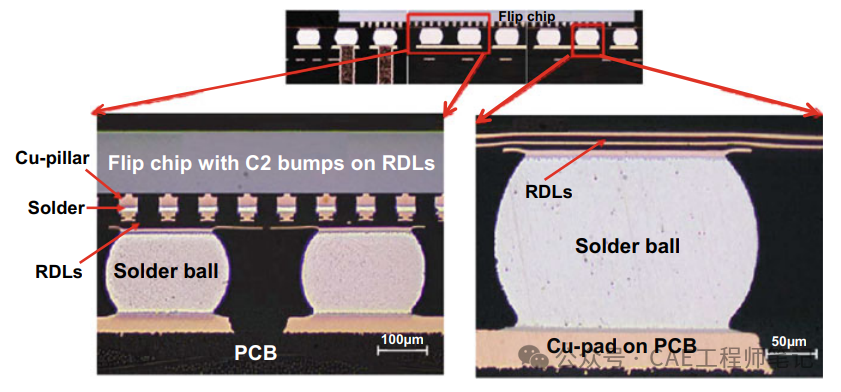

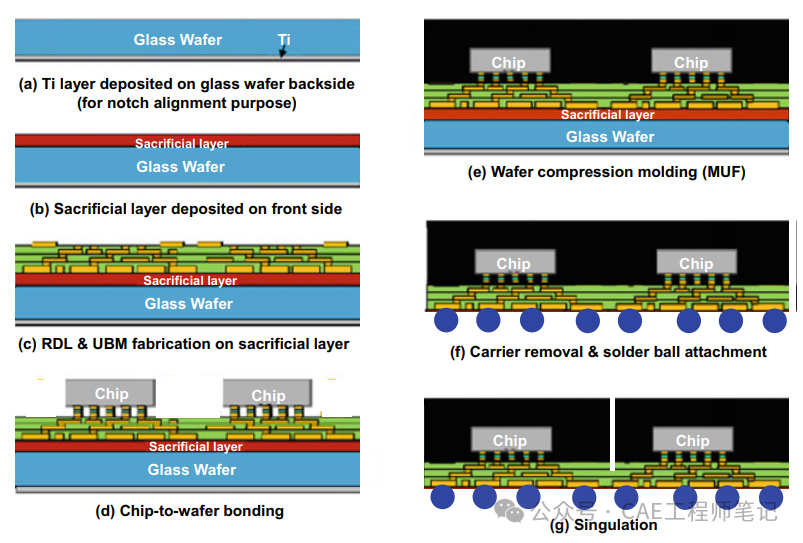

為了克服這些挑戰,Deca technologies 公司在 2012 年提出了芯片后裝或 RDL 先裝 (Chip-Last or RDL-First) 的技術方案,這項技術是帶有饋通轉接板的智能芯片互連技術(SMAFTI)的基礎。

Chip-Last or RDL-First

首先,在平坦的臨時載板上制作 RDL,可以消除前端工藝中翹曲帶來的影響;其次將 KGDs 以 I/O 面朝下的方式與 RDL 進行對準互連,完成芯片到晶圓(D2W)的鍵合工藝后;再使用 EMC 進行固化塑封處理,隨后將臨時載板去除;最后將焊球安裝在底部的 RDL 上并將重構晶圓切割成單獨的封裝。

相較于 Chip-First 的扇出型封裝技術,Chip-Last or RDL-First 技術中每一步工藝的難度都比較大,且這項技術需要更多的材料、設備、生產場地和技術人員,其生產成本非常高,并也有可能導致更大的產能損失。因此,該技術通常只應用于要求超高密度封裝和超高性能的產品中,如高端服務器和人工智能。

由于 Fan-out 封裝結構本身具有厚度更薄、密度更高等特征,也給FOPLP 帶來了諸多考驗。

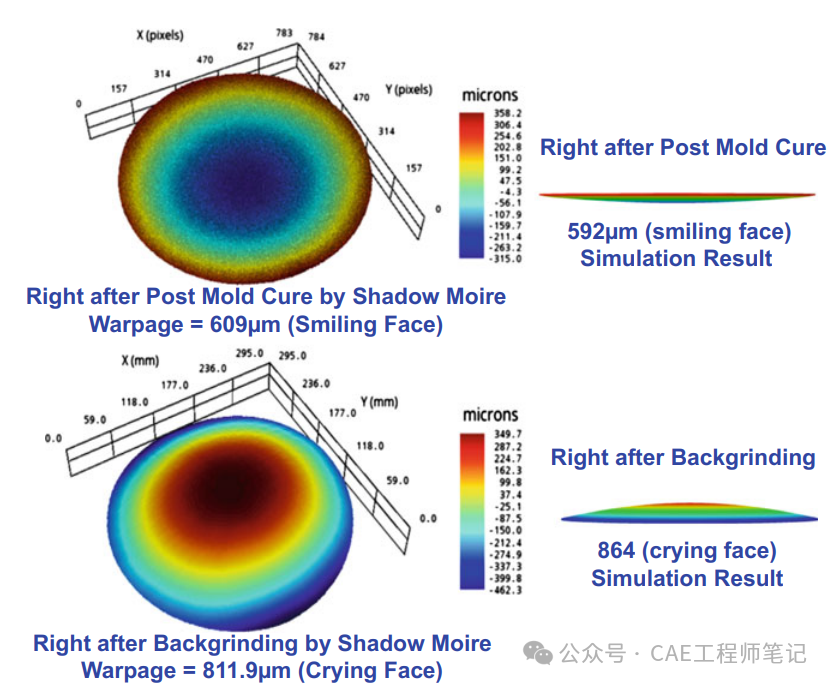

工藝翹曲:在制造工藝過程中的翹曲行為是扇出型封裝在普及過程中面臨的一個重大挑戰。由于不同材料的熱膨脹系數并不完全一致,在生產工藝中經歷升溫和降溫時,不同材料受熱膨脹和冷卻收縮的程度均不一樣,從而導致的熱失配應力是翹曲產生的主要原因。FOPLP 由于具有面積大而厚度小的特點,使得整個組件抵抗翹曲的能力較低,過大的工藝翹曲會嚴重影響封裝的生產良率以及無法進一步減小 RDL 的線寬和線距,因而是 FOPLP 封裝量產和工藝升級過程中的主要難點。在其他條件固定時,FOPLP 的面積越大,則翹曲幅度越大。所選用的封裝結構、塑封工藝、溫度載荷的不同,都可能對 FOPLP 的翹曲產生影響。

芯片偏移:在芯片拾取和放置過程中芯片定位精度的不足、在 EMC 壓縮成型過程中芯片受到液體流動帶來的拖動力和材料之間熱膨脹系數不匹配導致的熱失配應力均是造成芯片偏移的主要原因。輕微的芯片偏移會使后續光刻步驟中對準工藝產生明顯的偏差,對 RDL 的制造是一個巨大的挑戰。RDL 的線寬和線距以及器件焊盤之間的間距均會因芯片偏移而降低要求,導致封裝尺寸和產能損失也有所增大。

界面分層:工藝過程中使用了較多的聚合物,這些聚合物在常溫或常壓下易吸收空氣中的水分,在經過回流焊(220~260 °C)時,聚合物中的水分在高溫下會瞬間氣化,使聚合物內產生較大的蒸汽壓,同時受到熱失配應力的影響,重構晶圓內不同的粘接界面易發生裂紋萌生和分層現象。

芯片擠出:芯片擠出是指模塑料表面到芯片 I/O 面具有一定的臺階高度。在 RDL 制造中光刻工藝的精細間距和寬度的嚴格要求面臨著共面性問題,芯片突出問題將極大地影響 RDL 的斷裂,短路和開路故障。

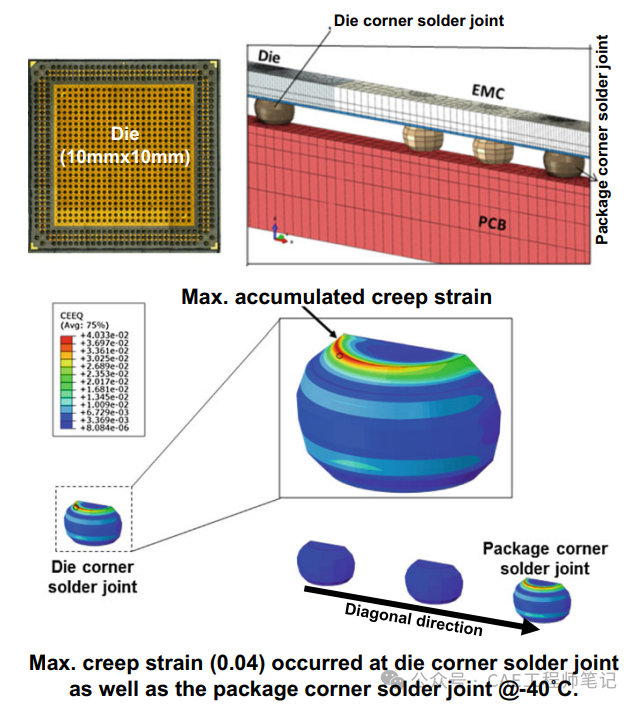

焊點疲勞失效:焊點的疲勞失效主要包括熱疲勞和力學疲勞,其中熱疲勞是導致焊點失效的主要因素,熱疲勞源于器件在服役過程中承受的熱循環載荷和功率載荷等。 宏觀上表現為熱疲勞損傷導致在遠離焊點中心區的釬料與基板過度區(即高壓力區)產生初始裂紋,裂紋逐漸沿釬料與基板界面擴展至整個焊點;微觀上表現為熱疲勞斷口表面有疲勞條紋的特征、晶界微孔洞和蠕變沿晶界斷裂的痕跡。焊點的疲勞壽命決定著整個器件的使用壽命,一個焊點的失效便可導致整個器件無法正常工作。

總的來說,從 2009 年 FOWLP 這一概念被提出以來,到現在隨著尺寸超過 600×600 mm 的 FOPLP 的不斷涌現。可以看出,要實現更高的制造效率,降低晶圓的浪費程度,同時維護好封裝成本,FOWLP 朝著 FOPLP 的轉變是必然的趨勢。

-

晶圓

+關注

關注

53文章

5151瀏覽量

129680 -

封裝

+關注

關注

128文章

8642瀏覽量

145330 -

先進封裝

+關注

關注

2文章

472瀏覽量

611

原文標題:先進封裝技術(Semiconductor Advanced Packaging) - 7 扇出型板級封裝(FOPLP)

文章出處:【微信號:深圳市賽姆烯金科技有限公司,微信公眾號:深圳市賽姆烯金科技有限公司】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

日月光斥資2億美元投建面板級扇出型封裝量產線

一種新型RDL PoP扇出晶圓級封裝工藝芯片到晶圓鍵合技術

芯片封裝中的FOPLP工藝介紹

華天科技硅基扇出封裝

整合為王,先進封裝「面板化」!臺積電、日月光、群創搶攻FOPLP,如何重塑封裝新格局?

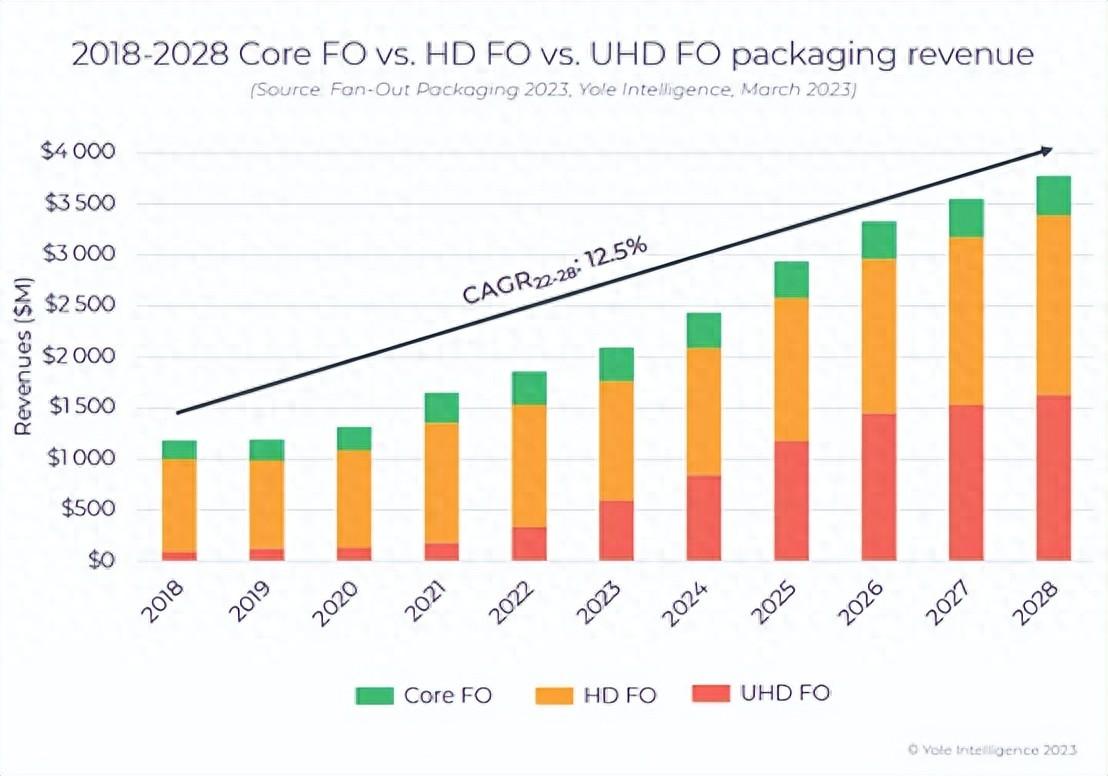

扇出型 (Fan-Out)封裝市場規模到2028 年將達到38 億美元

先進封裝技術-7扇出型板級封裝(FOPLP)

先進封裝技術-7扇出型板級封裝(FOPLP)

評論