先進封裝技術(Semiconductor Advanced Packaging) - 1 混合鍵合技術(上)

先進封裝技術(Semiconductor Advanced Packaging) - 2 混合鍵合技術(下)

先進封裝技術(Semiconductor Advanced Packaging) - 3 Chiplet 異構集成(上)

先進封裝技術(Semiconductor Advanced Packaging) - 4 Chiplet 異構集成(下)

先進封裝技術(Semiconductor Advanced Packaging) - 5 TSV 異構集成與等效熱仿真

隨著電子信息技術的快速發展,半導體電子行業及其基礎制造技術已成為過去半個世紀最重要的發展之一,集成電路芯片已經改變了經濟、技術和社會活動中的各個領域。在過去的幾十年里,摩爾定律(Moore’s law)一直是驅動半導體行業迅速發展的方向指南,摩爾定律起源于對集成電路技術早期經濟和技術趨勢的觀察和預測,是根據現象推測出來的經驗性規律。

隨著半導體技術的不斷發展,半導體的工藝制程已經逐漸接近物理極限,摩爾定律即將走到盡頭,整個芯片產業都將進入后摩爾(More than Moore)時代。后摩爾的定義是不再單純地依靠減小晶體管的特征尺寸來堆疊更多數量的晶體管從而實現芯片性能的提升,而是更多地通過電路設計及系統算法的優化,同時借助先進封裝技術來實現異構集成(Heterogenous integration),即依靠先進封裝技術把不同模塊和不同功能的芯片集成到一起以提升整體封裝的性能。

近半個世紀以來,封裝行業得到了飛速的發展。實現封裝產品的輕薄短,不僅僅是引腳間距的縮小,更是從封裝形式、封裝工藝等多個角度進行了改進。從最早的框架級封裝,通過對金屬板進行蝕刻,并利用蝕刻框架上的蝕刻圖形作為引腳,切割后可形成封裝產品。為了形成復雜的多引腳封裝,出現了利用銅箔壓合技術制備的基板,在基板上做好線路,基板正面安裝芯片,背面可通過植球等方式輸出。現在流行的晶圓級封裝,通過在晶圓上先進行芯片封裝,并在切割后對單顆芯片背面做球或柱子等輸出端。晶圓級封裝具備最優的性價比,也是未來封裝發展的必然趨勢。

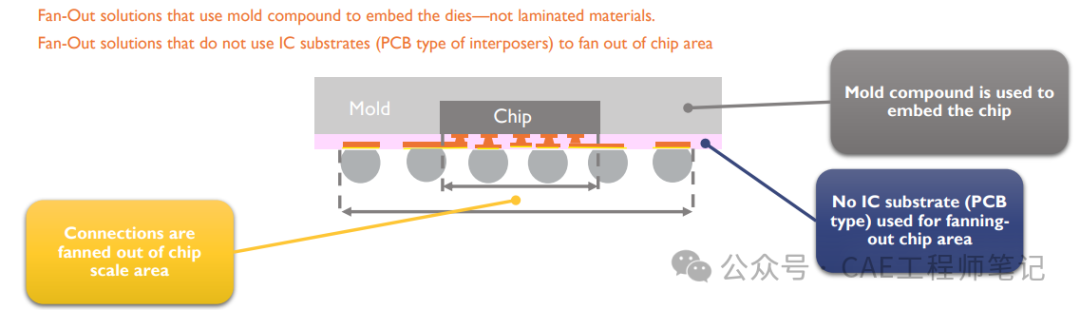

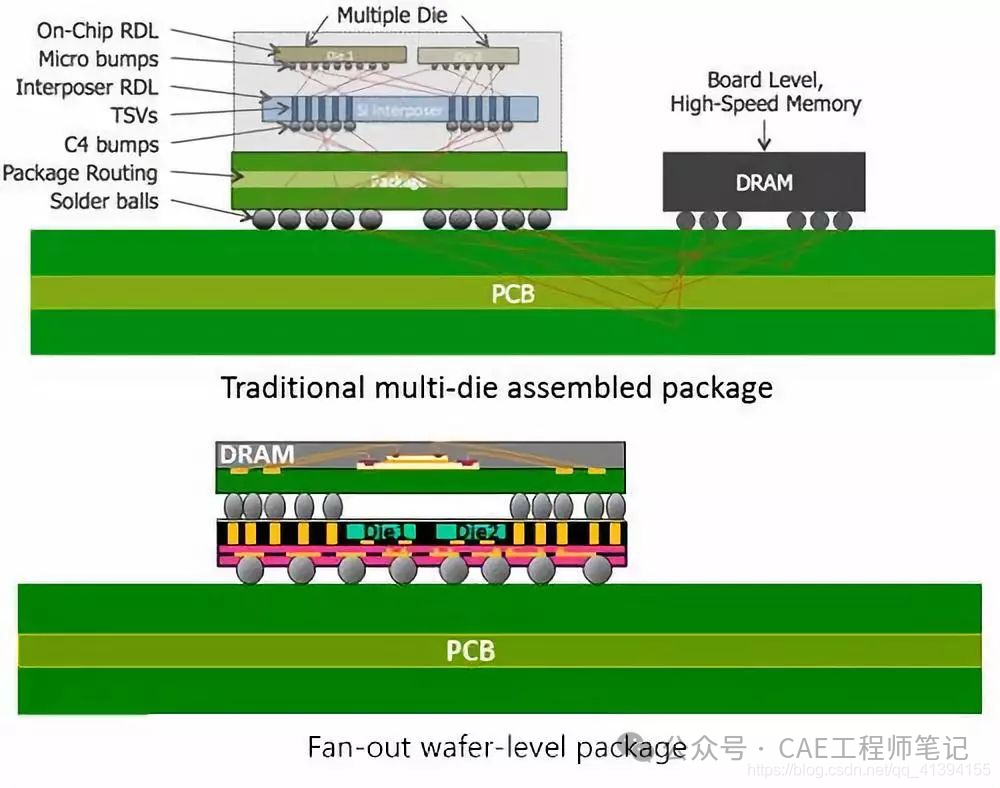

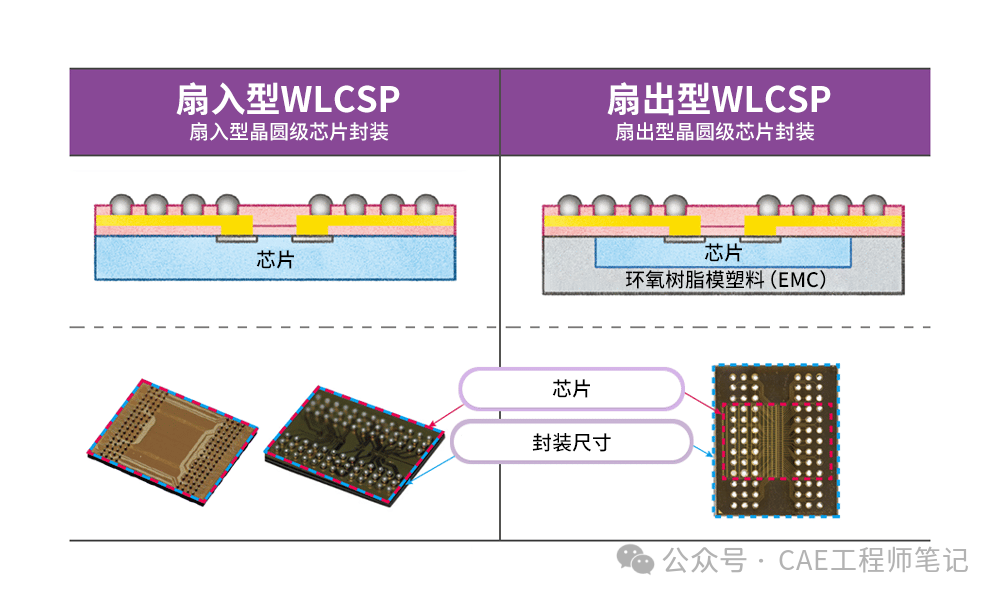

傳統封裝的發展使得芯片面積與封裝面積的比值越來越接近于 1,封裝面積決定了封裝能力,然而不管是布線或是引腳在增加了數量后間距都越來越小,到達極限后則需要更大的空間增加數量,為了獲得更大的空間則必須使該比例接近 1 甚至遠小于 1,所以出現了扇出(fan-out)的概念。當芯片面積和封裝面積接近極限之后,需要通過新的封裝方式來超越這個極限,這時候封裝朝著兩個方向發展:

第一種是 3D 集成封裝,在有限的封裝區域中借助 TSV 技術在垂直方向上進行芯片的堆疊;

第二種是扇出型封裝,通過晶圓重構技術增大封裝面積以集成不同功能的芯片。

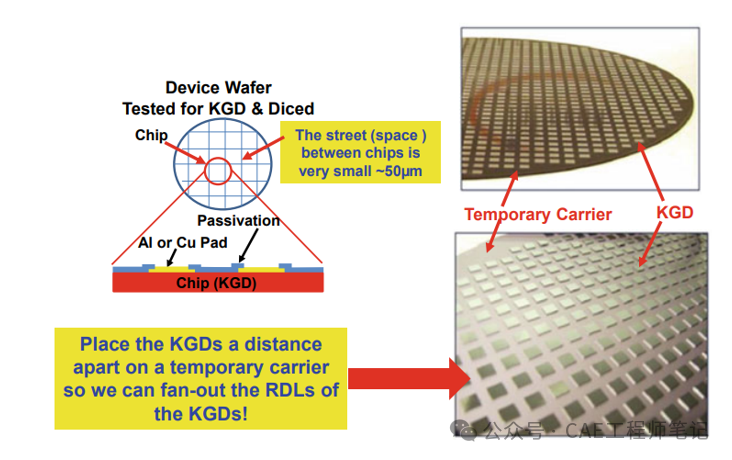

扇出型封裝是指將所需芯片嵌入在 EMC 中,通過 RDL 對焊點進行再分配,最后裝配到 PCB 所形成的封裝。相比于扇入型封裝,扇出型封裝將每一顆已知良好的芯片(KGD)嵌入在 EMC 中時,每顆 KGD 之間的空隙可以提供額外的 I/O 互連點,從而使 I/O 端子數量不受芯片尺寸大小的限制,很好地填補了既要求小芯片尺寸又要求高引腳數量這一類封裝的空白。此外,扇出型封裝通過再布線層技術進行互連并取代基板,縮短互連長度,降低信號延遲,減小生產成本。

尤其需要指出的是,與臺式機或筆記本電腦不同,如今的移動計算設備對功率非常敏感,同時對多功能、高性能和高帶寬的要求也不斷提高,單靠晶體管縮放和芯片縮放已不能滿足移動設備對多功能集成的苛刻要求,如更小的外形尺寸,良好的功率效率、散熱和電性能等。移動計算設備中功能集成的復雜性使得傳統的引線鍵合、C4 焊點倒裝芯片封裝、多芯片模組和系統級封裝等難以實現高引腳數和高密度的集成,而扇出型晶圓級封裝(FOWLP)技術允許將芯片的 I/O 互連點布置在芯片面積區域以外的空隙中,以滿足更多的 I/O 端子數、更小的外形尺寸和更高的電氣性能。同時,該技術也能緩解互連焊點兩側 I/O 間距不匹配的問題。

2006 年,英飛凌最先開發和應用了扇出型封裝技術,并在手機基帶芯片封裝中實現量產。由于扇出型封裝第一步要重構晶圓,然后用塑封料將芯片包裹起來并完成再布線和凸點制作,從結構上看芯片像是被嵌入到塑封料中,因此英飛凌將此項技術稱為嵌入式晶圓級球柵陣列(eWLB)。幾乎在同一時期,飛思卡爾也提出了重分配芯片的封裝(RCP)技術用來實現雷達和物聯網模塊的封裝量產。

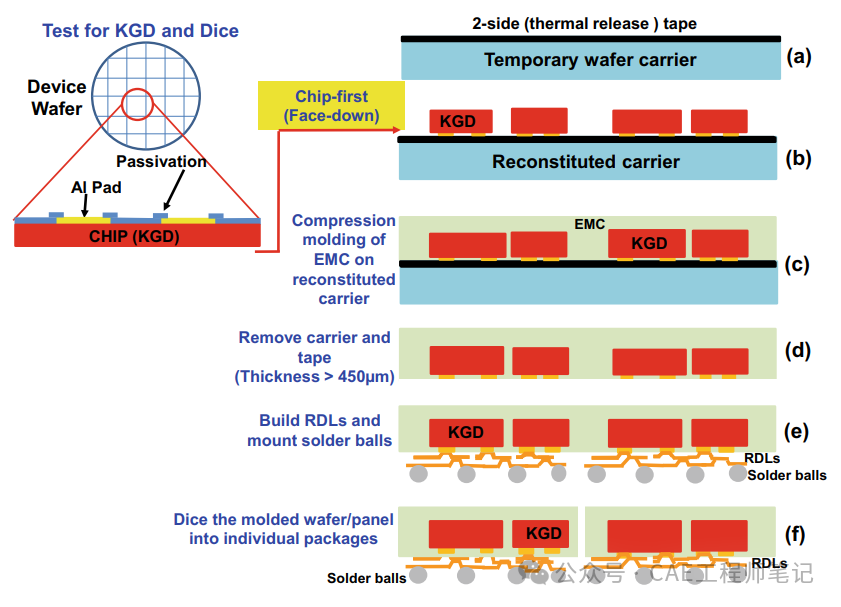

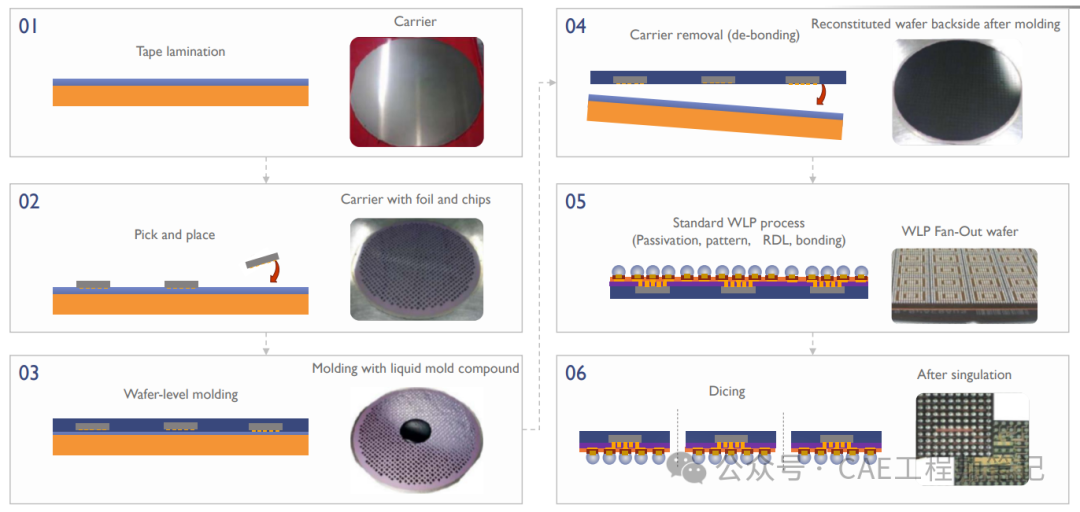

兩者都是先裝芯片且芯片功能面朝下的封裝方式。將芯片倒裝在貼有雙面膠膜的金屬載板上,整體進行塑封后,將載板和膠膜分別進行剝離,翻轉剩余的芯片結構朝上進行再布線并植球、切割。

無論是英飛凌的 eWLB 封裝技術還是飛思卡爾的 RCP 封裝技術,最初并沒有引起大家的重視,應用范圍也比較狹窄,僅僅用來批量生產手機基帶芯片和雷達模塊,并且芯片 I/O 數量一般小于 500,再布線的線寬線間距也相對較大。早先提出的 FOWLP 技術在封裝性能、 互連布線和異構集成等方面都存在不足,僅用于相對簡單的 2D 封裝。

隨著先進封裝材料和設備的發展,尤其是高解析度、高光敏度光刻膠和高分辨率光刻機在先進封裝技術中的應用,晶圓級芯片尺寸封裝(WLCSP)得到快速發展。在 2012-2014 年,扇出型晶圓級封裝面臨來自晶圓級封裝技術的激烈競爭,英特爾移動產品也放棄了該項技術在其手機基帶芯片封裝中的應用,由此扇出型封裝進入發展瓶頸期。

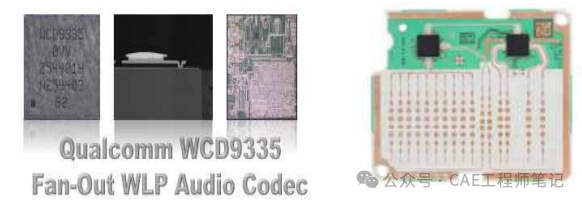

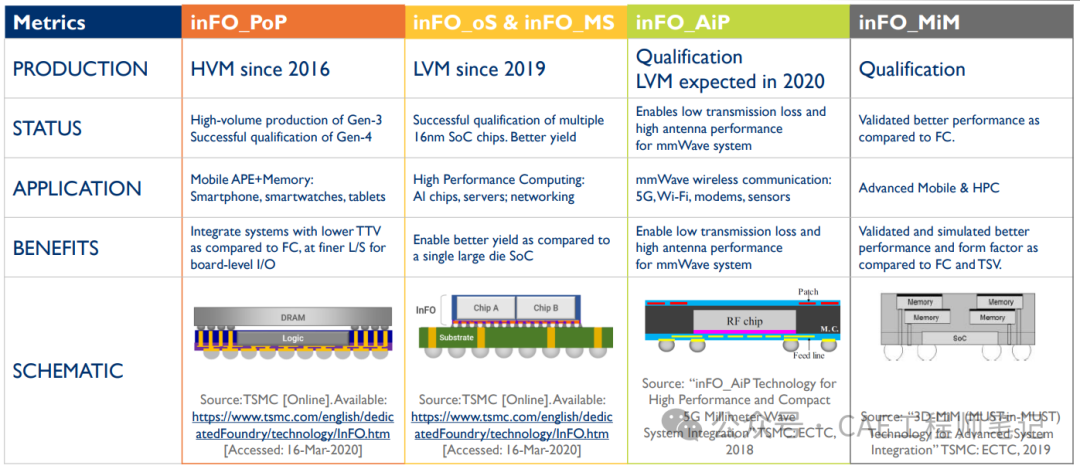

2016 年,TSMC 在先進封裝技術上經過數十年的布局和沉淀,在 FOWLP 領域中研發出的集成扇出型(InFO)封裝脫穎而出,并成功應用于蘋果公司 iPhone 7 系列手機的 A10 應用處理器(AP)中。得益于該項技術,臺積電成功包攬了蘋果公司之后每一代手機的 AP 芯片的制造和封裝訂單。

集成扇出型封裝技術的優勢在于可省去載板,綜合成本較傳統的疊層封裝(PoP)降低約 2~3 成以上,節省芯片封裝的成本,并可應用于手機 AP 或其他 RF、電源管理 IC 等應用市場。蘋果和臺積電強強聯手將發展多年的扇出型封裝技術帶入量產,其示范作用不可小覷,至此各大芯片制造及封裝代工廠開始紛紛投入巨資布局扇出型封裝。

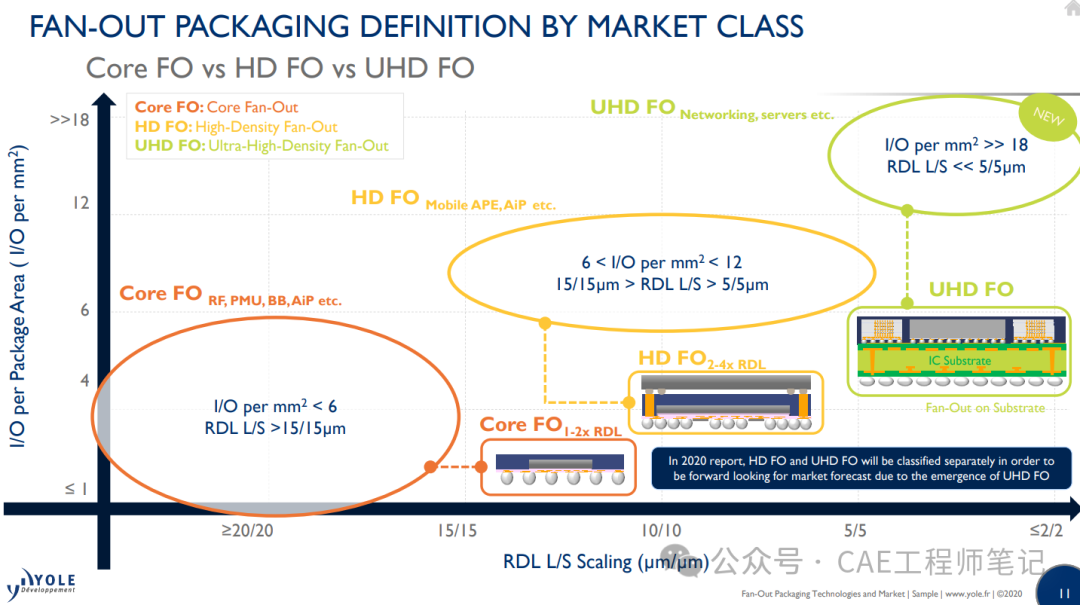

隨著扇出型封裝技術逐漸成熟,其 I/O 端子數從原來的每平方毫米少于 6 個發展至如今的每平方毫米遠多于 18 個,而 RDL 的線寬和線距從原來的大于 15 微米發展至如今的小于 5 微米。扇出型封裝技術也從簡單地通過增大扇出區域來增加布線面積,升級為具有模通孔(TMV)的 3D 封裝技術,甚至是具有超高密度的異構集成封裝。

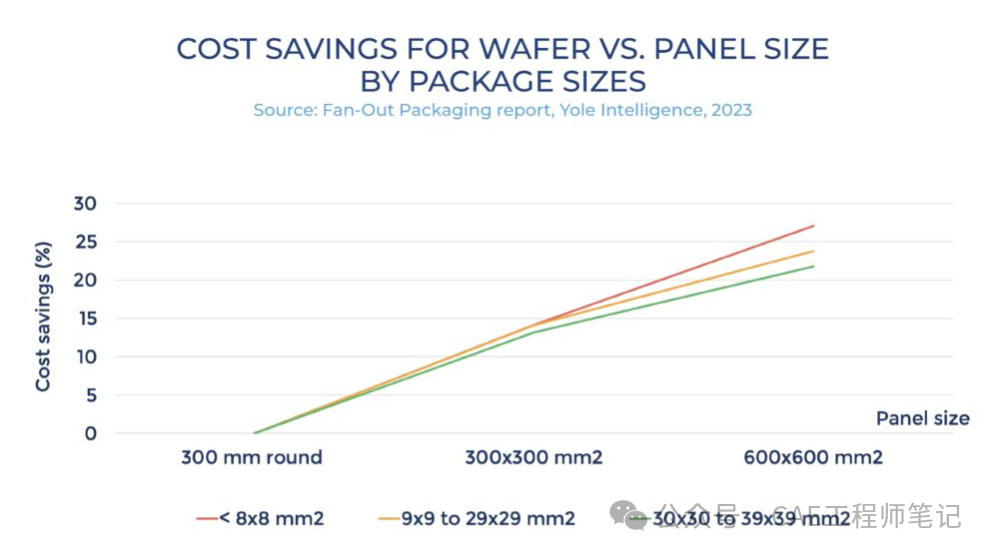

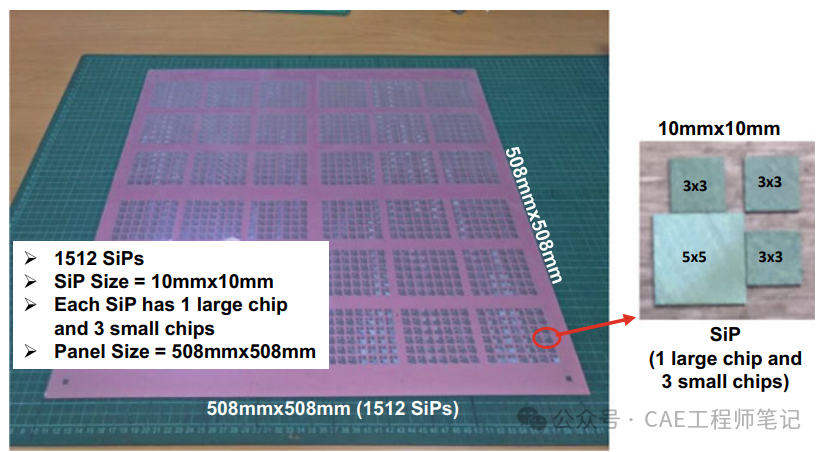

目前,FOWLP 主要是使用 12 英寸的晶圓載板來進行生產制造,為了進一步降低扇出型封裝的生產成本,如何提高其生產效率成為了下一個比較關注的問題。對于其技術路線的升級有兩種可選方案,第一種是采用更大尺寸的晶圓載板進行生產,第二種是使用扇出型面板級封裝(FOPLP)技術,但使用更大尺寸的晶圓載板所帶來的設備更新成本及工藝難度均遠比 FOPLP 技術大。相較于 FOWLP 技術,FOPLP 具有更高產能和更低成本的潛力,FOPLP 也成為了更具潛力的發展方向。

FOPLP 的封裝工藝與 FOWLP 相似,兩者最大的不同點是 FOWLP 使用晶圓狀的臨時載板,而 FOPLP 使用矩形載板。FOPLP 技術中使用的矩形載板相對于 12 英寸的晶圓載板不僅具有更大的面積,且其載板利用率也遠高于晶圓載板。

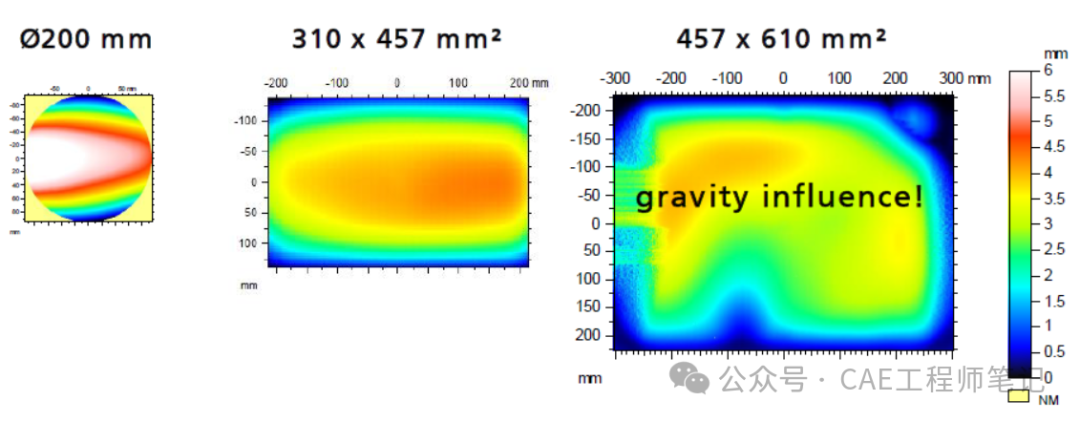

但由于載板面積變大,相較于 FOWLP 而言,FOPLP 在生產制造過程中的翹曲問題也變得尤為嚴重,對其工藝精度造成很大的影響,增大了其生產難度。因此,FOPLP 更多的是運用在 I/O 密度較低及 RDL 線寬和線距相對較大的中低端產品中,而 FOWLP 更多的是運用在 I/O 密度較高且 RDL 線寬和線距較小的高端應用中。

從扇出型封裝在手機基帶芯片封裝中的首次應用到現在已經過去十多年的時間,中間經歷過低迷期。但是得益于芯片制程能力的不斷提高、高精度半導體設備和材料在先進封裝中的應用以及消費類電子產品對微型化、智能化和高度集成化的強烈需求,各大設備、材料和代工廠積極布局并投入重金研發,迅速推動了扇出型封裝的應用和發展。盡管目前扇出型封裝還存在一些技術難題,但是隨著摩爾定律逐漸走到盡頭,作為先進系統級封裝的重要解決方案,扇出型封裝大規模爆發指日可待。

-

晶圓

+關注

關注

52文章

5134瀏覽量

129347 -

先進封裝

+關注

關注

2文章

466瀏覽量

559

原文標題:先進封裝技術(Semiconductor Advanced Packaging) - 6 扇出型晶圓級封裝(FOWLP)

文章出處:【微信號:深圳市賽姆烯金科技有限公司,微信公眾號:深圳市賽姆烯金科技有限公司】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

先進封裝技術- 6扇出型晶圓級封裝(FOWLP)

先進封裝技術- 6扇出型晶圓級封裝(FOWLP)

評論