Intel之前已經(jīng)宣布在2021年推出7nm工藝,首發(fā)產(chǎn)品是數(shù)據(jù)中心使用的Ponte Vecchio加速卡。7nm之后的5nm工藝更加重要了,因為Intel在這個節(jié)點會放棄FinFET晶體管轉(zhuǎn)向GAA晶體管。

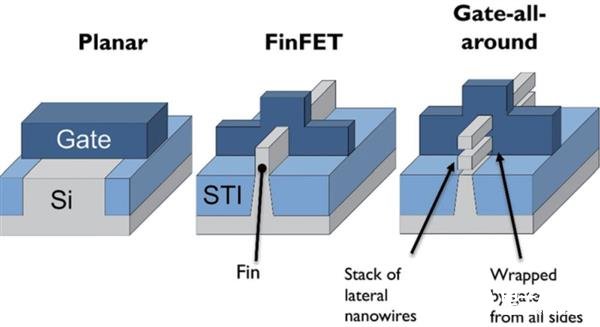

隨著制程工藝的升級,晶體管的制作也面臨著困難,Intel最早在22nm節(jié)點上首發(fā)了FinFET工藝,當(dāng)時叫做3D晶體管,就是將原本平面的晶體管變成立體的FinFET晶體管,提高了性能,降低了功耗。

FinFET晶體管隨后也成為全球主要晶圓廠的選擇,一直用到現(xiàn)在的7nm及5nm工藝。

Intel之前已經(jīng)提到5nm工藝正在研發(fā)中,但沒有公布詳情,最新爆料稱他們的5nm工藝會放棄FinFET晶體管,轉(zhuǎn)向GAA環(huán)繞柵極晶體管。

GAA晶體管也有多種技術(shù)路線,之前三星提到他們的GAA工藝能夠提升35%的性能、降低50%的功耗和45%的芯片面積,不過這是跟他們的7nm工藝相比的,而且是初期數(shù)據(jù)。

考慮到Intel在工藝技術(shù)上的實力,他們的GAA工藝性能提升應(yīng)該會更明顯。

如果能在5nm節(jié)點跟進GAA工藝,Intel官方承諾的“5nm工藝重新奪回領(lǐng)導(dǎo)地位”就不難理解了,因為GAA工藝上他們也是比較早跟進的。

至于5nm工藝的問世時間,目前還沒明確的時間表,但Intel之前提到7nm之后工藝周期會回歸以往的2年升級的節(jié)奏,那就是說最快2023年就能見到Intel的5nm工藝。

責(zé)任編輯:wv

-

intel

+關(guān)注

關(guān)注

19文章

3493瀏覽量

188070 -

晶體管

+關(guān)注

關(guān)注

77文章

9989瀏覽量

140833 -

FinFET

+關(guān)注

關(guān)注

12文章

256瀏覽量

90975

發(fā)布評論請先 登錄

FinFET與GAA結(jié)構(gòu)的差異及其影響

互補場效應(yīng)晶體管的結(jié)構(gòu)和作用

IBM與Rapidus在多閾值電壓GAA晶體管技術(shù)的新突破

如何測試晶體管的性能 常見晶體管品牌及其優(yōu)勢比較

晶體管與場效應(yīng)管的區(qū)別 晶體管的封裝類型及其特點

晶體管的輸出特性是什么

CMOS晶體管的尺寸規(guī)則

NMOS晶體管和PMOS晶體管的區(qū)別

CMOS晶體管和MOSFET晶體管的區(qū)別

什么是單極型晶體管?它有哪些優(yōu)勢?

GaN晶體管和SiC晶體管有什么不同

GaN晶體管的基本結(jié)構(gòu)和性能優(yōu)勢

芯片晶體管的深度和寬度有關(guān)系嗎

PNP晶體管符號和結(jié)構(gòu) 晶體管測試儀電路圖

Intel放棄FinFET晶體管轉(zhuǎn)向GAA晶體管 GAA工藝性能提升或更明顯

Intel放棄FinFET晶體管轉(zhuǎn)向GAA晶體管 GAA工藝性能提升或更明顯

評論