DDR5 JEDEC最近已定稿,從各類介紹文章看基本集中在一些新特性描述方面,極少涉及到技術細節,與海報效果差不多。為了深入了解DDR5的各方面信息,“翻墻”、“找網友”、“找前同事”各種方法都用了,最后發現還是找不到最完美的JEDEC文件,很多參數在【TBD】的狀態,經過對這些零碎材料的分析并結合自身的經驗,給出在仿真DDR5新特性時采取何種策略或提出相應建議。 會發現,前面掌握的DDRx基礎知識及方法大部分可以承傳到DDR5仿真設計中,當然要把包含DDR5信號的產品設計好,還需要花更多的時間深入學習并根據實際的情況處理。

如下從幾方面對DDR5進行闡述:

1 DDR5顆粒容量

DDR5單Die可以做到最大容量為64Gbit,單DIMM條容量達到2T。這個數據對于平時需要使用大內存仿真或平面設計的同學絕對是個好消息。

圖 1. Dimm與Die的容量

2 DDR5封裝

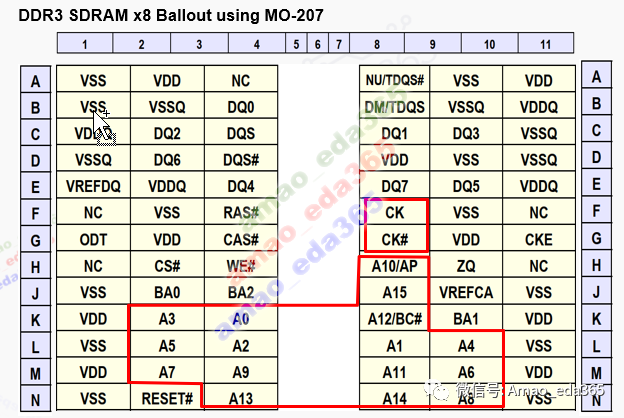

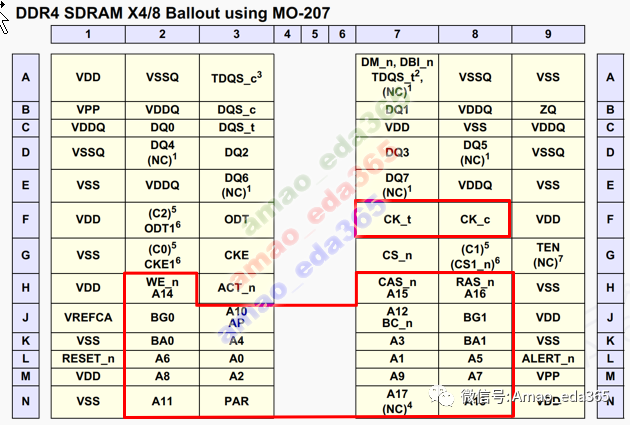

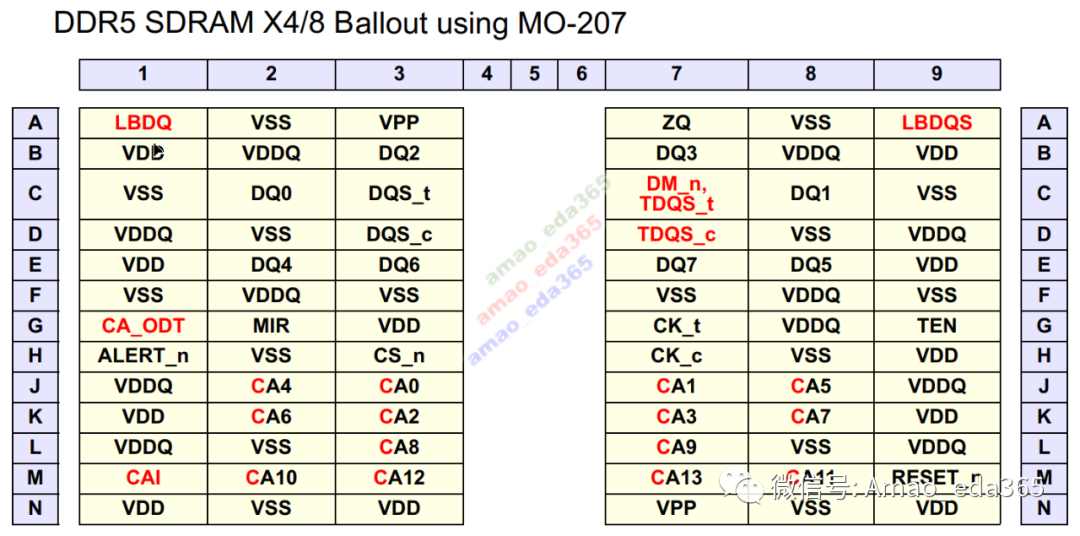

DDR3-5的封裝比較

圖 2. DDR3 PINMAP

圖 3. DDR4 PINMAP

圖 4. DDR5 PINMAP

從DDR3-DDR5 地址、控制、命令數據、時鐘、電源的管腳總體擺放位置只作了小調整,而這個小調整按流程需要在DIE-PKG-PCB間進行Co-Design,以保證信號SI與電源的噪聲,這是協同設計的過程。

一般工程師是在PINMAP固定的條件下進行板級的布線設計及仿真,較少有機會深入到芯片Padorder層面進行整體考慮,這與國內芯片生態及平臺目前的狀態有極大的關系。

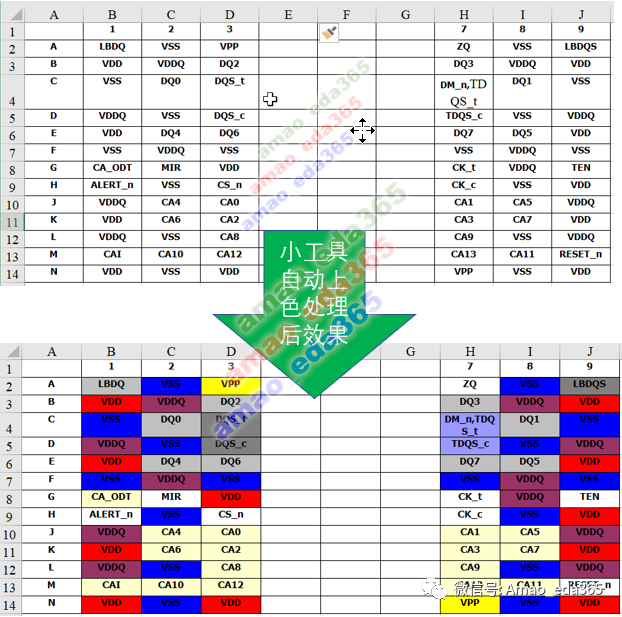

Pinmap設計時一般會給不同種類的信號總線賦上不同的顏色以提高工作效率及便于Reviewed。作者開發了相應自動上色小工具處理,高效快速,這里不作深入,有需要的讀者可以到作者的公眾號上自行下載。

如:小工具對DDDR5 PINMAP自動分類上色的效果圖

經過上色后,DQ/ADDRESS/VDD等不同信號的分布狀況一目了然,非常方便信號的檢查。

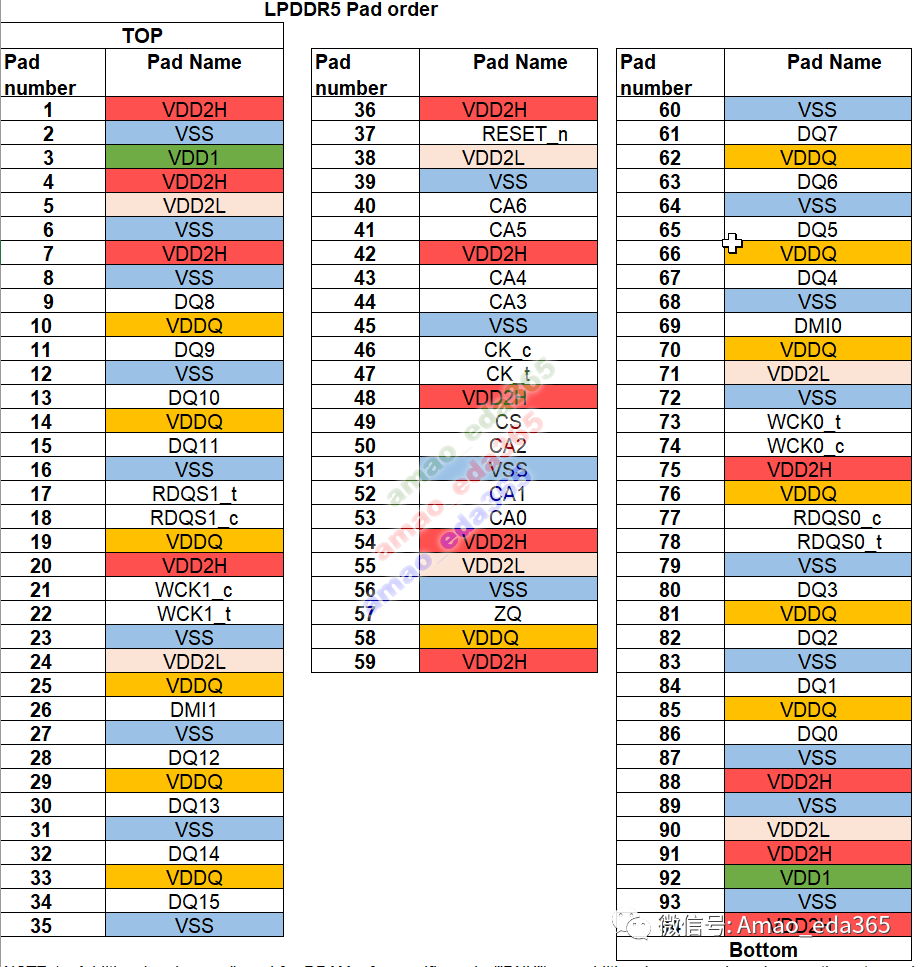

3 LPDDR5芯片管腳的擺放設計

芯片Padorder一般需如何擺放?可以參考下面LPDDR5顆粒的樣例,從下圖中的芯片管腳擺放可以看到,對于數據信號及時鐘等速率較高的情況,要求每個pad必須要與電源/地相鄰,在設計時怎樣使整個芯片的PAD使用數量最少,則與設計者的水平有很大的關系。

圖 5. LPDDR5芯片PADORDER

4 Dimm條分析

Dimm結構的改變應是本次從外觀外看改動最大的地方,每個DIMM提供兩個獨立的32位數據通道(考慮ECC時為40位),兩個7位CA總線,而不是DDR4單個24位CA總線,每個通道的變化及與DDR4的對比如下:

具體管腳的調整及擺放需要對DIMM條建模仿真以確定(下月我公開課中會對具體的建模過程及仿真的效果比較有詳細的講解)

圖 6. DDR5 DMIMM

圖 7. DDR4 DIMM

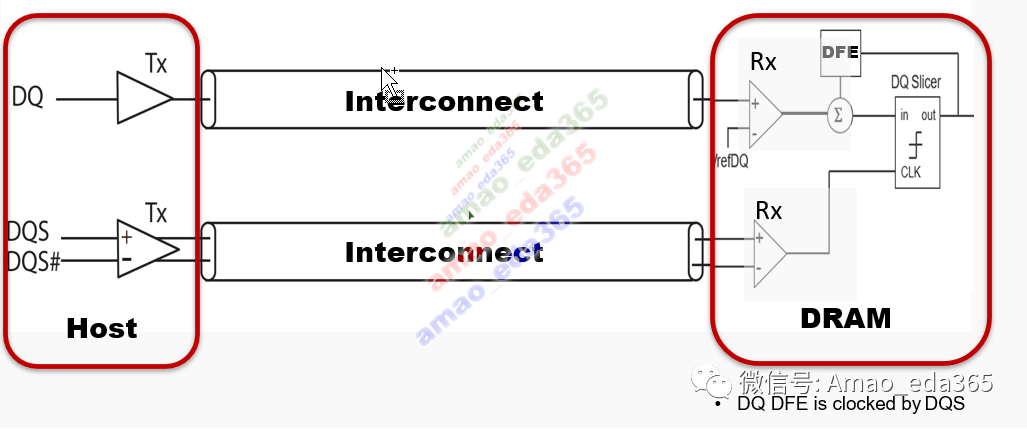

5 DEF

DFE(Decision Feedback Equalization:決策反饋均衡)的引入是DDR5的另一個亮點,DFE是一種通過使用來自內存總線接收器的反饋來提供更好的均衡效果及排除 inter-symbol 干擾的方法。均衡可以使DDR 5內存總線傳輸速率更高。還添加了新的改良訓練模式,以幫助DIMM和控制器補償內存總線上的微小時序差異 。

DFE的引入使仿真變得更簡單,優化通過軟件工具自動完成,很多復雜的設置體現在底層軟件上,而應用層面則是越來越簡單了。如下圖的數據接收端引入的均衡示圖。

圖 8. DDR5 DQ DFE均衡

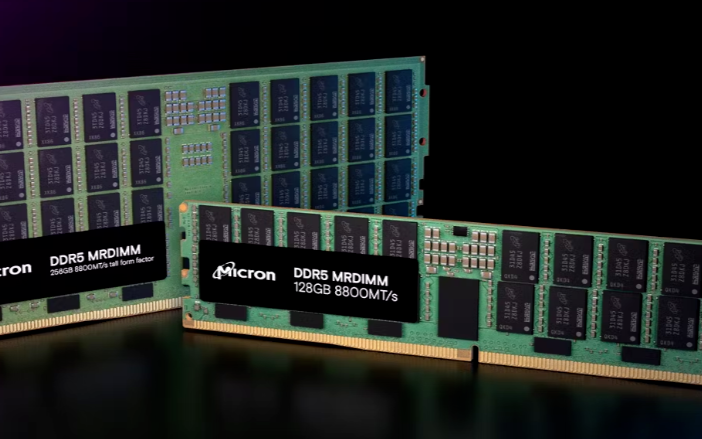

6 電壓調節器上Dimm

由于工作電壓降低,對紋波影響要求更嚴格,電壓調節原來在主板上,這樣的路徑較長,中間還會經Dimm插座,對電源的影響較大,而現的Dimm條設計則是把電壓調節器移到DIMM條上,如下圖。

圖9. DDR5電壓調節器移到Dimm條上

DIMM上的電源PDN設計與仿真方法可以參考《信號、電源完整性仿真設計與高速產品應用實例》中PowerAC與PowerDC仿真等章節內容,這些方法對于DDR5的應用環境完全可以勝任。Dimm條仿真PowerDC/AC的效果如下圖。

圖 10. DIMM上IR DROP仿真效果

結論

DDR5的出現,沒有太多的驚喜,也沒有太多的失望,從仿真的角度看,DDR4/3的仿真技能及思路大部分都可以繼承,在實際DDR5仿真過程中需要具體問題具體分析了。

-

pcb

+關注

關注

4365文章

23481瀏覽量

409232 -

封裝

+關注

關注

128文章

8651瀏覽量

145362 -

DDR5

+關注

關注

1文章

444瀏覽量

24869

原文標題:DDR5分析與仿真應對策略

文章出處:【微信號:eda365wx,微信公眾號:EDA365電子論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

漲價!部分DDR4與DDR5價差已達一倍!

上海貝嶺推出全新DDR5 SPD芯片BL5118

DDR4漲價20%,DDR5上調5%!

大型文件秒開、多開任務流暢——DDR5的優勢遠不止頻率

DDR3、DDR4、DDR5的性能對比

DDR5內存的工作原理詳解 DDR5和DDR4的主要區別

揭秘DDR5的讀寫分離技術奧秘

DRAM大廠第三季DDR5價格大幅上調

DDR5內存面臨漲價潮,存儲巨頭轉向HBM生產

SK海力士DDR5芯片價格或將大幅上漲

Introspect DDR5/LPDDR5總線協議分析儀

DDR5 MRDIMM內存標準將發,存儲廠商方案先行

DDR5內存條上的時鐘走線

從幾方面對DDR5進行闡述

從幾方面對DDR5進行闡述

評論