一、同步設計

1.1 時鐘的同步設計

關注問題:

(1)設計中盡可能使用單時鐘和單時鐘邊沿觸發

(2)不要使用例如“與”“或”門這些基本單元來生成RS鎖存或者FF

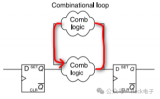

(3)不要在組合邏輯中引入反饋電路

在HDL設計中使用同步設計思想以及邏輯綜合工具。使用異步時鐘會讓更加精確的時序約束變得困難,因此,盡可能利用單個時鐘和單邊沿。(使用單個時鐘在多數設計中很難實現,在設計中盡量減少時鐘數量以減輕分析的復雜度)

盡管可以使用基本門來實現RS或FF,但時序分析工具會把它視作對組合電路的反饋,如果無法避免,則需要使用set_disable_timing設置來避免時序分析期間反饋環路的影響。

避免在內部電路生成異步時鐘,如果需要生成這樣的時鐘,那么推薦在生成時鐘的FF輸出端使用create_clock來指定時鐘。

避免反饋跨越異步復位,同樣的,避免使用門控時鐘和門控復位。

二、 復位問題

2.1 使用異步復位作為初始的復位

關注問題:

(1)使用同步復位電路可能會導致綜合器生成無法正確復位的電路,同時,同步復位會在數據路徑引入復位信號(延遲讓時序變得困難),在多時鐘系統中可能需要計數器來保證復位信號寬度。但同步復位并不是完全沒有優點,比如,保證系統是完全同步的,可以濾除掉復位信號的一些小毛刺,同步復位需要更少的觸發器等等,這些問題整理詳細文章討論。

(2)使用異步復位對寄存器進行初始的復位會更加安全

(3)除了復位功能外,復位/置位的引腳不要用作它途

(4)在同一個復位線路上禁止同時使用同步復位和異步復位

(5)一個FF盡量不使用異步復位和異步置位

異步復位示例:

always結構僅會由時鐘上升沿以及低有效的復位信號觸發

always @(posedge CLK or negedge RST_X) if (!RST_X) Q 《= 1‘b0; else Q 《= DATA;

請注意上面表述的是初始復位(Initial reset)推薦使用異步復位。異步復位的時序分析比較困難,因為時序路徑會被切斷,從而沒有考慮到B的復位輸入到寄存器B的輸出Q的時序。同時,A的輸出到B異步復位的的時序也不會被分析。

2.2 復位問題

注意問題:

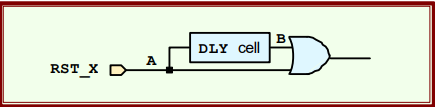

(1)不要在復位路徑引入邏輯電路

例:

reg[4:0] count; wire REN_X,EN_X,count32_x,ctl_x; assign count32_x = ~(& count) | ctl_x; assign REN_X = EN_X | count32_x; always @( posedge CLK or negedge REN_X ) if(REN_X == 1’b0) Q 《= 1‘b0; else Q 《= D;

當組合邏輯產生復位信號時,由于優化的原因,使能信號可能會和FF分離,并且不排除危險信號驅動復位信號的可能性(FF可能會以意外的時序復位)。如上圖所示,即使在RTL描述中的FF復位信號前插入了使能邏輯,也可能會發生這種情況。并且一旦發生這種問題,很難排查。總而言之,設計電路不要總依賴綜合工具的優化。

2.2.1 噪聲,毛刺

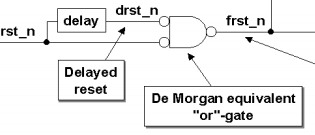

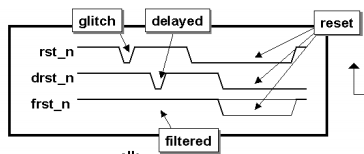

復位信號不排除會被噪聲干擾,產生一些毛刺,因此,推薦使用濾波,但引入濾波也不是必須的,視情況而定。下圖是高有效復位的濾波電路

如果是低有效復位?

濾波波形原理:

2.2.2 亞穩態問題

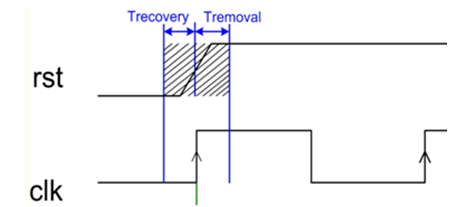

以低有效異步復位為例,如果復位信號在時鐘沿釋放(或附近),不滿足Recovery Time以及Removal Time,會出現亞穩態,所謂復位恢復時間就是,復位釋放的時間距離時鐘沿(上升沿)的時間,復位移除時間就是,復位釋放的時間距離時鐘沿(上升沿)的時間。和數據建立時間保持時間一樣,都要滿足一定的時序要求。這是需要關注的問題。

2.2.3 同步器/異步復位同步釋放

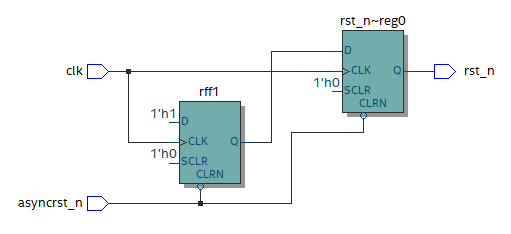

module async_resetFFstyle2 ( output reg rst_n, input clk, asyncrst_n); reg rff1; always @(posedge clk or negedge asyncrst_n) if (!asyncrst_n) {rst_n,rff1} 《= 2’b0; else {rst_n,rff1} 《= {rff1,1‘b1}; endmodule

外部的復位信號進入推薦使用異步復位同步釋放,下面是代碼綜合出的電路圖,這種設計有它的優勢。

編輯:jq

-

RS

+關注

關注

3文章

140瀏覽量

110623 -

代碼

+關注

關注

30文章

4900瀏覽量

70680 -

同步器

+關注

關注

1文章

109瀏覽量

15174 -

綜合器

+關注

關注

0文章

12瀏覽量

6593

原文標題:RTL設計風格及Verilog編碼規范(一)

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

淺談Verilog和VHDL的區別

Verilog 與 ASIC 設計的關系 Verilog 代碼優化技巧

Verilog 測試平臺設計方法 Verilog FPGA開發指南

Verilog與VHDL的比較 Verilog HDL編程技巧

ADS1281 PCM編碼規范應該在哪里找?

Verilog硬件描述語言參考手冊

如何利用Verilog-A開發器件模型

淺談RTL設計風格及Verilog編碼規范

淺談RTL設計風格及Verilog編碼規范

評論