當今 FPGA 和高性能處理器的多個電源軌必須按照嚴格的順序上電和斷電。通常連接到電源軌的去耦電容必須主動放電,以確保正確控制斷電順序并在可接受的時間內完成斷電。本文介紹了有源放電電路的原理和設計,并解釋了功率 MOSFET 等關鍵元件的選擇標準,以確保可重復的性能和可靠性。

介紹

當今的許多片上系統 FPGA、ASIC 和應用處理器都需要多個單獨的電源軌來為低壓核心邏輯、3.3V 或 5V I/O 以及諸如內存總線或 1.2V 以太網驅動器等其他電路供電。眾所周知,以正確的順序為這些電源軌上電對于確保正確的系統運行至關重要。電源定序器用于依次啟用每個負載點 (POL) 轉換器,在正確的時間啟動各個電源軌。確保斷電過程遵循相反的順序同樣重要,但電源線上的去耦電容會阻止系統正確斷電。除非這些電容器被主動放電,否則剩余的電荷會在 POL 被禁用后以不確定的速率衰減,因此可能會破壞序列。

有源電容放電

每個去耦電容器的放電時間可以使用串聯電阻來設置 RC 時間常數來控制。這使定序器能夠在序列中前一個轉換器停用后的已知時間延遲后關閉每個 POL。應選擇電阻值以在合適的時間內將電容器放電至其完全充電電壓的 5%,避免過大的放電電流和噪聲,但也允許序列在發出關閉系統的信號后的可接受時間內完成已經收到。

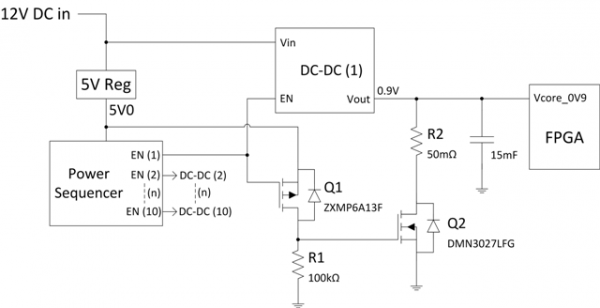

圖 1 的示意圖說明了 Diodes 公司的主動放電設計,該設計使用 N 溝道功率 MOSFET DMN3027LFG (Q2) 作為開關,通過電阻 R2 將去耦電容放電到地,選擇電阻 R2 以實現合適的 RC 時間常數。 R2 的存在還可以防止急劇上升的電流峰值,這可能會導致 EMI 問題以及 N 溝道功率 MOSFET 和電容器組上的瞬態熱應力。

圖 1. 有源電容器放電對于正確的斷電排序至關重要。

在圖 1 中,電源定序器的 EN 輸出連接到 DC-DC 穩壓器的使能引腳,也連接到 P 溝道 MOSFET (Q1) 的柵極。當定序器輸出變為低電平以禁用 DC DC 穩壓器時,Q1 將信號反相,從而打開 Q2 以對電容器放電。放電電路假定 DC-DC 穩壓器一旦施加關斷信號就不能繼續產生輸出。如果在激活關閉命令后 DC-DC 穩壓器的輸出有可用電源,Q2 將嘗試吸收 DC-DC 穩壓器的全部輸出電流能力。必須通過在激活放電電路之前插入延遲來防止這種情況。

關鍵組件選擇

盡管有源放電電路很容易實現,但需要注意選擇正確的電阻器以及 P 溝道和 N 溝道 MOSFET,以最大限度地減少對瞬態和過熱的影響,從而降低可靠性。

MOSFET Q1 的選擇應參考電源排序器的輸出電壓閾值。所選器件應具有足夠高的柵極閾值電壓 (VGS(th)),以確保在定序器輸出較高時保持關閉狀態,記住 VGS(th) 會隨著結溫的升高而下降。本示例選擇的序列發生器采用 5V 電源供電,并具有 4.19V 的最小指定高電平輸出電壓。在 60°C 的環境工作溫度下,Q1 的 VGS(th) 必須大于 0.9V,以確保正常工作。此外,應使用 100kΩ 電阻將柵極下拉至源極電位,以避免誤開啟。檢查 MOSFET 數據表中 VGS(th) 與溫度的歸一化曲線表明 Diodes Incorporated 的ZXMP6A13F滿足要求:保證最小 VGS(th) 在室溫下為 1V,在 +60°C 時降至 0.9V 左右。

出于本示例的目的,我們假設定序器必須在 100 毫秒內關閉總共 10 個電壓軌。因此,每個軌上的去耦電容器組必須在 10 毫秒內放電。以 8ms 的 3x RC 時間常數為目標,可確保電容器在所需時間內放電至低于其全電壓的 5%。要計算 RC 常數,必須考慮電容器組的 MOSFET RDS(ON)、寄生走線電阻和 ESR,以及電阻器 R2。

假設電容 ESR 和走線電阻的總和不大于 10mΩ,去耦組的總電容為 15mF,RDS(ON) 和 R2 的合適值可通過下式計算:

3 x (10mΩ + R2 + (1.5 x RDS(ON))) x 15mF = 8ms

假設 R2 = 50mΩ,功率 MOSFET Q2 在 VGS = 4.5V 和 25°C 環境溫度下的 RDS(ON) 必須小于 80mΩ。

在選擇 MOSFET 時,還應考慮與溫度相關的變化和 RDS(ON) 的批次間變化的影響。在 4.5V 柵極驅動的預期工作溫度范圍內,RDS(ON) 可以變化多達 15mΩ。出于這個原因,最好確保 R2 大約是所選 MOSFET 的制造商指定的最大 RDS(ON) 的兩倍。如果 R2 為 50mΩ,則可以選擇 MOSFET,例如 Diodes Incorporated 的DMN3027LFG N 溝道 MOSFET。該器件在室溫下 VGS = 4.5V 時的典型和最大 RDS(ON) 分別為 22mΩ 和 26.5mΩ。因此,RDS(ON) 可以在大約 15mΩ 到 40mΩ 之間變化,在 3.9 到 5.4ms 之間提供 95% (3x RC) 的放電時間,最壞情況下的電容器組大小為 20mF。

評估安全作業區

因為DMN3027LFG隨著時間的推移,電容器的能量會隨著電流和電壓的變化而消耗,因此有必要評估功率 MOSFET 可以安全處理的最大單脈沖,同時確保結溫不超過絕對最大額定值,典型 TJ(max) = +150°C。這可以通過檢查 MOSFET 數據表中的安全工作區 (SOA) 看出(圖 2)。SOA 應基于應用的環境工作溫度以及所需的 MOSFET 柵極驅動。在對 0.9V 充電電容器組放電的情況下,可接受的 SOA 曲線應表明脈沖寬度在 1ms 和 10ms 之間的單脈沖峰值電流能力至少為 1V。SOA 應適用于典型的應用環境溫度,假設為 +60°C,同時安裝在 PCB 上,具有最小的散熱,

圖 2. DMN3027LFG N 溝道 MOSFET 的 SOA。

還需要考慮DMN3027LFG (Q2) MOSFET 和串聯電阻 R2 的功耗。最壞的情況是由電容器短時間充電和放電引起的。假設在最壞的情況下,電源定序器可以進入一個連續環路,每 20 毫秒啟用和禁用 DC-DC 穩壓器(10 毫秒啟用 + 10 毫秒禁用),DMN3027LFG和 R2將消耗大約 0.5 W。這是通過知道存儲在電容器組中的總能量將每 20 毫秒釋放一次來計算的:

P = E ÷ t = ?CV2 ÷ 20ms = 500mW(假設 C = 20mF 充電至 1V)

由于DMN3027LFG的最大溫度調節 RDS(ON)為 40mΩ,因此 Q2 和 R2 的功耗分別為 222mW 和 278mW。在 15mΩ 的最低 RDS(ON) 時,R2 的功耗將增加到 385mW。因此需要一個 0.5W 額定值的電阻器。

在典型應用中,環境溫度預計會達到 60°C,DMN3027LFG在推薦的最小焊盤布局上的結到環境熱阻 (RθJA) 為 130°C/W,然后在耗散 222mW 時 TJ 達到 90°C。這在 TJ(max) = 150°C 時提供了充足的動態余量。

將計算付諸實踐

出于測試目的,組裝了一個由六個 2,200μF 電解電容器(標稱總量為 13.2mF)和一個有源放電電路組成的電容器組,其中包括 Diodes 公司的ZXMP6A13F P 溝道 MOSFET (Q1) 和DMN3027LFG N 溝道 MOSFET (Q2)如圖1所示。ZXMP6A13F采用5V信號手動觸發。

圖 3. 不使用(左)和使用(右)50mΩ 串聯放電電阻器時記錄的結果。

首先,電容器組僅通過DMN3027LFG放電,以說明添加 50mΩ 電阻器 R2 的效果。圖 3 顯示峰值電流達到約 30A,但由于 MOSFET RDS(ON) 增加,這將在較高溫度下降低。添加 R2 將峰值電流限制在 11A 左右,同時也降低了放電電流的溫度依賴性。通過電路中的電阻,放電到初始 1V 充電狀態的 95% 的時間為 3 到 4ms,接近理論值計算的數字。

結論

在使用從多個電源軌運行的復雜 FPGA 和片上系統設備時,以正確的順序關閉每個 POL 與確保正確的上電順序同樣重要。這對于防止損壞芯片的某些部分是必要的。然而,在斷電時,系統正常運行時必不可少的去耦電容會導致關斷時間變得不可預測。對這些電容器進行主動放電以確保在已知時間內關閉每個電源軌,從而實現正確和安全的關閉。

花時間考慮最壞的情況和對功率 MOSFET 開關等組件的壓力可以通過確保長期可靠性和最大限度地減少對溫度等環境影響的依賴來獲得回報。

-

FPGA

+關注

關注

1645文章

22020瀏覽量

617120 -

MOSFET

+關注

關注

150文章

8496瀏覽量

219699 -

放電電路

+關注

關注

1文章

22瀏覽量

10928

發布評論請先 登錄

有源放電電路的原理和注意事項

有源放電電路的原理和注意事項

評論