皮爾金頓Pilkington是是世界上最大的玻璃生產集團之一。創建于1826年英國St.Helens,已具有195年的歷史,在全球擁有25個生產基地,銷售公司遍布130個國家。賓利、法拉利、奔馳、寶馬等世界級名車均采用皮爾金頓制造的專業擋風玻璃。

那么你知道這個公司曾經做過FPGA嘛...?是的,的確做過,但就像很多巨頭那樣,不是很成功。

這個玻璃公司在上個世紀建立微電子部門準備在FPGA方向上大干一場,而且找到了Toshiba這個大用戶,但最終還是沒能成功,不得不把團隊賣給了Motorola(后者最后也失敗了:))。

Pilkington FPGA架構簡介

皮爾金頓有兩種(已知的)架構,都是基于sea-of-gates設計的,其中邏輯功能是通過將門連接在一起來構建的。上世紀80年代中期,不同的制造商有著非常不同的邏輯單元結構。

第一種架構(無特定名稱)是圍繞一個具有NAND門和鎖存器的邏輯單元設計的,每個邏輯單元通過本地互連進入其相鄰的單元。白皮書指出,這是低效的,因為需要大量的NAND門來實現通用功能,如OR和XOR,以及鎖存器出到DFF造成的布局限制。

第二種架構(白皮書稱它為TS1)。像ABC這樣的邏輯優化程序將邏輯表示為AND門、異或門、多路復用器和D觸發器的結構;并且所有這些都具有輸入可編程反向功能。在上世紀90年代中期,當時的邏輯優化工具仍然使用笨拙的sum-of-product方法時,皮爾金頓已經在硬件上實現了這一點。

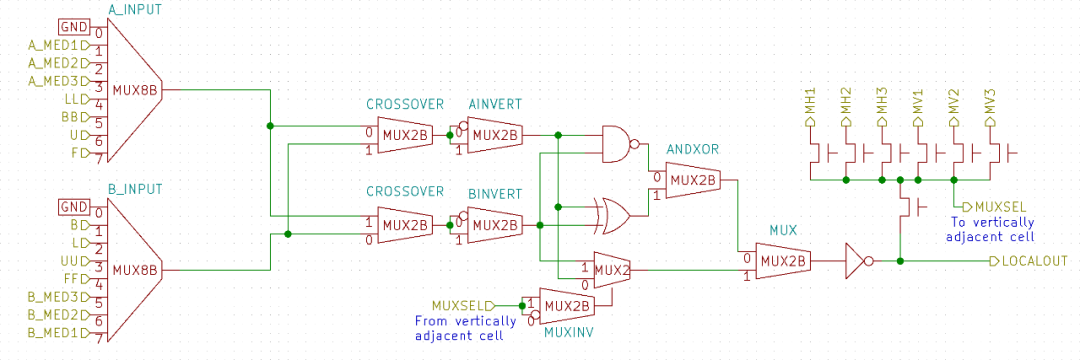

TS1 Logic Cell

邏輯單元本身挺簡單:組合邏輯單元只是從輸入選擇器mux中獲取輸入,可選地反向它們,并將它們饋送到NAND、XOR和MUX的輸入,從它們中選擇輸出,然后反向以放大信號。

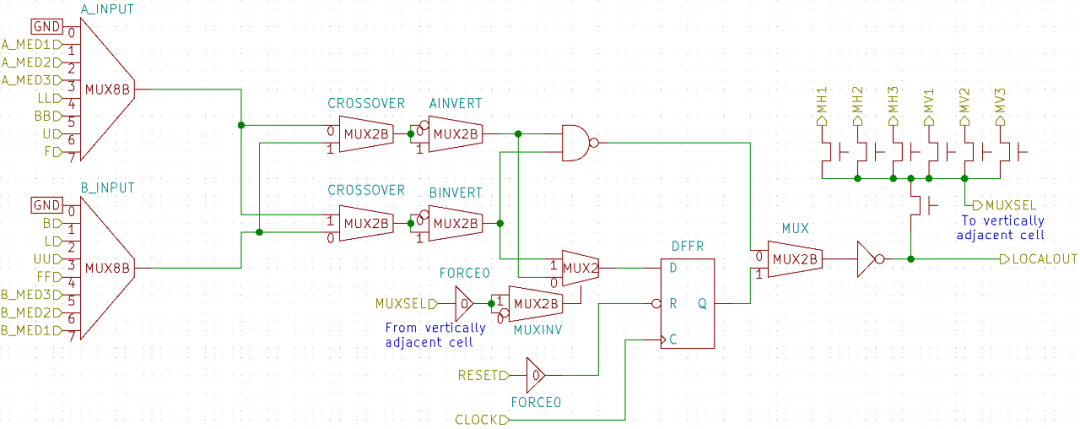

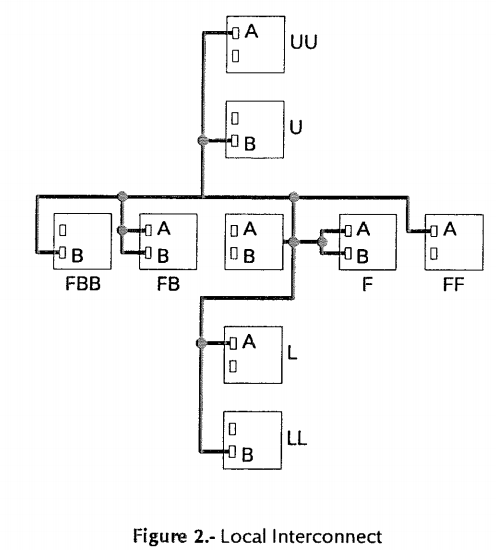

時序邏輯單元沿著相同的路線。邏輯單元的輸出直接連接到“本地互連”:與相鄰信號的A和B輸入選擇器的快速鏈接;它還可以連接到“介質互連”:較慢的水平和垂直互連鏈路(每行/列6個)通過邏輯單元“區域”傳播。

Routing 結構

邏輯單元被分組為一個由3個組合邏輯單元和一個時序邏輯單元組成的正方形tile。這些tile有兩個變體(標記為A和B,只在如何連接到inter-tile互連方面有所不同),tile平鋪在一起形成一個5x5的區域。

每個區域都被端口單元包圍,這些單元與“全局互連”通過接口相連。這種互連方式就是放在現代的標準來看,其全局布線資源也是很精簡的,所以布線工具必須充分利用更多的本地布線資源。設計人員還有另一個訣竅:如果邏輯門足夠快,您可以通過門來路由邏輯,而不會造成太大的性能損失;這就是為什么inter-tile互連的行和列之間沒有直接鏈接-這些鏈接就是邏輯門本身。

與當時的一些邏輯架構(如Actel的多路復用器架構)相比,這種設計還挺優雅。所選擇的門又小又簡單,軟件處理起來相對容易:綜合不是問題,而且將邏輯劃分為區域的目的是通過將邏輯轉換為一個“分而治之”問題來更容易地布局布線,但也許現代算法將其視為一個全局問題也OK。

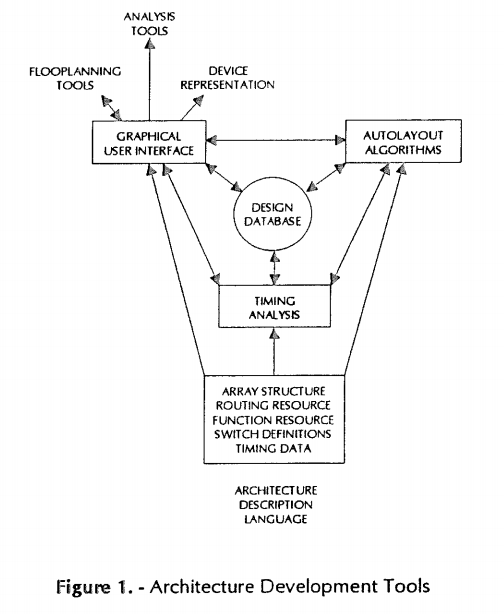

公司還自己搞了一套架構評估工具...看來沒少投入啊...

至于為什么FPGA后來黃了,不得而知。也許架構的實現存在無法修復的錯誤,又或許上世紀90年代的EDA工具無法充分契合芯片的層次結構吧。

審核編輯 :李倩

-

FPGA

+關注

關注

1644文章

22009瀏覽量

616614 -

架構

+關注

關注

1文章

528瀏覽量

25926

原文標題:皮爾金頓的FPGA架構

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

Xilinx Ultrascale系列FPGA的時鐘資源與架構解析

EM儲能網關 ZWS智慧儲能云應用(11) — 一級架構 主從架構

MRAM存儲替代閃存,FPGA升級新技術

FPGA+GPU+CPU國產化人工智能平臺

Verilog vhdl fpga

詳解FPGA的基本結構

FPGA芯片架構和資源有深入的理解,精通Verilog HDL、VHDL

【招聘】verilog vhdl FPGA

ALINX FPGA+GPU異架構視頻圖像處理開發平臺介紹

自動駕駛三大主流芯片架構分析

Pilkington FPGA架構簡介

Pilkington FPGA架構簡介

評論