楷登電子(美國(guó) Cadence 公司,NASDAQ:CDNS)今日宣布,其面向 TSMC N7、N6 和 N5 工藝技術(shù) PCI Express?(PCIe?) 5.0 規(guī)范的 PHY 和控制器 IP 在 4 月舉行的業(yè)界首次 PCIe 5.0 規(guī)范合規(guī)認(rèn)證活動(dòng)中通過了 PCI-SIG? 的認(rèn)證測(cè)試。Cadence? 解決方案經(jīng)過充分測(cè)試,符合 PCIe 5.0 技術(shù)的 32GT/s 全速要求。該合規(guī)計(jì)劃為設(shè)計(jì)者提供測(cè)試程序,用以評(píng)估系統(tǒng)級(jí)芯片(SoC)設(shè)計(jì)的 PCIe 5.0 接口是否會(huì)按預(yù)期運(yùn)行。

面向 PCIe 5.0 技術(shù)的 Cadence IP 包括 PHY、配套控制器和驗(yàn)證 IP(VIP),主要用于高帶寬超大規(guī)模計(jì)算、網(wǎng)絡(luò)和存儲(chǔ)應(yīng)用的系統(tǒng)級(jí)芯片設(shè)計(jì)。利用 Cadence 針對(duì) PCIe 5.0 架構(gòu)的 PHY 和控制器子系統(tǒng),客戶可以設(shè)計(jì)出功耗極低的系統(tǒng)級(jí)芯片,并加快產(chǎn)品上市速度。

“我們很高興看到 Cadence 面向 TSMC 先進(jìn)工藝的全系列 IP 產(chǎn)品實(shí)現(xiàn) PCIe 5.0 協(xié)議合規(guī)性。”TSMC 設(shè)計(jì)基礎(chǔ)設(shè)施管理部副總裁 Suk Lee 表示,“我們與 Cadence 的持續(xù)密切合作將幫助雙方客戶滿足嚴(yán)格的功耗和性能要求,并借助基于 TSMC 先進(jìn)技術(shù)帶來的領(lǐng)先設(shè)計(jì)解決方案來加速芯片創(chuàng)新。”

“憑借經(jīng)過客戶驗(yàn)證的最低功耗,符合 PCIe 5.0 規(guī)范的 Cadence PHY 和控制器 IP 使客戶能夠開發(fā)出極其節(jié)能的系統(tǒng)級(jí)芯片。”Cadence 公司全球副總裁兼 IP 部總經(jīng)理 Sanjive Agarwala 表示,“通過我們的多通道片上子系統(tǒng)解決方案,我們的客戶可以看到在與其目標(biāo)應(yīng)用相匹配的外形尺寸中實(shí)現(xiàn)了 IP 合規(guī)性。”

“面向 PCIe 5.0 規(guī)范的 Cadence PHY 和控制器測(cè)試芯片在 Xgig 訓(xùn)練器和分析儀平臺(tái)上進(jìn)行的合規(guī)性測(cè)試中表現(xiàn)出色,與之前進(jìn)行的測(cè)試結(jié)果一致。”VIAVI Solutions 實(shí)驗(yàn)室和產(chǎn)品業(yè)務(wù)部高級(jí)副總裁兼總經(jīng)理 Tom Fawcett 表示,“Cadence 在高帶寬超大規(guī)模 SoC IP 方面處于領(lǐng)先地位,他們?cè)?PCI-SIG 合規(guī)活動(dòng)中的成功記錄表明他們對(duì)其解決方案和整個(gè)技術(shù)的持續(xù)信心。”

“英特爾致力于通過開放的 PCI Express 標(biāo)準(zhǔn)進(jìn)行全行業(yè)創(chuàng)新和嚴(yán)格的兼容性測(cè)試。”英特爾公司技術(shù)計(jì)劃總監(jiān) Jim Pappas 表示,“Cadence 最新的 PHY 和控制器 IP 展示了他們對(duì) PCIe 5.0 性能和與我們第 12 代英特爾酷睿和第 4 代英特爾至強(qiáng)可擴(kuò)展平臺(tái)互操作性的承諾。”

“作為 PCI-SIG 的長(zhǎng)期成員,Cadence 為 PCIe 技術(shù)的發(fā)展作出了很大的貢獻(xiàn)。”PCI-SIG 主席 Al Yanes 表示,“Cadence 積極參與該合規(guī)計(jì)劃,幫助推動(dòng) PCIe 架構(gòu)的不斷普及。”

面向 PCIe 5.0 架構(gòu)的 Cadence IP 支持 Cadence 的智能系統(tǒng)設(shè)計(jì)(Intelligent System Design? )策略,助力實(shí)現(xiàn)卓越的先進(jìn)節(jié)點(diǎn)系統(tǒng)級(jí)芯片設(shè)計(jì)。面向 TSMC N7、N6 和 N5 工藝技術(shù)的 PCIe 5.0 設(shè)計(jì)套件現(xiàn)已可供授權(quán)和交付。面向 TSMC 先進(jìn)工藝的 Cadence 全系列設(shè)計(jì) IP 解決方案還包括 112G、56G、裸片到裸片(D2D)以及先進(jìn)存儲(chǔ)器 IP 解決方案。

-

芯片

+關(guān)注

關(guān)注

459文章

52360瀏覽量

438839 -

控制器

+關(guān)注

關(guān)注

114文章

17054瀏覽量

183598 -

Cadence

+關(guān)注

關(guān)注

67文章

968瀏覽量

144112

發(fā)布評(píng)論請(qǐng)先 登錄

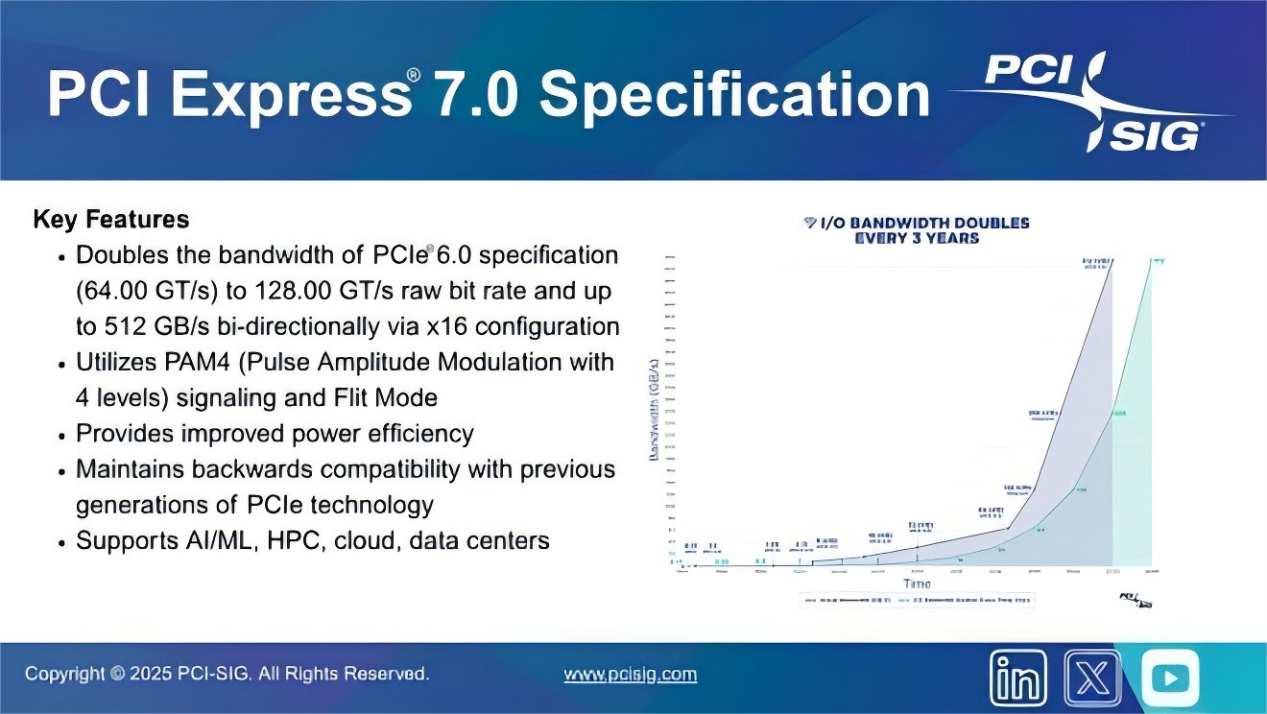

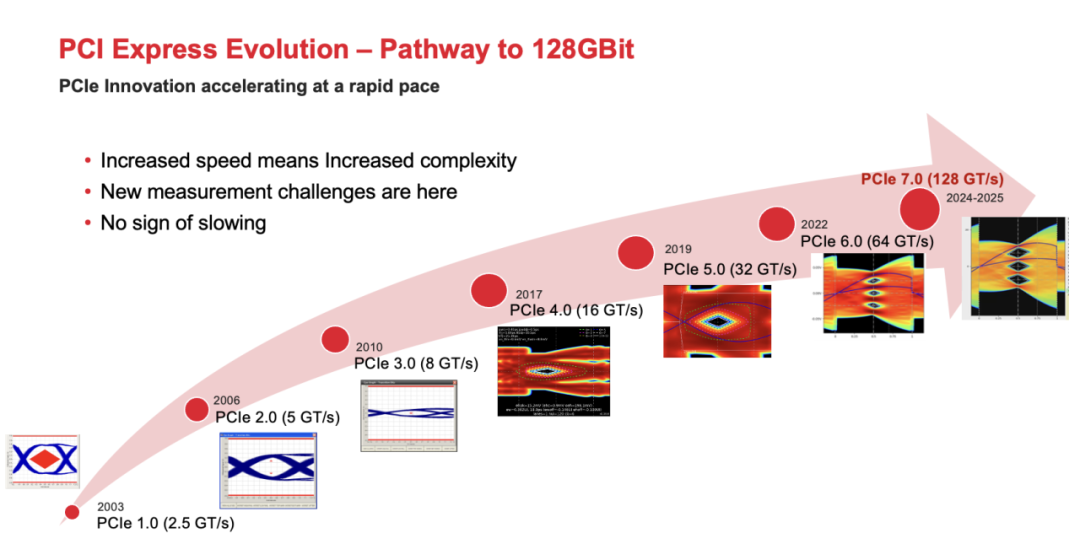

PCIe 7.0發(fā)布:16通道雙向512GB/s,擁抱光纖未來

PCIe 5.0市場(chǎng)加速滲透,PCIe 6.0研發(fā)到來

nvme IP開發(fā)之PCIe下

PCIe 7.0最終版草案發(fā)布,傳輸速率128 GT/s,PCIe 6.0加速商業(yè)化

是德科技PCIe 6.0發(fā)射機(jī)合規(guī)性測(cè)試解決方案

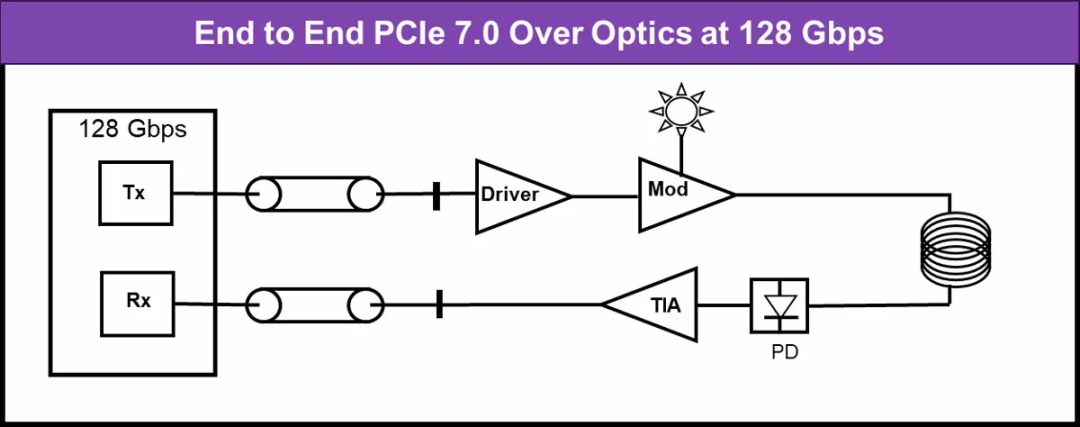

PCIe 7.0 互連— PCIe的盡頭會(huì)是光嗎?

pcie 4.0與pcie 5.0的區(qū)別

是德科技PCIe 7.0測(cè)試解決方案

PCIe接口的工作原理 PCIe與PCI的區(qū)別

CC256x藍(lán)牙SIG認(rèn)證應(yīng)用說明

Cadence展示完整的PCIe 7.0 IP解決方案

PCIe 5.0 SerDes 測(cè)試

PCIe光傳輸?shù)膬?yōu)勢(shì)與挑戰(zhàn)

Cadence PCIe 5.0技術(shù)通過PCI-SIG?認(rèn)證測(cè)試

Cadence PCIe 5.0技術(shù)通過PCI-SIG?認(rèn)證測(cè)試

評(píng)論