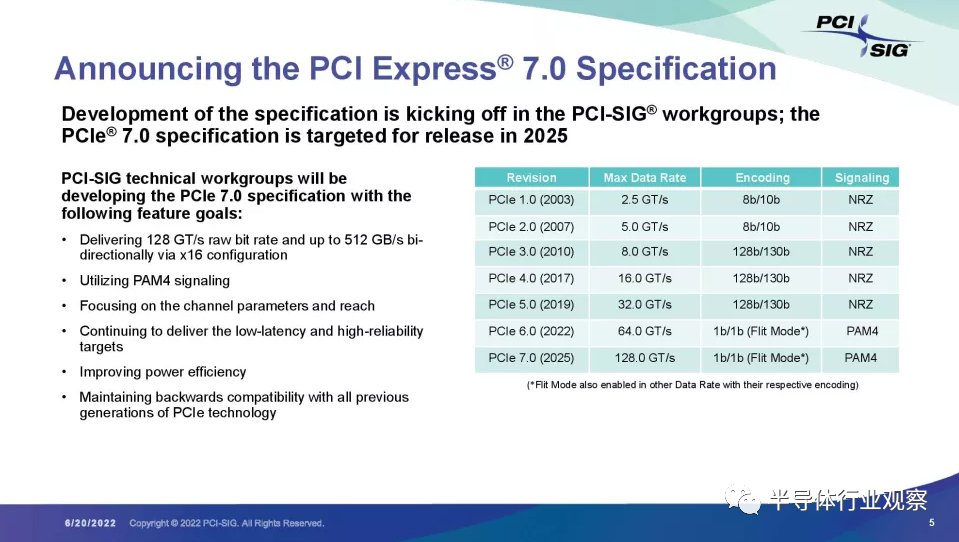

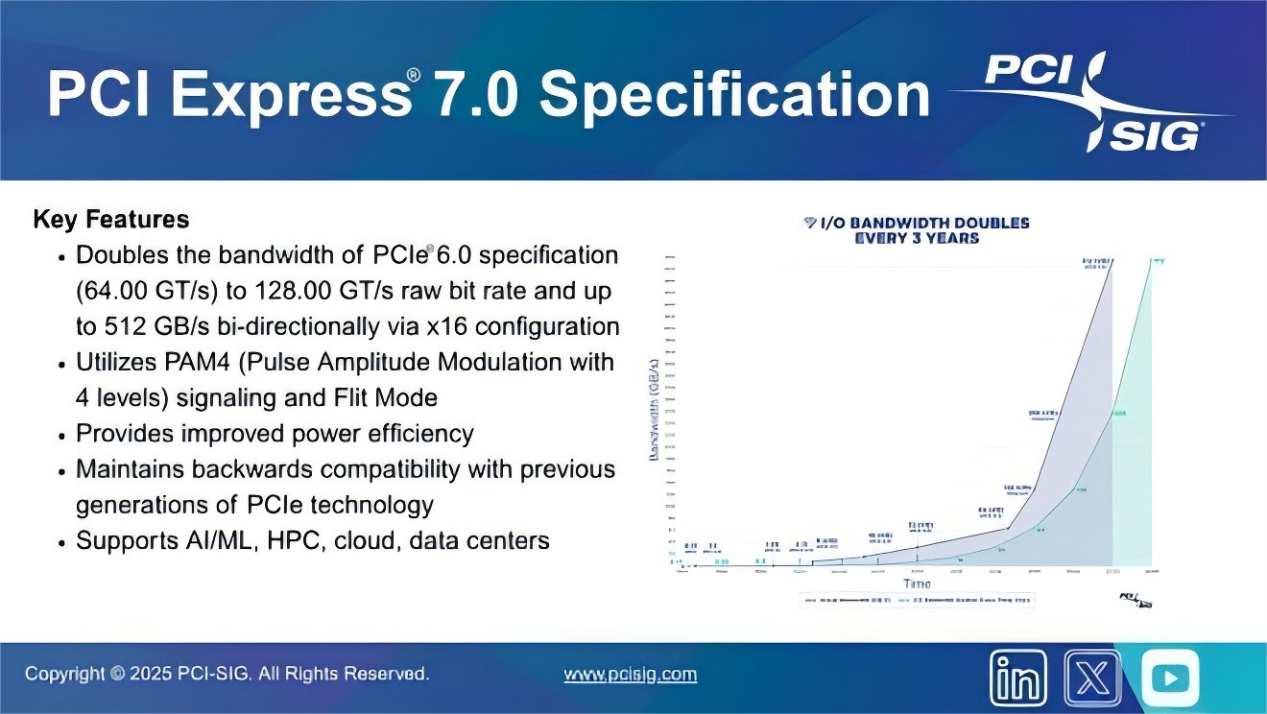

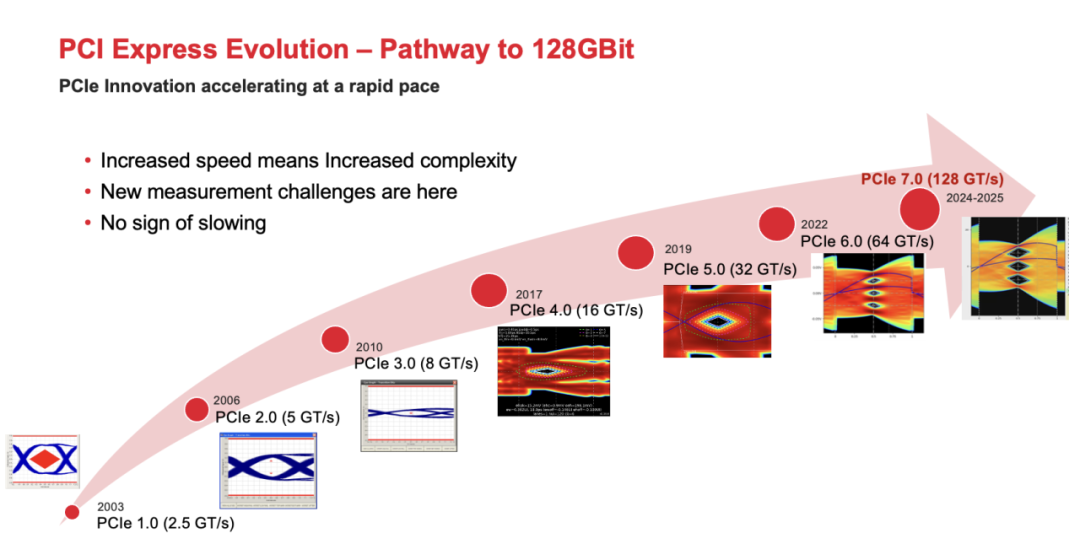

2022 年 PCI-SIG 開(kāi)發(fā)者大會(huì)正在如火如荼舉行,而藏在無(wú)處不在的 PCIe 接口標(biāo)準(zhǔn)背后的標(biāo)準(zhǔn)委員會(huì)PCI-SIG 宣布,PCIe 7.0 規(guī)范的目標(biāo)是在 2025 年向其成員發(fā)布,數(shù)據(jù)速率高達(dá) 128 GT/s。在編碼開(kāi)銷(xiāo)之前,這相當(dāng)于通過(guò) 16 通道 (x16) 連接實(shí)現(xiàn) 512 GB/s 的雙向吞吐量。PCI-SIG 是 PCIe 接口背后的聯(lián)盟,這是一個(gè)由 900 多家成員公司組成的開(kāi)放行業(yè)標(biāo)準(zhǔn)。

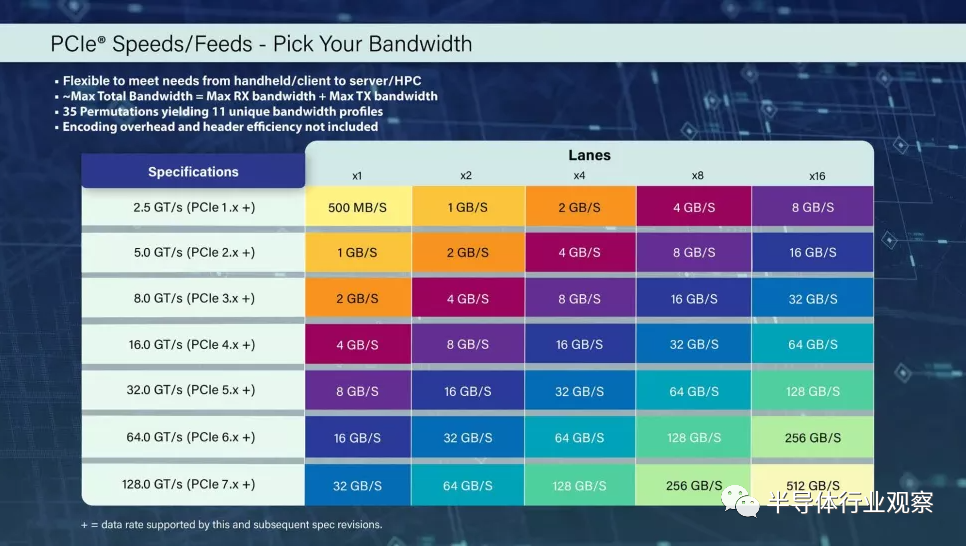

PCI-SIG 指出,PCIe 7.0 接口將通過(guò) x16 連接提供高達(dá) 512 GB/s 的雙向吞吐量,但這是在編碼開(kāi)銷(xiāo)(encoding overhead )和標(biāo)頭效率(header efficiency)的影響之前,這兩者都會(huì)影響可用帶寬。 PCIe 7.0 接口將繼續(xù)使用 1b/1b flit 模式編碼和隨 PCIe 6.0 引入的 PAM4 信號(hào)技術(shù),這與PCIe 3.0 到PCIe 5.0 規(guī)范中使用的 128b/130b 編碼和 NRZ 信號(hào)相比有顯著改進(jìn)。因此,實(shí)際可用帶寬將略低于 512 GB/s 的數(shù)字,但仍代表 PCIe 6.0 接口的兩倍。 正如我們?cè)谔D(zhuǎn)到 PCIe 4.0 和 5.0 時(shí)看到的那樣,由于更快的信號(hào)傳輸速率,PCIe 走線(xiàn)的長(zhǎng)度將再次縮短。這意味著在沒(méi)有額外組件的情況下,PCIe 根設(shè)備(如 CPU)和終端設(shè)備(如 GPU)之間的最小允許距離將縮短。因此,與我們?cè)谇皫状涌谥锌吹降南啾龋靼鍖⑿枰嗟闹?a href="http://m.xsypw.cn/tags/定時(shí)器/" target="_blank">定時(shí)器(retimers )和由更高質(zhì)量材料組成的更厚 PCB,而 PCIe 7.0 支持將導(dǎo)致主板價(jià)格再次上漲。 值得注意的是,每條通道的帶寬將更高,現(xiàn)在對(duì)于 x1 連接的雙向帶寬為 32 GB/s,可以允許某些設(shè)備的“更細(xì)”連接(例如,使用 x4 而不是 x8 連接)。

PCIe 7.0 規(guī)范的基礎(chǔ)工作是在PCI-SIG 今年早些時(shí)候完成 PCIe 6.0 規(guī)范之后制定的,它將提供比上一代 PCIe 6.0 接口增加一倍的帶寬。然而,我們還需要一段時(shí)間才能看到支持這種快速接口的 SSD 和 GPU 等設(shè)備——這些規(guī)范通常在我們看到出貨硅片之前很久就得到批準(zhǔn)和最終確定。 您會(huì)注意到,市場(chǎng)上仍然沒(méi)有多少PCIe 5.0設(shè)備,盡管該接口確實(shí)出現(xiàn)在英特爾Alder Lake的主流主板上,并且還將出現(xiàn)在 AMD 即將推出的 Zen 4 Ryzen 7000上今年晚些時(shí)候到貨的平臺(tái)。首批 PCIe 5.0 SSD 將與 Ryzen 7000 處理器同時(shí)上市,但我們已經(jīng)看到了用于數(shù)據(jù)中心和 AI/ML 設(shè)備的 PCIe 5.0 設(shè)備的產(chǎn)品公告。 換句話(huà)說(shuō),您在相當(dāng)長(zhǎng)的一段時(shí)間內(nèi)都不會(huì)在市場(chǎng)上看到 PCIe 7.0 設(shè)備,盡管 PCI-SIG 現(xiàn)在開(kāi)始定義規(guī)范并希望實(shí)現(xiàn)其每三年發(fā)布一個(gè)新規(guī)范的目標(biāo)。PCIe 7.0 規(guī)范預(yù)計(jì)將在 2025 年落地,但我們要到 2028 年才能看到終端設(shè)備。

PCIe 7.0 規(guī)范目標(biāo):

通過(guò) x16 配置提供 128 GT/s 的原始比特率和高達(dá) 512 GB/s 的雙向傳輸速率

利用 PAM4(4 級(jí)脈沖幅度調(diào)制)信令

關(guān)注渠道參數(shù)和覆蓋范圍

繼續(xù)提供低延遲和高可靠性的目標(biāo)

提高電源效率

保持與所有前幾代 PCIe 技術(shù)的向后兼容性

符號(hào)列表

“30 年來(lái),PCI-SIG 的指導(dǎo)原則一直是,‘如果我們建造它,他們就會(huì)來(lái),’”Insight 64 研究員 Nathan Brookwood 說(shuō)。“PCI 技術(shù)的早期并行版本可容納數(shù)百兆字節(jié)/其次,與 1990 年代的圖形、存儲(chǔ)和網(wǎng)絡(luò)需求相匹配。2003 年,PCI-SIG 演變?yōu)橹С智д鬃止?jié)/秒速度的串行設(shè)計(jì),以適應(yīng)更快的固態(tài)磁盤(pán)和 100MbE 以太網(wǎng)。幾乎就像發(fā)條一樣,PCI-SIG 每三年將 PCIe 規(guī)范帶寬翻一番,以應(yīng)對(duì)新興應(yīng)用和市場(chǎng)的挑戰(zhàn)。今天宣布的 PCI-SIG 計(jì)劃將通道速度翻倍至 512 GB/s(雙向)使其有望在另一個(gè) 3 年周期內(nèi)將 PCIe 規(guī)范性能翻一番。”他進(jìn)一步指出。 “隨著即將推出的 PCIe 7.0 規(guī)范,PCI-SIG 繼續(xù)我們 30 年來(lái)的承諾,即提供推動(dòng)創(chuàng)新邊界的行業(yè)領(lǐng)先規(guī)范,”P(pán)CI-SIG 總裁兼主席 Al Yanes 說(shuō)。“隨著 PCIe 技術(shù)不斷發(fā)展以滿(mǎn)足高帶寬需求,我們工作組的重點(diǎn)將放在通道參數(shù)和覆蓋范圍以及提高功率效率上。”Al Yanes 接著說(shuō)。 PCIe 7.0 規(guī)范旨在支持新興應(yīng)用,例如 800 G 以太網(wǎng)、AI/ML、云和量子計(jì)算;和數(shù)據(jù)密集型市場(chǎng),如超大規(guī)模數(shù)據(jù)中心、高性能計(jì)算 (HPC) 和軍事/航空航天。

審核編輯 :李倩

-

pcb

+關(guān)注

關(guān)注

4357文章

23438瀏覽量

407180 -

接口

+關(guān)注

關(guān)注

33文章

8961瀏覽量

153288 -

PCIe

+關(guān)注

關(guān)注

16文章

1328瀏覽量

84754

原文標(biāo)題:PCIe 7.0發(fā)布,速度高達(dá)512 GB/s

文章出處:【微信號(hào):架構(gòu)師技術(shù)聯(lián)盟,微信公眾號(hào):架構(gòu)師技術(shù)聯(lián)盟】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

PCIe 7.0發(fā)布:16通道雙向512GB/s,擁抱光纖未來(lái)

PCIe 7.0最終版草案發(fā)布,傳輸速率128 GT/s,PCIe 6.0加速商業(yè)化

PCIe 7.0 互連— PCIe的盡頭會(huì)是光嗎?

突破存儲(chǔ)形態(tài)與邊界!佰維全新Mini SSD震撼發(fā)布,引領(lǐng)端側(cè)智能時(shí)代存儲(chǔ)新范式!

致態(tài)發(fā)布首款PCIe 5.0旗艦產(chǎn)品TiPro9000:順序讀取速度14000MB/s

銀翼新境 致態(tài)TiPro9000引領(lǐng)個(gè)人存儲(chǔ)PCIe 5.0新時(shí)代

PCIe 4.0與3.0的區(qū)別 PCIe設(shè)備的故障排除方法

如何測(cè)試PCIe插槽的速度

Cadence展示完整的PCIe 7.0 IP解決方案

新思科技PCIe 7.0驗(yàn)證IP(VIP)的特性

PCIe 7.0發(fā)布,速度高達(dá)512 GB/s

PCIe 7.0發(fā)布,速度高達(dá)512 GB/s

評(píng)論