通過使用Achronix Speedster7t FPGA中的機器學習加速器MLP72,開發人員可以輕松選擇浮點/定點格式和多種位寬,或快速應用塊浮點,并通過內部級聯可以達到理想性能。

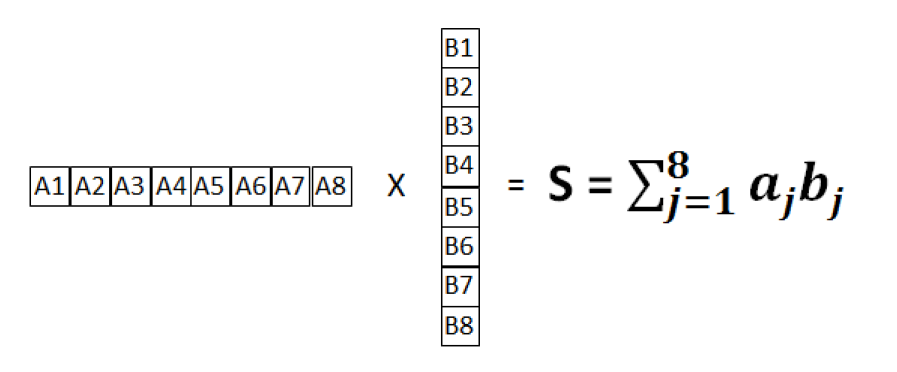

神經網絡架構中的核心之一就是卷積層,卷積的最基本操作就是點積。向量乘法的結果是向量的每個元素的總和相乘在一起,通常稱之為點積。此向量乘法如下所示:

圖1點積操作

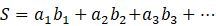

該總和S由每個矢量元素的總和相乘而成,因此

?本文講述的是使用FP16格式的點積運算實例,展示了MLP72支持的數字類型和乘數的范圍。

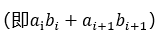

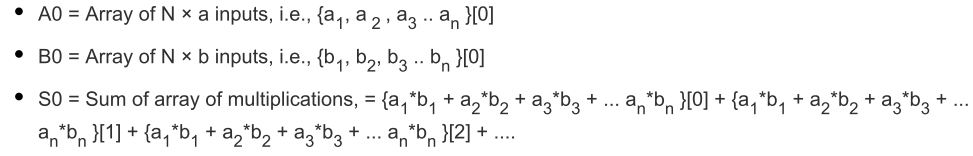

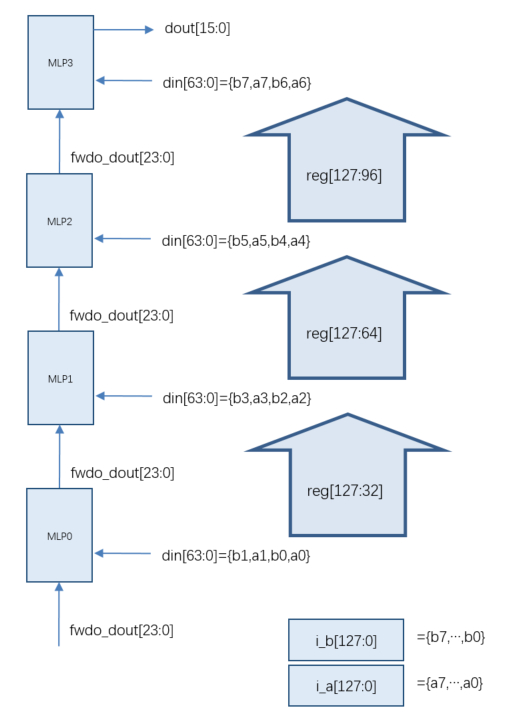

此設計實現了同時處理8對FP16輸入的點積。該設計包含四個MLP72,使用MLP內部的級聯路徑連接。每個MLP72將兩個并行乘法的結果相加

?本文講述的是使用FP16格式的點積運算實例,展示了MLP72支持的數字類型和乘數的范圍。

此設計實現了同時處理8對FP16輸入的點積。該設計包含四個MLP72,使用MLP內部的級聯路徑連接。每個MLP72將兩個并行乘法的結果相加 ,每個乘法都是i_a輸入乘以i_b輸入(均為FP16格式)的結果。來自每個MLP72的總和沿著MLP72的列級聯到上面的下一個MLP72塊。在最后一個MLP72中,在每個周期上,計算八個并行FP16乘法的總和。

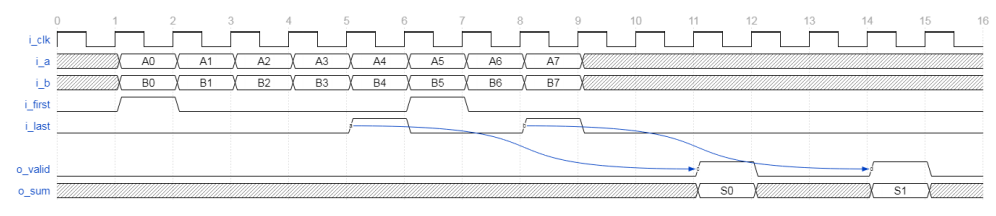

最終結果是多個輸入周期內的累加總和,其中累加由i_first和i_last輸入控制。i_first輸入信號指示累加和歸零的第一組輸入。i_last信號指示要累加和加到累加的最后一組輸入。最終的i_last值可在之后的六個周期使用,并使用i_last o_valid進行限定。兩次運算之間可以無空拍。

,每個乘法都是i_a輸入乘以i_b輸入(均為FP16格式)的結果。來自每個MLP72的總和沿著MLP72的列級聯到上面的下一個MLP72塊。在最后一個MLP72中,在每個周期上,計算八個并行FP16乘法的總和。

最終結果是多個輸入周期內的累加總和,其中累加由i_first和i_last輸入控制。i_first輸入信號指示累加和歸零的第一組輸入。i_last信號指示要累加和加到累加的最后一組輸入。最終的i_last值可在之后的六個周期使用,并使用i_last o_valid進行限定。兩次運算之間可以無空拍。

- 配置說明

表1 FP16點積配置表

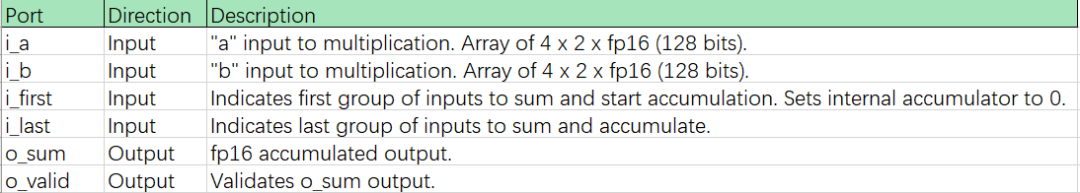

- 端口說明

表2 FP16點積端口說明表

- 時序圖

圖2 FP16點積時序圖

其中,

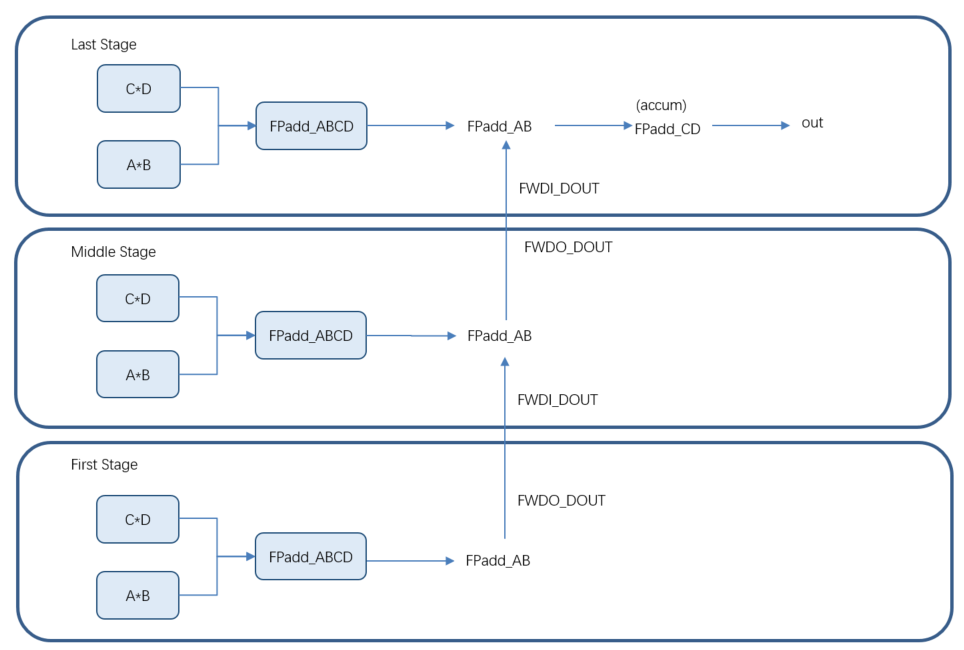

?那么,以上運算功能如何對應到MLP內部呢?其后的細節已分為MLP72中的多個功能階段進行說明。

?那么,以上運算功能如何對應到MLP內部呢?其后的細節已分為MLP72中的多個功能階段進行說明。

- 進位鏈

圖3 MLP進位鏈

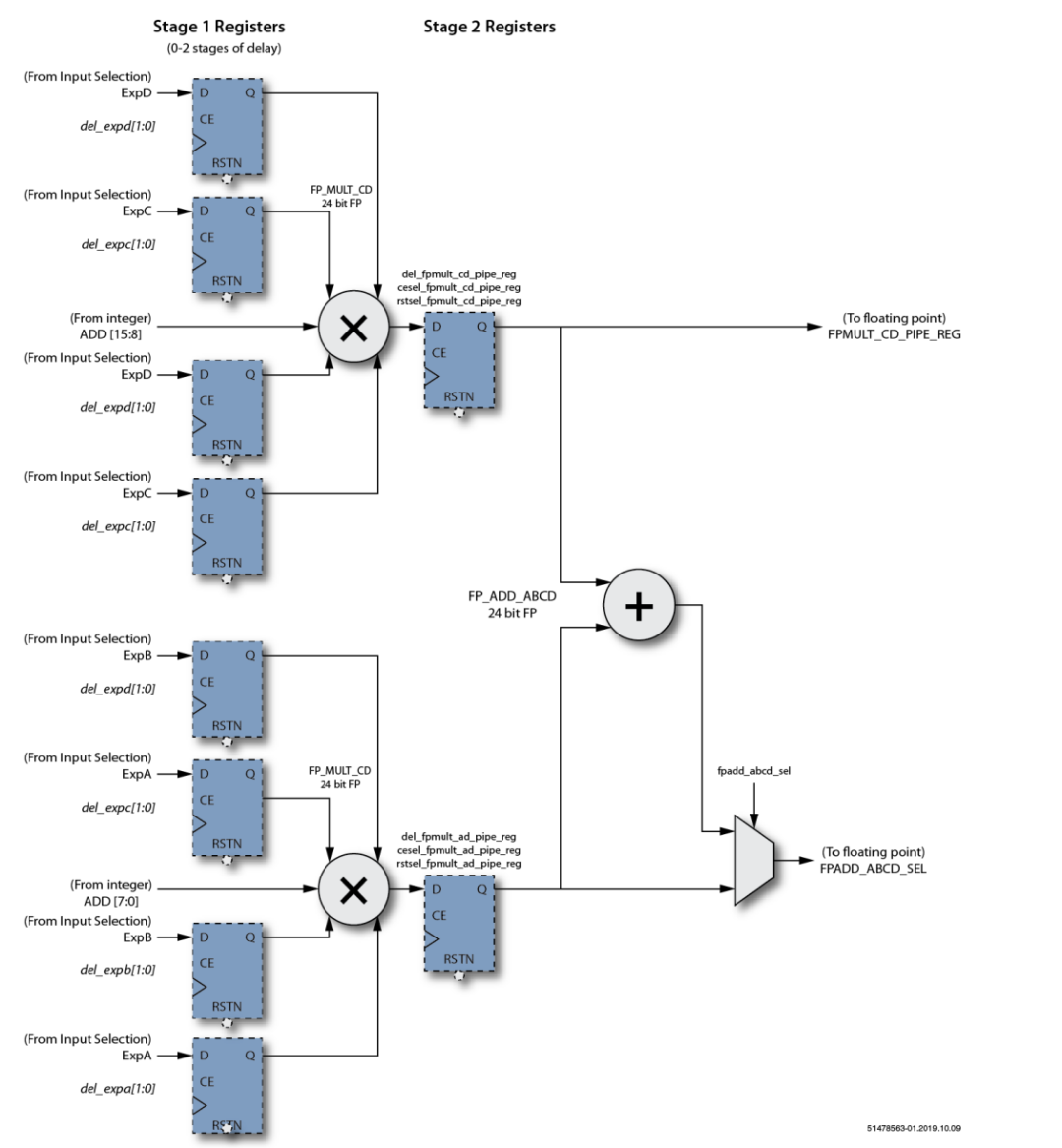

- 乘法階段

圖4 MLP乘法功能階段框圖

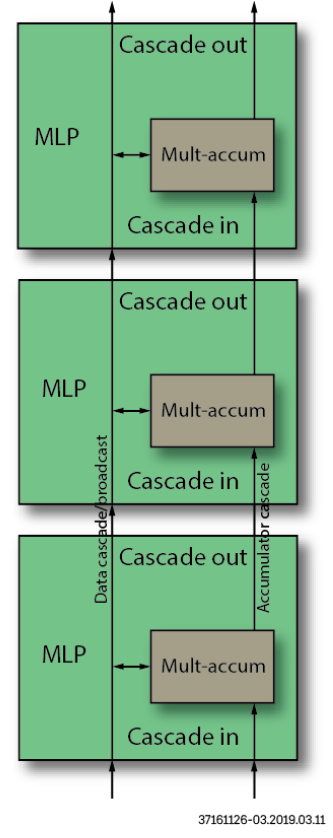

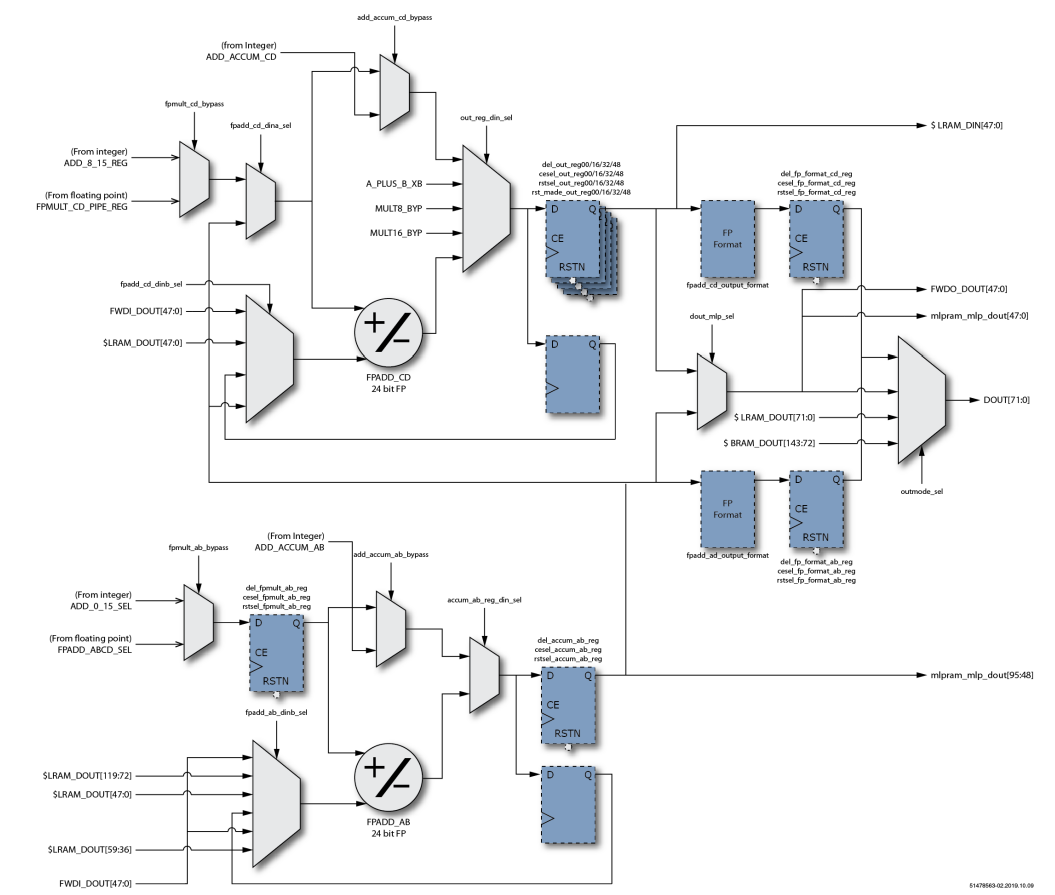

MLP72浮點乘法級包括兩個24位全浮點乘法器和一個24位全浮點加法器。兩個乘法器執行A×B和C×D的并行計算。加法器將兩個結果相加得到A×B + C×D。 乘法階段有兩個輸出。下半部分輸出可以在A×B或(A×B + C×D)之間選擇。上半部分輸出始終為C×D。 乘法器和加法器使用的數字格式由字節選擇參數以及和參數設置的格式確定。 浮點輸出具有與整數輸出級相同的路徑和結構。MLP72可以配置為在特定階段選擇整數或等效浮點輸入。輸出支持兩個24位全浮點加法器,可以對其進行加法或累加配置。進一步可以加載加法器(開始累加),可以將其設置為減法,并支持可選的舍入模式。 最終輸出階段支持將浮點輸出格式化為MLP72支持的三種浮點格式中的任何一種。此功能使MLP72可以外部支持大小一致的浮點輸入和輸出(例如fp16或bfloat16),而在內部以fp24執行所有計算。

圖5 MLP浮點輸出階段框圖

需要強調的是本設計輸入和輸出都是FP16格式,中間計算過程,即進位鏈上的fwdo_out和fwdi_dout 都是FP24格式。具體邏輯框圖如下所示:

圖6 FP16點積邏輯框圖

MLP內部數據流示意圖:

圖7 FP16點積在MLP內部數據流圖

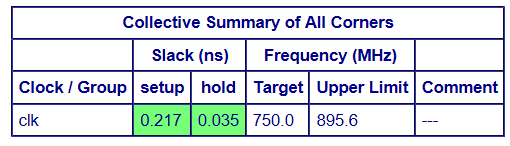

最終ACE的時序結果如下:

審核編輯 :李倩

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

FPGA

+關注

關注

1645文章

22050瀏覽量

618647 -

機器學習

+關注

關注

66文章

8503瀏覽量

134642 -

MLP

+關注

關注

0文章

57瀏覽量

4623

原文標題:詳解FPGA如何實現FP16格式點積級聯運算

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

熱點推薦

計算精度對比:FP64、FP32、FP16、TF32、BF16、int8

本文轉自:河北人工智能計算中心在當今快速發展的人工智能領域,算力成為決定模型訓練與推理速度的關鍵因素之一。為了提高計算效率,不同精度的數據類型應運而生,包括FP64、FP32、FP16、TF32

將Whisper大型v3 fp32模型轉換為較低精度后,推理時間增加,怎么解決?

將 openai/whisper-large-v3 FP32 模型轉換為 FP16、INT8 和 INT4。

推理所花費的時間比在 FP32 上花費的時間要多

發表于 06-24 06:23

RGB888格式的image怎么保存jpg格式?

01的K230板子 1.2.2固件

我用RGB565可以順利保存jpg,但是RGB888就不行,提示如下

提問:RGB888格式的image怎么保存jpg格式

想保存888是因為感覺圖像質量更好,后面用這些保存的圖片來訓練模型

試試這個

發表于 04-25 08:18

Optimum Intel / NNCF在重量壓縮中選擇FP16模型的原因?

無法確定使用 Optimum Intel / NNCF 在重量壓縮中選擇 FP16 模型的原因。

發表于 03-06 06:04

使用模型優化器命令將ONNX模型轉換為OpenVINO? IR格式時出現“ReplacementID”錯誤怎么解決?

, 3], [1,512, 896, 4]

--input frame, prob

--data_type FP16

--output_dir \"{model_path.parent

發表于 03-05 09:41

為什么無法將TensorFlow自定義模型轉換為IR格式?

將 TensorFlow* 自定義模型轉換為 IR 格式: mo --data_type FP16 --saved_model_dir--input_shape (1,150,150,3

發表于 03-05 07:26

為什么無法使用Dla_compiler在OpenVINO?中編譯用于FPGA的IR模型?

/dlia_plugin.cpp:141 FPGA plugin supports only FP16 and FP32 output precision.

發表于 03-05 06:00

THS8200輸出1080P50/60格式YPbPr視頻時無信號是怎么回事?

輸入是16位YCbCr 4:2:2格式的信號,EAV/SAV同步,所有I2C配置按照參考腳本slec026a和slec026b的相關內容來設置的。

現在如果輸入格式是1080P25和P30時,可以

發表于 01-22 07:05

TVP5150AM1工作在601格式時,H、V沒有輸出是怎么回事?

在通道A輸入CVBS信號,配置為656格式,工作完全正常。

配置為601格式,

i2c_write_char(VideoDecoderADDR,0x03

發表于 01-06 06:47

MOV格式與MP4格式的區別

MOV格式與MP4格式在多個方面存在顯著的區別。以下是對這兩種視頻格式的比較: 一、開發背景與用途 MOV格式 : 開發背景:MOV格式是A

中交興路多式聯運可視與協同平臺賦能提升物流管控效率

聯運已成為我國供應鏈體系的關鍵組成部分,也是物流產業科技創新發展的重要領域。 三大堵點 制約多式聯運規模化普及 多式

FPGA中的浮點四則運算是什么

由于定點的四則運算比較簡單,如加減法只要注意符號擴展,小數點對齊等問題即可。在本文中,運用在前一節中描述的自定義浮點格式FPGA中數的表示方法(下),完成浮點四則運算的

FPGA中浮點四則運算的實現過程

由于定點的四則運算比較簡單,如加減法只要注意符號擴展,小數點對齊等問題即可。在本文中,運用在前一節中描述的自定義浮點格式FPGA中數的表示方法(下),完成浮點四則運算的

FPGA如何實現FP16格式點積級聯運算

FPGA如何實現FP16格式點積級聯運算

評論